IDF: Xeon MP „Tulsa“ mit 16 MB Cache

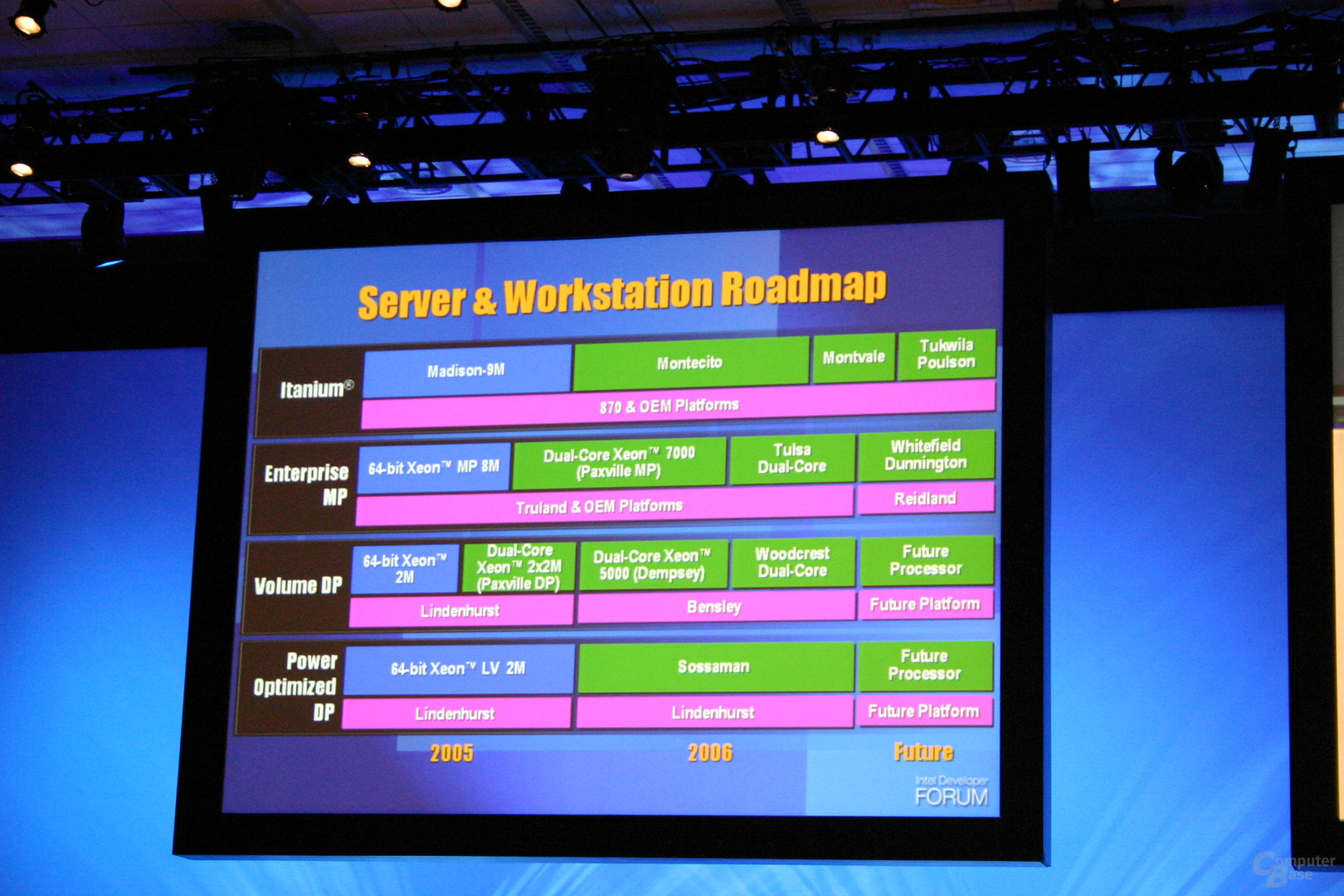

Während Intel mit dem Montecito im Itanium-Segment einen Prozessor mit bis zu 24 MB-L3-Cache kurz vor der Markteinführung steht, ist bei den Xeon MP-Servern mit dem Single-Core „Potomac“ mit 8 MB L3-Cache derzeit die Obergrenze erreicht.

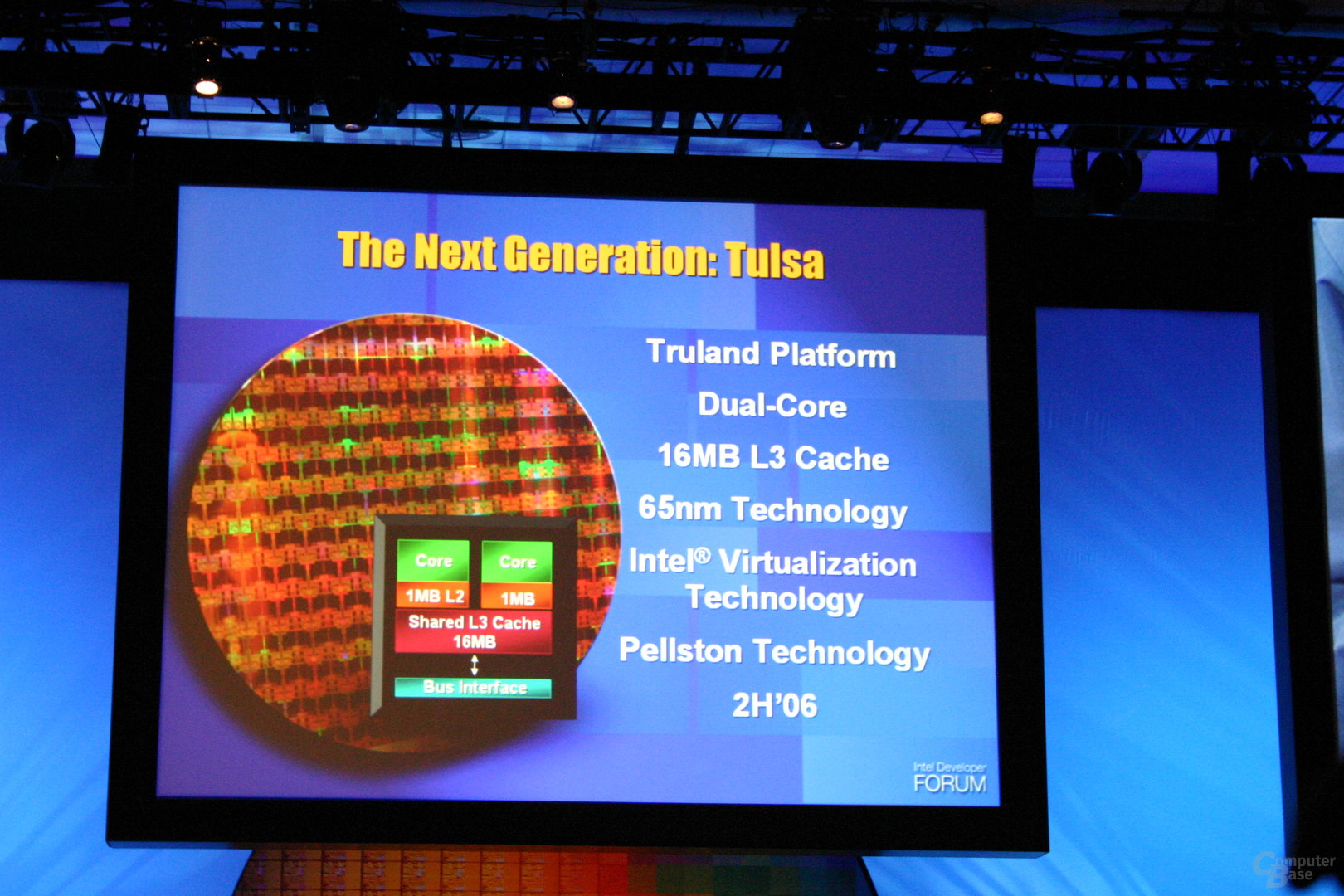

Mit dem kommenden Dual-Core-Prozessor „Tulsa“ möchte Intel der Xeon MP-Plattform nun insgesamt 18 MB L3-Cache zur Seite stellen, wobei Truland samt E8500-Chipsatz (Twin Castle) und damit Sockel 604 nach wie vor als Plattform-Basis dienen wird.

Wie der Paxville MP wird auch Tulsa noch auf der aktuellen Netburst-Architektur basieren. Erst mit dessen Nachfolger Whitefield – ein Quad-Core-Chip – wird sich das ändern. Whitefield wird dabei als Teil der Common Platform Architecture möglicherweise mit einem integrierten Speichercontroller oder einem seriellen Frontside-Bus (CSI - Common Serial Interface) daher kommen. Doch auch mit Tulsa wird es neue Features geben. Die Pellston-Technologie, die erstmals im Dual-Core-Itanium 2 Montecito zum Einsatz kommen wird, ist auch im Tulsa präsent und soll dort dafür sorgen, dass defekte Cache-Lines automatisch deaktiviert werden. Wie wir im Rahmen des IDF in Erfahrung bringen konnten, könnte auch Foxton, ein weiteres Feature des Montecito, im Tulsa vorhanden sein.