VIA enthüllt neue x86-Architektur „Isaiah“

VIA Technologies verkündete gestern erste Details der „VIA Isaiah Architektur“, einer neuen x86-Architektur, die signifikante Steigerungen in Funktionalität und Rechenleistung für Desktop-, Mobil- und Ultra- Mobile-PCs ermöglichen soll, während der Strombedarf gering gehalten und die Akkulaufzeit erhöht wird.

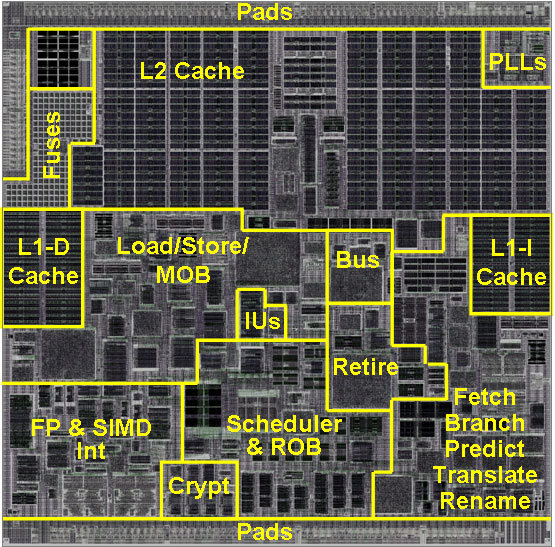

In den letzten vier Jahren von VIAs US-basierendem Prozessor-Design Tochterunternehmen Centaur Technology mit rund 100 Ingenieuren von Grund auf neu entwickelt, kombiniert die Isaiah-Architektur aktuelle Errungenschaften im Bereich der x86-Technologie wie zum Beispiel eine 64-Bit super-skalare spekulative Out-of-Order Mikroarchitektur, eine hochleistungs Multimedia-Recheinheit und eine neue Virtualisierungs-Architektur. Die erste Generation der Isaiah basierenden Produkte ist vollständig Pin-kompatibel mit VIAs C7-Prozessoren und ermöglicht so speziell System Buildern durch die Schaffung einer einfachen Upgrade-Möglichkeit für die bestehenden Designs einen sanfteren Übergang.

Die ersten Prozessoren mit Implementierung der Isaiah-Architektur werden im 65-Nanometer-Prozess gefertigt werden. Dies soll sich vor allem in einer verbesserten Energie-Effizienz, welche, kombiniert mit den neuen überarbeiteten Power- und Wärme-Management-Fähigkeiten, das beste Rechenleistung-pro-Watt-Verhältnis im Markt bieten soll, ausdrücken.

Die Isaiah-Architektur wurde speziell entwickelt, um mit ihren Eigenschaften und ihrer Leistung den hohen Anforderungen heutiger und zukünftiger Internet-Applikationen gerecht zu werden. Dies beinhaltet High-Definition Video, 3D-Spiele, Bildverarbeitung und virtuelle Welten. Unter Einbeziehung der sehr geringen Stromaufnahme, sowie der geringen Abwärme soll sie sich ideal für mobile Geräte mit kleinem Formfaktor wie etwa Mini-Notebooks und Ultra Mobile Devices eignen. Die Schlüssel-Eigenschaften stellt VIA wie folgt dar:

- 64-Bit super-skalare spekulative Out-Of-Order Mikroarchitektur: Die Isaiah-Architektur umfasst eine Vielzahl von erweiterten architektonischen Eigenschaften, wie eine super-skalare Out-of-Order-Architektur, „macro-fusion“ (spezielle x86-Befehle werden zur Effizienzsteigerung zu einer „micro-op“ zusammengefasst) und „micro-fusion“ (mehrere „micro-ops“ die verschiedene Ausführugns-Ports kontrollieren werden zu einer „fused miro-op“) Funktionalität, sowie eine hochentwickelte Sprung-Vorhersage, welche die Prozessor-Effizienz und Rechenleistung signifikant verbessern soll. Sie verfügt über acht verschiedene Prädiktoren in zwei Pipeline-Stufen, wobei auf die erste „Hol“-Stufe drei Prädiktoren für bedingtes Sprungverhalten (jede für einen bestimmten Sprungtyp genauer) entfallen. Die Übersetzungsstufe (die mehr Informationen über die Befehle hat) enthält einen Rückkehr-Prädiktor, einen bedingten Sprung Überlauf Prädiktor und einen Standard-Prädiktor. Jeder Prädiktor ist bei einem bestimmten Sprung an einer bestimmten Stelle der Pipeline genauer. Sie „stimmen ab“ und bringen so die letztendliche Vorhersage hervor.

Die ersten CPUs werden pro Takt drei x86-Instruktionen verarbeiten, drei „fused micro-ops“ generieren, spekulativ und Out-of-Order sieben ausführbare „micro-ops“ (zwei Integer, eine Load, eine Store Adress, eine Store Data, eine „Media“ und eine Multiply Micro-Op) an sieben Ausführungs-Ports ausgeben und drei „fused micro-ops“ verarbeiten. Zusätzlich ist ein kompletter und uneingeschränkter 64-Bit-Befehlssatz mit genug Kopffreiheit für 64-Bit-Betriebssysteme und Applikationen vorhanden. Eine neue Virtualisierungs-Architektur soll für mehr Sicherheit und Effektivität in virtuellen Umgebungen sorgen.

- Hohe Rechenleistung und Multimedia-Verarbeitung: Neben Unterstützung für Taktfrequenzen von bis zu 2 GHz in den ersten Produkten sowie einem Frontside-Bus mit geringer Leistungsaufnahme und zwischen 800 MHz und 1.333 MHz skalierbarem Takt besitzt VIAs Isaiah-Architektur auch ein nach Unternehmensangaben hoch-effizientes Cache Sub-System mit 16-facher Assoziativität (gegenüber 8-facher bei Intel), zwei 64 KB großen L1-Caches (Intel: 32 KB) und 1 MB exklusivem (d. h. die Daten des L1-Cache sind im Gegensatz zu Intels inklusivem Design nicht gleichzeitig im L2-Cache, was dessen effektive Größe vergrößert) L2-Cache (bei den ersten Prozessoren). Im Bezug auf die weitere Verbesserung der Rechenleistung im Bereich Multimedia integrierte VIA die nach eigenen Angaben weltweit schnellste x86 Fließkomma-Einheit (FPU) mit der Fähigkeit vier Fließkomma-Additionen und -Multiplikationen pro Takt auszuführen. Außerdem minimiert ein neuer Algorithmus die Latenzzeiten. Unterstützung für den neuen SSE-Befehlssatz und ein 128-Bit breiter Integer-Datenkanal erhöhen die Multimedia-Rechenleistung zusätzlich.

- Erweitertes Power- und Thermal-Management: Um die Energieaufnahme und Wärmeabgabe zu minimieren, greift die VIA auf neue Schaltkreis-Technologien zurück. Zusätzlich wird durch der neue „C6“-Modus unterstützt, in welchem die Cache-Speicher ausgeschaltet werden. Die weitgehend adaptive „PowerSaver“-Technologie hilft den Strombedarf weiter zu senken und das Wärme-Management weiter zu verbessern. Dies beinhaltet die einzigartige „TwinTurbo“ dual-PLL-Implementierung, welche sich in etwa wie ein Automatik-Getriebe verhält. Sie soll einen sanften Übergang zwischen den Aktivitäts-Stadien während eines Taktzyklus erlauben und eine stetige Verfügbarkeit sicherstellen. Zudem soll die Latenzzeit verringert und durch neuartige Mechanismen das Temperatur-Management verbessert worden sein.

- Skalierbare Aufrüstmöglichkeit für VIAs C7-Prozessor: Die Isaiah-Architektur ist Pin-kompatibel mit der aktuellen C7-Familie und befähigt OEMs und Mainboard-Hersteller zu einem sanften Übergang zur neuen Architektur. So lassen sich mit einem einzelnen Board- oder System-Design deutlich mehr verschiedene Marktsegmente gleichzeitig ansprechen.

- VIA PadLock Hardware-Sicherheit Eigenschaften

Zur Verbesserung der Vertraulichkeit, Integrität und Authentizität von elektronischen Daten greift VIA auf die marktführende on-Die kryptografische Hardwarebeschleunigung der „VIA PadLock Security Engine“ zurück. VIA PadLock bietet laut VIA weiterhin den weltweit besten Zufallszahlen-Generator (RNG), eine AES Verschlüsselungseinheit, SHA-1- und SHA-256-Hashing für sichere und integere Nachrichten-Verarbeitung, sowie einen neuen speziellen, sicheren Ausführ-Modus mit Eigenschaften eines abgesicherten on-Chip Speicherbereiches und verschlüsselter Befehls-Verarbeitung.

Erste Prozessor-Implementierungen auf Basis der VIA Isaiah Architektur werden für das erste Halbjahr 2008 erwartet.