Intel-Prozessor: 15-Kern-Broadwell-Xeon trifft Altera-FPGA auf einem MCP

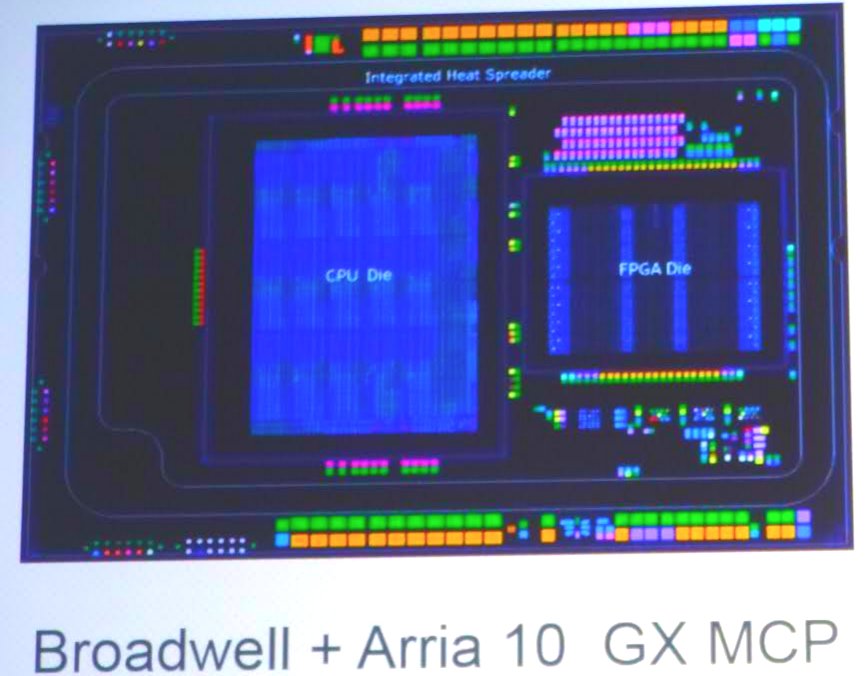

Zum Open Compute Summit hat Intel weitere Details zur Hochzeit eines Xeon-Prozessors mit einem FPGA-Chip von Altera, die mittlerweile zu Intel gehören, auf einem gemeinsamen Multi-Chip-Package (MCP) dargelegt. Demnach basiert der verwendete Xeon-Prozessor auf der Broadwell-Architektur und wird wahrscheinlich 15 Kerne bieten.

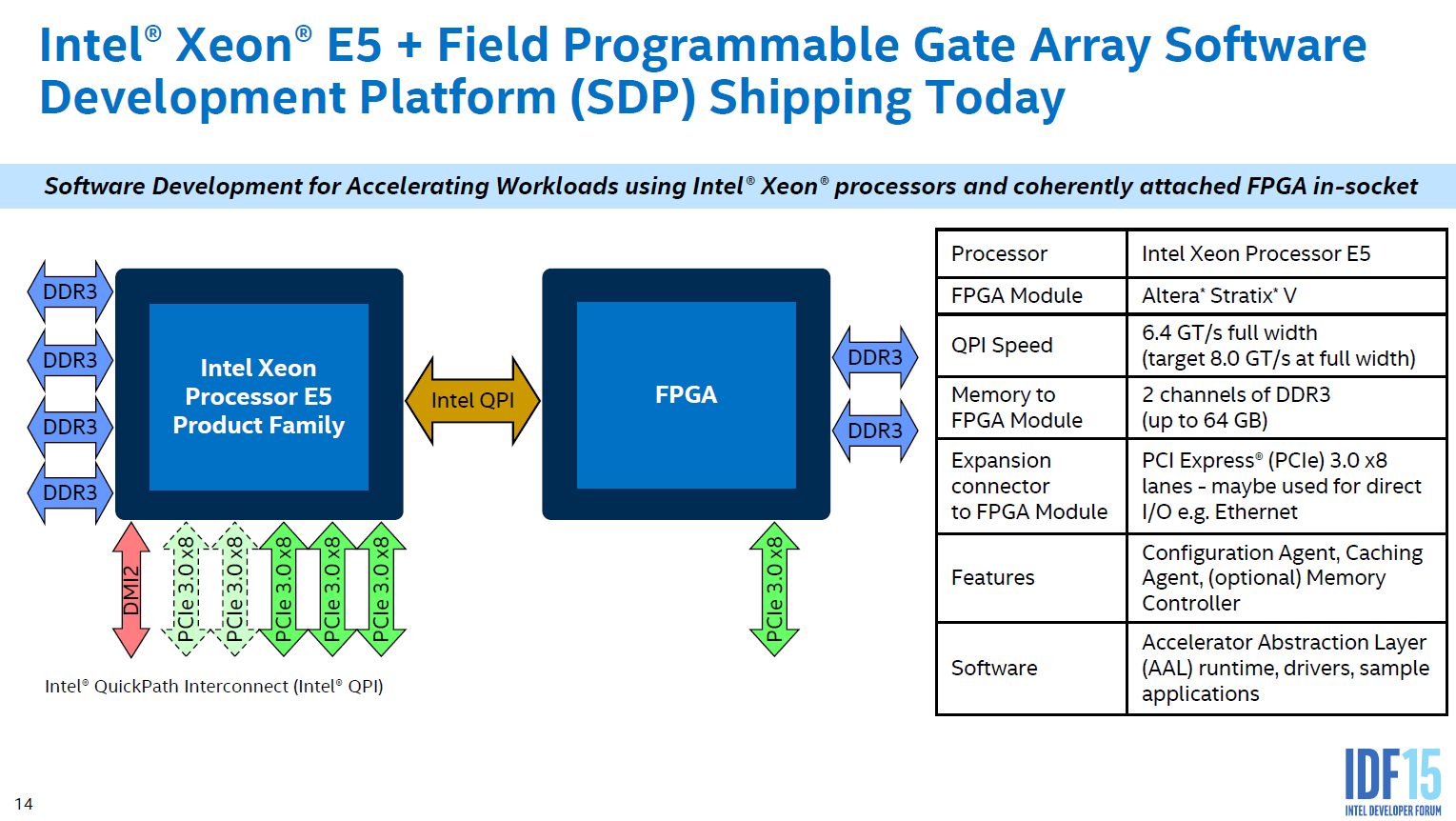

Beim FPGA setzt Intel auf den Altera Arria 10, der als GX-Serie in unterschiedlichsten Variationen (PDF) angeboten wird. Der in 20 nm gefertigte Chip wurde bisher via QPI-Link mit Intels Xeon-Prozessor verknüpft – dies hatte Intel bereits im Rahmen des IDF 2015 im letzten Sommer verraten, bei dem ein Entwicklerkit für Software vorgestellt wurde, die Hardware seinerzeit aber noch nicht dem finalen Stand entsprach. Im finales Design wird jedoch erstmals EMIB (Embedded Multi-Die Interconnect Bridge) zum Einsatz kommen, die Kommunikationen der verschiedenen Chips wird dann durch Leitungen im Package realisiert.

Wenngleich die exakten Details auch jetzt noch nicht bekannt gegeben wurden, sind doch einige zusätzliche Informationen ans Tageslicht gelangt. Der Xeon-Prozessor wird auf einem vollwertigen E5-Modell und damit aus der Familie Broadwell-EP stammen. Anhand des qualitativ nicht hochwertigen Bildes lassen sich 15 Kerne erahnen (5+5+5), deren Aufbau an den Medium Core Count (MCC) des Haswell-EP angelehnt ist, der 4+4+4 Kerne bot. Intel hat diese Angaben jedoch bisher nicht bestätigt, berichtet The Next Platform, schlüssig sind diese jedoch. Denn der größere Chip, der High Core Count (HCC) mit bis zu 22/24 Kernen auf einem Die, wäre für ein Muli-Chip-Package vermutlich einfach zu groß, denn bereits die 15-Kern-Version genehmigt sich einen Großteil des freien Platzes.

Neben dem Schauplatz der Hardware kommt der Software eine Schlüsselrolle zu. Während der Fahrplan für den Chip selbst im Groben steht und vermutlich 2017 als „Off Roadmap Product“ leise eingeführt wird, liegen die Herausforderungen in den Anwendungsfällen und der darauf abgestimmten Software, die gleichzeitig die x86-Kerne ansprechen und die Vorzüge des FGPAs zur Beschleunigung diverser Szenarien inklusive komplexer Ver- und Entschlüsselung nutzen kann. Wenn diese Gratwanderung gelingt, können diese Spezialprozessoren nicht nur im Cloud-Umfeld, sondern auch im klassischen Netzwerk- und Enterprise-Bereich eingesetzt werden.