Mit Graphen oder CNTs wird man nichts erreichen, denn der Subthreshold Swing ist bei diesen Materialien aufgrund des Fehlens einer echten Bandlücke einfach viel zu gering. Das sind eher Möglichkeiten für die Displaytechnologie, da sie hohe Leitfähigkeit und Transparenz bei potentiell niedrigen Kosten vereinen, zudem flexibel und damit technischen Oxiden potentiell überlegen sind.

Die angegebenen Längen beziehen sich ja immer auf die Gatelänge. Deswegen ist es schon möglich, dass ein 14nm Transistor ja dann eigentlich doch viel größer ist. Aber die Gatelänge ist das, was für den Transistor interessant ist.

Die ganze Sache ist insgesamt unglaublich. Man muss sich nur vorstellen, was dahinter steckt. Wenn ich eine 10nm Mehrfachbelichtung mache, muss ich Maske und Wafer auch jedes mal noch viel präziser positionieren - wer einmal eine Mehrfachbelichtung im µm Bereich von Hand gemacht hat, kann ungefähr abschätzen, was das bedeutet. Und wenn man bedenkt, dass das physikalische Limit für die 193nm-UV-Lithographie an sich bei rund 80nm liegt (und da ist die Immersionslithographie schon bedacht) und wir mittlerweile eine ganze Größenordnung darunter liegen - unglaublich.

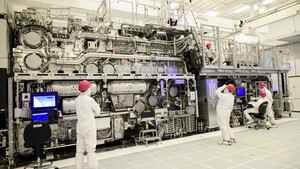

An EUV wird allerdings kein Weg vorbei führen, da man anders einfach irgendwann keine Parallelprozesse mehr hinbekommt. Klar, man kann auch mit Ionenstrahlen schreiben, aber nur sequentiell. Daher wird der Technologievorsprung für ASML hier eine Goldgrube sein. Wann EUV aber großtechnisch angewandt wird, wird sich herausstellen.

Und danach funktionieren meine Resonanztunneltransistoren vielleicht irgendwann ja mal. Muss ja einen Ausweg zum MOSFET geben, wenn man nicht mehr kleiner wird und der Durchgriff nicht besser wird.