Knogle

Lieutenant

- Registriert

- Mai 2014

- Beiträge

- 682

Moin

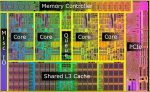

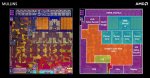

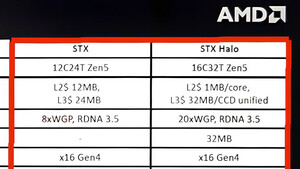

Habe eine Frage... Undzwar, was fuer Speicherbausteine kommen in Prozessoren zum Einsatz? Und wie sind diese an den Kern angebunden bzw. implementiert?

Beispiel: Der Xeon X5650 aus 2009 hat im L1 Cache eine Schreibgeschwindigkeit von 1,2TB/s der Xeon E3 1231v3 dagegen nur 800GB/s

Woher kommen diese Unterschiede?

MfG

Habe eine Frage... Undzwar, was fuer Speicherbausteine kommen in Prozessoren zum Einsatz? Und wie sind diese an den Kern angebunden bzw. implementiert?

Beispiel: Der Xeon X5650 aus 2009 hat im L1 Cache eine Schreibgeschwindigkeit von 1,2TB/s der Xeon E3 1231v3 dagegen nur 800GB/s

Woher kommen diese Unterschiede?

MfG