Problem ist wirklich das alle Ergebnisse nicht auf jedes Board übertragbar sind was vorallem an den verschiedenen Signallaufzeiten durch unterschiedliche Boardlayouts im Speicherslotbereich liegt.

Grund ist das nur identische Module gleiche Zugriffszeiten und aufgrund identischen Speichermodul-Leiterbahnenlayouts auch identische,

gleichlange Bitleitungslängen der Daten(Übertragung) und Adressleitungen(Adressierung) zwischen den Pins und somit "Signallaufzeiten" (Pin-to-Pin-Signallaufzeit in ms) haben. Nur so kann der Speichercontroller optimal mit vorallem mehreren Modulen im Endeffekt synchron hantieren. Am Motherboard muss ja das auch ausgeglichen werden durch absichtlich geschlingelte Leiterbahnlängen um diese dadurch alle in der Länge zwischen Speicherbänken und Speichercontroller auszugleichen -

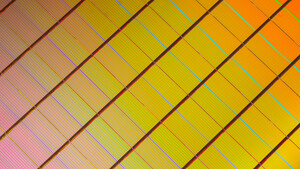

alle durch absichtliches "schlingeln" gleich lang gehalten wie dieses Bild zeigt :

(Quelle :

http://www.pci-card.com )

Sind aber jetzt verschiedene Speichermodule drinnen oder welche eines Herstellers mit "unsymphatischen" Bitleitungs-Layout auf dem Speichermodul kann das nicht mehr zu 100% funktionieren weil diese absichtlich geschlingelten Leiterbahnlängen zwecks identischer Signalaufzeiten davon ausgehen das identische Module mit eben auch auf den Speichermodul identischen Bitleitungslängen drinnen sind oder aber einem disbezüglichen Schätzwert entsprechen für welchen es aber leider keine NORM gibt, schliesslich können auch die verschiedenen Boardhersteller nicht ahnen mit welchem Speichermodul der User das Board mal betreiben will - somit müssen hier "Kompromisse" gemacht werden und das heisst auch :

Im Endeffekt, also gesammte Bitleitungswege zwischen Speicherchips-Pins über Speicherplatinenlayout -> Speicher-Datenbus am Board und Speichercontrolleranshlusspins stimmt dann also dieser "Längensausgleich" nicht mehr wenn nicht auch die Module identisch sind oder mit "unglücklichen Gegen-Layout" und somit dann insgesammt keine identische Bitleitungslängenverhältnisse mehr vorherschen und genau das ist manchmal Fall.Beispielbild : Leider manchmal je nach Hersteller zu unterschiedliche Bitleitungslängen und damit Signallaufzeiten ("SRT") am Platinenlayout des Ram-Bausteins (hellgrüne Leitungswege) :

Problem ist eben vorallem das bezüglich Signallaufzeiten jeder Hersteller sein eigenes "Layout-Süpchen" auf seinen Speichermodulplatinen kocht und dadurch ein Speicher was das betrifft in einem Board wunderbar harmoniert und in anderem gar nicht.Verschobene Signalaufzeiten können ein Misinterpretieren von Bit-Werten (I/0) beim auslessen der einzelnen Zellen über die Datenleitungen zur Folge haben (von Bitdatenlängen abhängige Laufzeiten der Bits) und das Datenverlust und somit Instabilität.Von daher sind eigentlich sämtliche Speichertests welche sich auf zahlreichen Internetseiten finden nur zu 50% zu gebrauchen da extrem Boardabhängig.Ganz abgesehn davon das oft BIOS-Udpates das Verhalten mit gewissen Speichermarken postitiv ändern kann (vorallem bezüglich SPD-Übernahme) was einen Test auf Board "xy" nochmal fällig machen würde und damit nochmal weniger auf andere Boards übertragbar ist.

Weiterer Grund, die Signaltermination harmoniert je nach Board<->Speicherkombination etwas anders :

Zusätzlich kommt noch hinzu das DDR-SDRAM keine gute Termination hat.Wärend z.b. bei RABMUS die Signalführung durch alle Chips und Module linear hinduch geht und dann sauber terminiert wird um Reflektionen am Ende einer "Stichleitung" zu vermeiden ist die Signalführung bei DDR-SRAM parallel und die Buse werden erst am Motherboard neben den Speicherbänken per Widerstände abgeschlossen/terminiert.(Um Signalrefletkionen oder Busrauschen durch zu lange Terminationswege zu vermeiden)

Wer mal dicht neben den Speicherslots entlang schaut kann diese vielen Widerstand-Bauteile sehen :

(sehen aus wie kleine schwarze Spinnen entlang den Slots, auch "Widerstandsnetzwerk" genannt))

Leider ist aber auch hier das Bitleitungslayout zu diesen Widerstand-Bauteilen je nach Boardhersteller leicht unterschiedlich und dadurch kann es auch hier je nach Speichermodulmarken<->Boardmarken-Kombination zu sauberer Termination kommen oder eben nicht.Dieses Problem steigt bei zunehmenden Speichertakt denn da müssen sämtliche Datenbus und Terminationswege zunehmend kurz gehalten werden sonst steigen mit zunehmender Frequenz Signalreflektionen und ausserdem "schwingt" sich mit zunehmden Takt das Busrauschen nach oben bei gleichen Bitwerten auf den Leitungen was andere dadurch "mitkippen" und damit verfälschen kann aber auch hier verhällt sich nicht jedes Board trotz gleichem Speichermodul gleich.

Das alles ist neben BIOS/SPD-Inkompatibilitäten der Hauptgrund warum "Modulmarke A" auf Board "X" super geht aber auf Board "Y" nicht.

und das ist somit leider auch der Grund warum Speichertests nie "boardübergreifend" gelten können und werden.

P.S:

Ich hoffe mein üpiges Posting hat niemanden gelangweilt, aber ich dachte mir vielleicht ineteressiert es ja welche was genauer dahinter steckt.