IDF: Intel zeigt Nehalem in Aktion

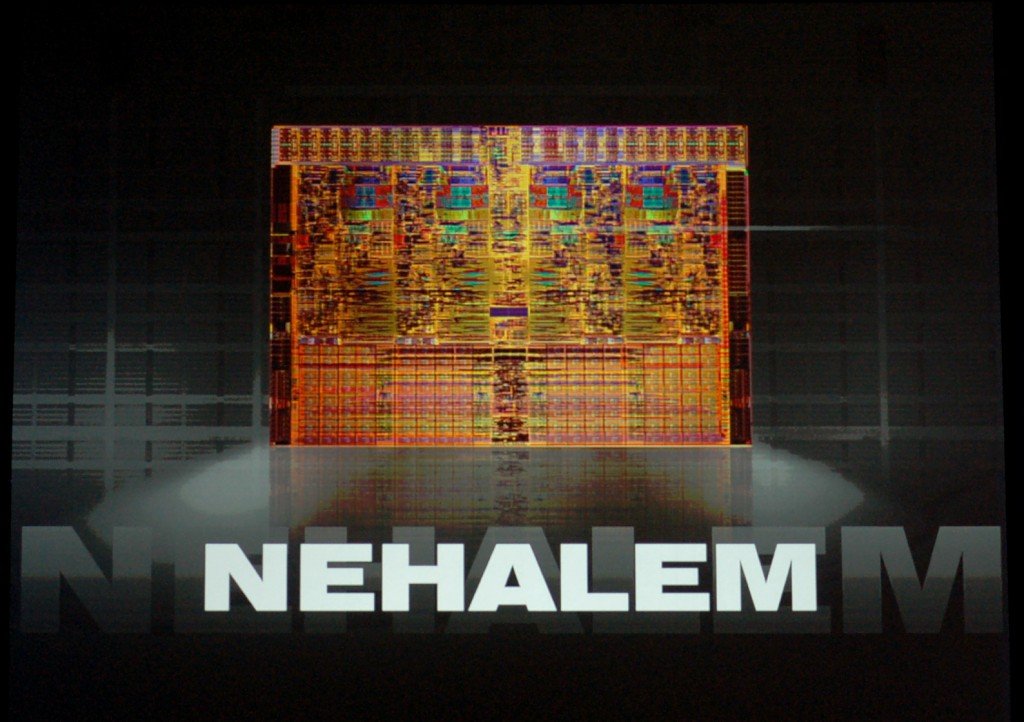

Nehalem – Er ist noch ein Jahr entfernt und doch kann Intel im Rahmen des IDF in San Francisco schon ein erstes lauffähiges Muster präsentieren. Zusammen mit Nehalems Chefentwickler Glen Hinton hatte Intel-Chef Paul Otellini die Ehre, den in 45 nm gefertigten Penryn-Nachfolger in Aktion demonstrieren zu dürfen.

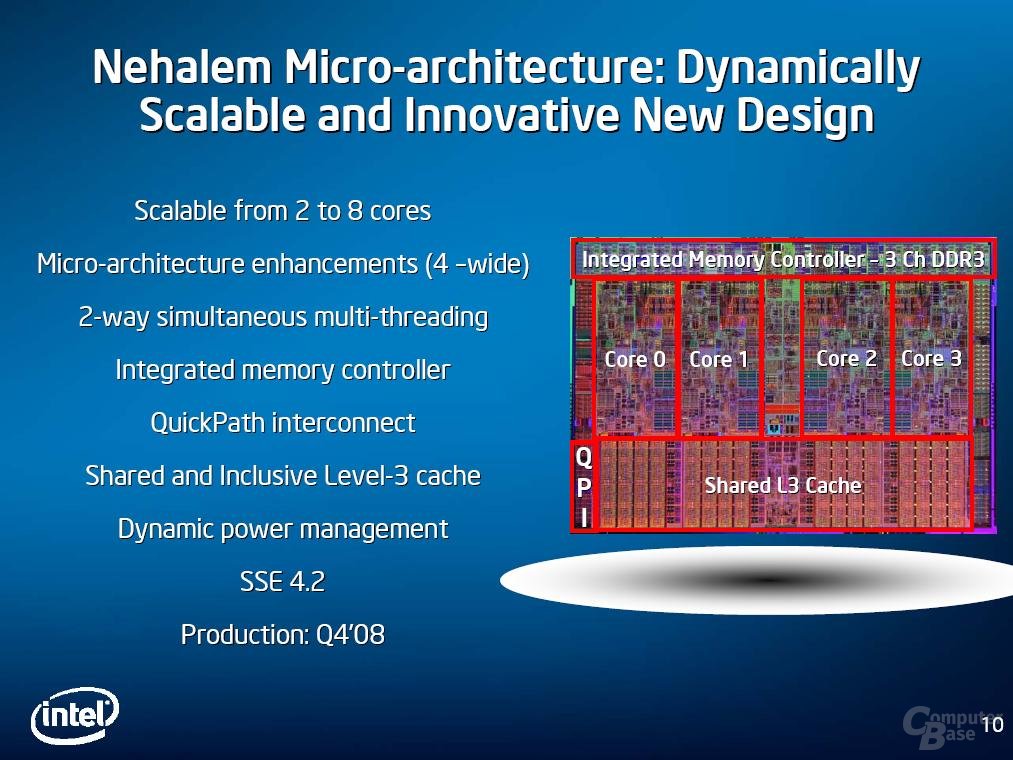

Beim insgesamt 731 Million Transistoren schweren Chip handelt es sich um ein natives Quad-Core-Design mit vier Rechenkernen (siehe Die-Shot), der mit Hilfe des wieder zum Leben erweckten HyperThreading – neuerdings vermarktet unter der allgemeinen gültigen Bezeichnung Simultaneous Multi Threading (SMT) – insgesamt acht virtuelle Kerne und insgesamt 8 MB L2-Cache bietet. Wie das seiner Zeit mit dem 3,06 GHz schnellen Pentium 4 (Northwood) eingeführten HyperThreading, sollen die vorhanden Prozessorressourcen hierdurch besonders effizient ausgenutzt werden können.

Das gezeigte Nehalem-Sample basiert auf dem allerersten A0-Stepping und hat erst vor drei Wochen die Silizium-Fab verlassen. Der Halbleiterriese musste sich also durchaus beeilen, um diese Demonstration zu ermöglichen. Schließlich will der Chip nicht nur getestet, sondern auch mit einem entsprechenden Gehäuse versehen werden. Erschwerend kommt hinzu, dass Intel sich mit Nehalem vom betagten Frontside-Bus verabschiedet und stattdessen auf das neue QuickPath-Interface (QPI, ehemals CSI) setzt, und somit nach einem neuen Sockel und Chipsatz verlangt – reichlich Fehlerquellen, die erst einmal genommen werden wollen. Ein bisher bekannter Nehalem-Chipsatz trägt den Namen Tylersburg. Die darauf basierte Plattform heißt Truley DP (zwei Sockel mit Gainestown) oder Truley UP (ein Sockel mit Bloomfield).

Die kurze Zeit hat jedoch genügt, um Nehalem – wie Intel bekannt gab – zur Zusammenarbeit mit Windows XP und Mac OS X zu bewegen. Zum Beweis der Funktionfähigkeit wurde auf einem mit Nehalem bestückten PC im Media Player von Windows XP eine Audio-Datei abgespielt: „Hi Paul, I am Nehalem. I am only three weeks old, and already talking“. Über den Prozessortakt machte Paul Otellini keine Angaben. Es gilt als wahrscheinlich (aufgrund des gezeigten Die-Shots), dass es sich beim gezeigten Nehalem um Bloomfield/Gainestown mit Sockel B (Socket B, LGA1366) handelt. Weitere Nehalem-Varianten tragen den Codenamen Beckton (acht Kerne, Stoutland-Plattform, Boxboro-Chipsatz, 2009), Havendale/Lynnfield (? Kerne, Foxhollow-Plattform, ? Chipsatz, 2009).

Über Nehalem hat Intel in der Vergangenheit schon einige Details bekannt gegeben. Hierzu gehören z. B. ein modulare Design für bis zu acht oder mehr Kerne oder die Option, eine Grafiklösung mit in den Prozessor zu integrierten. Auch ist klar, dass es sich um die dritte Weiterentwicklung der Core Mikroarchitektur handelt, die in ersten Generation (65 nm) im Conroe/Merom/Woodcrest/Kentsfield/Clovertowen/Tigerton und in der zweiten Generation (45 nm) im Penryn/Wolfdale/Yorkfield/Harpertown zum Einsatz kommt. Nehalem ist demnach auch weiterhin 4fach-skalar. Einher mit QuickPath geht auch die Integration des Speichercontrollers, wie es bei AMD seit dem Athlon 64/Opteron üblich ist.

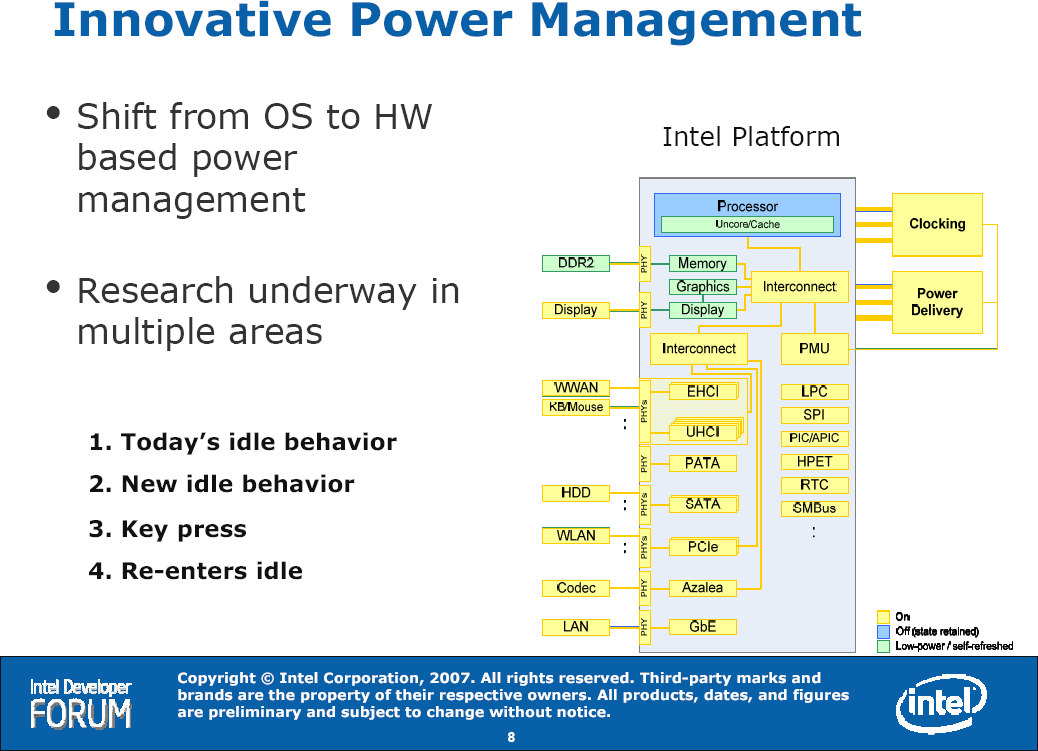

Zu den neuen Informationen über Nehalem gehört unter anderem, dass der Chip seine Stromsparzustände (ACPI Power Modes) unabhängig vom BIOS oder dem Betriebssystem selbst steuern kann. Inwieweit diese Steuerung über dem bei Intel bereits länger eingesetztem (und bei AMD mit Barcelona erstmals unterstützten) C1E (Enhanced Halt State) hinaus geht, muss sich noch zeigen. Auch die Nehalem-Kerne sollen einzeln deaktiviert werden können – der Chip scheint damit auch in der Lage zu sein, als Triple-Core arbeiten zu können. Dass Intel die Stromsparfunktionen langfristig nicht mehr den (teils unfähigen) Betriebssystemen überlassen möchte, hat das Unternehmen bereits gestern im Rahmen der so genannten „Day 0“-Veranstaltungen bekundet, die sich in der Regel versteckt um Forschung und Entwicklung (Research and Development, R&D) drehen.

Otellini gab zudem bekannt, dass Intel ab 2008 bei der Fertigung der Gehäuse für 45 nm-Prozessoren und 65 nm-Chipsätze auf Halogen verzichtet. Da Intel bei der Produktion seiner 45-nm-Hi-k-Prozessoren, die ein High-k Metall Gate (Hi-k)-Dielektrikum als Isolierschicht am Gate des Transistors nutzen, komplett auf Blei verzichtet, ist die künftige Prozessorgeneration nicht nur energieeffizienter, sondern auch umweltfreundlicher.

Erste Prozessoren auf Basis der Nehalem-Architektur sollen in der zweiten Hälfte des kommenden Jahres erscheinen.

Im Podcast erinnern sich Frank, Steffen und Jan daran, wie im Jahr 1999 alles begann.