Intels „Haswell-EP“ mit bis zu 14 Kernen und 35 MB Cache

Wieder einmal sind Informationen zu einer kommenden CPU-Generation von Intel in einem asiatischen Forum gelandet. Dieses Mal ist die neue Architektur „Haswell“ gemeint, deren erste Ableger für 2013 erwartet werden. Genauer gesagt betreffen die Details den Server-Chip „Haswell-EP“, der für Xeon-Systeme mit zwei CPUs geplant ist.

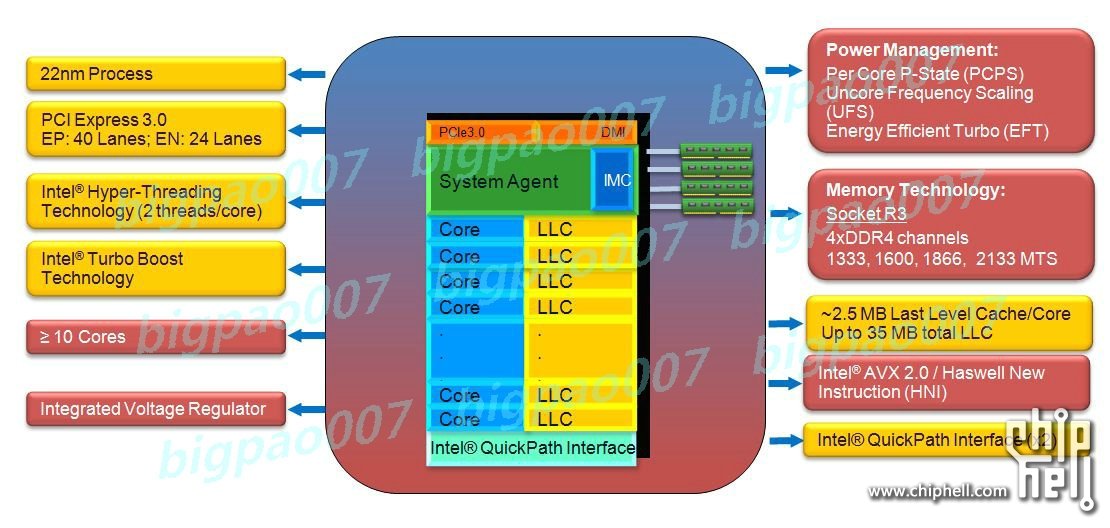

Wie die publizierten Folien aufzeigen, sollen die in 22 nm gefertigten „Haswell-EP“ mindestens zehn Kerne oder mehr besitzen. Anhand der Angaben von 2,5 MB Cache pro Kern sowie insgesamt bis zu 35 MB Cache lässt sich ableiten, dass die höchste Ausbaustufe über 14 Kerne verfügen wird. Während man bisher Formulierungen wie L1-, L2- und L3-Cache gewohnt war, ist hier lediglich die Rede von Last Level Cache (LLC), wobei scheinbar jedem Kern ein eigener LLC zugeordnet ist.

Wie bereits vermutet, soll der neue Arbeitsspeicher-Standard dieses Mal im Server-Segment sein Debüt feiern. Vier DDR4-Speicherkanäle soll der integrierte Speichercontroller von „Haswell-EP“ bereitstellen. Die aufgeführten Speichergeschwindigkeiten wirken dabei angesichts erster Module mit effektiv 2.400 MHz gering und passen eher zum aktuellen DDR3-Standard, jedoch sollte aufgrund der noch nicht offiziell verabschiedeten DDR4-Spezifikation darauf nicht allzu viel Augenmerk gelegt werden.

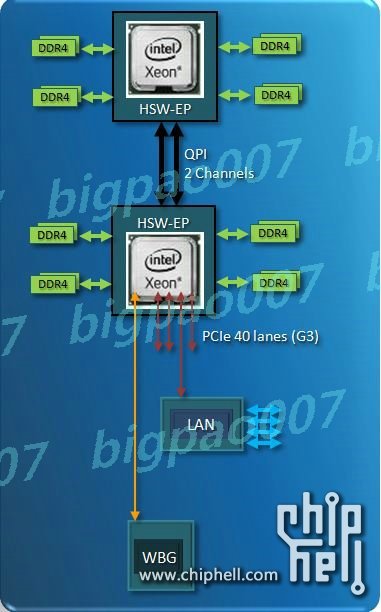

Neben dem 4-Kanal-Speichercontroller und dem 2-Kanal-QPI (Quick Path Interface) zur Kommunikation zwischen den CPUs in Zwei-Sockel-Systemen soll „Haswell-EP“ zudem 40 PCI-Express-3.0-Lanes bereitstellen, für „Haswell-EN“ werden hier 24 Lanes genannt. Zu den Neuerungen im Bereich der Befehlssätze wie AVX 2.0 und der sogenannten Haswell New Instruction (HNI) gesellen sich altbekannte Funktionen wie Intels Hyper-Threading, das zwei Threads pro Kern ermöglicht und der Turbo-Boost, der ein automatisches dynamisches Übertakten eines Teils der Kerne vollzieht. Bezüglich Stromversorgung und Leistungsaufnahme werden Änderungen im Power Management und eine integrierte Spannungsregelung aufgeführt.

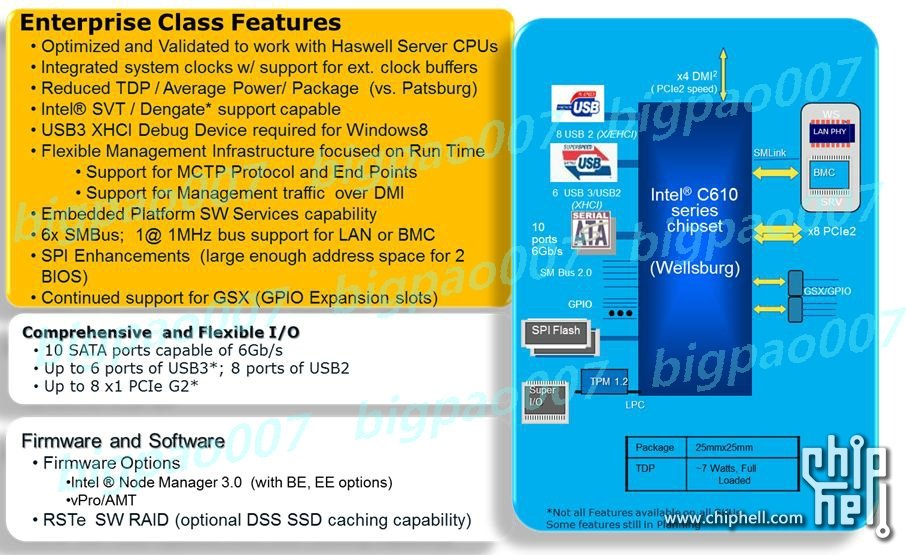

Schließlich soll mit dem C610 ein neuer Chipsatz mit dem Codenamen „Wellsburg“ Einzug halten, der den „Haswell“-Xeon zur Seite steht. Auf Seite der I/O-Unterstützung werden unter anderem zehn SATA-Ports mit 6 GBit/s sowie bis zu sechs USB-3.0-Ports beschrieben. Die Leistungsaufnahme soll gegenüber dem Vorgänger C600 („Patsburg“) sinken.

Da Intel erst Anfang März die „Sandy Bridge-EP“ offiziell in den Markt entließ und die Nachfolger „Ivy Bridge-EP“ noch in weiter Ferne (2013) liegen, dürfte „Haswell-EP“ voraussichtlich erst 2014 eingeführt werden. Zuvor werden im kommenden Jahr die kleineren „Haswell“ mit deutlich weniger Kernen auf den Markt kommen, deren Einführung laut diverser Roadmaps für das erste Halbjahr 2013 geplant ist.