AMD Carrizo: Deutlich effizienter und etwas schneller

Im Vorlauf der International Solid-State Circuits Conference (ISSCC) hat AMD weitere Details zur neuen Notebook-APU mit dem Codenamen Carrizo veröffentlicht. Während die IPC der neuen Excavator-CPU-Kerne nur um fünf Prozent zulegen, wurde gleichzeitig jedoch deren Energieaufnahme um bis zu 40 Prozent reduziert.

Die Optimierung auf ein Low-Power-Design stand bei AMD im klaren Fokus, was auch die letzten Meldungen und den fehlenden Auftritt im Desktop erklärt. Denn während die Leistung der Prozessorkerne von Steamroller auf Excavator durch kleine Optimierungen am Design, wobei die Verdoppelung des L1D-Caches hervorsticht, nur um fünf Prozent zulegt, sind die Einsparungen bei der Energieaufnahme auf dem Papier beeindruckend. Im Desktop-Umfeld lässt sich mit diesen Eigenschaften wenig gewinnen, im Notebook-Markt bringt AMD dies aber in eine deutlich bessere Ausgangslage als zuvor. Anvisiert werden deshalb Modelle bereits ab einer TDP von 12 Watt, denn genau in diesem Low-Power-Bereich sind die Vorteile der Anpassungen am größten.

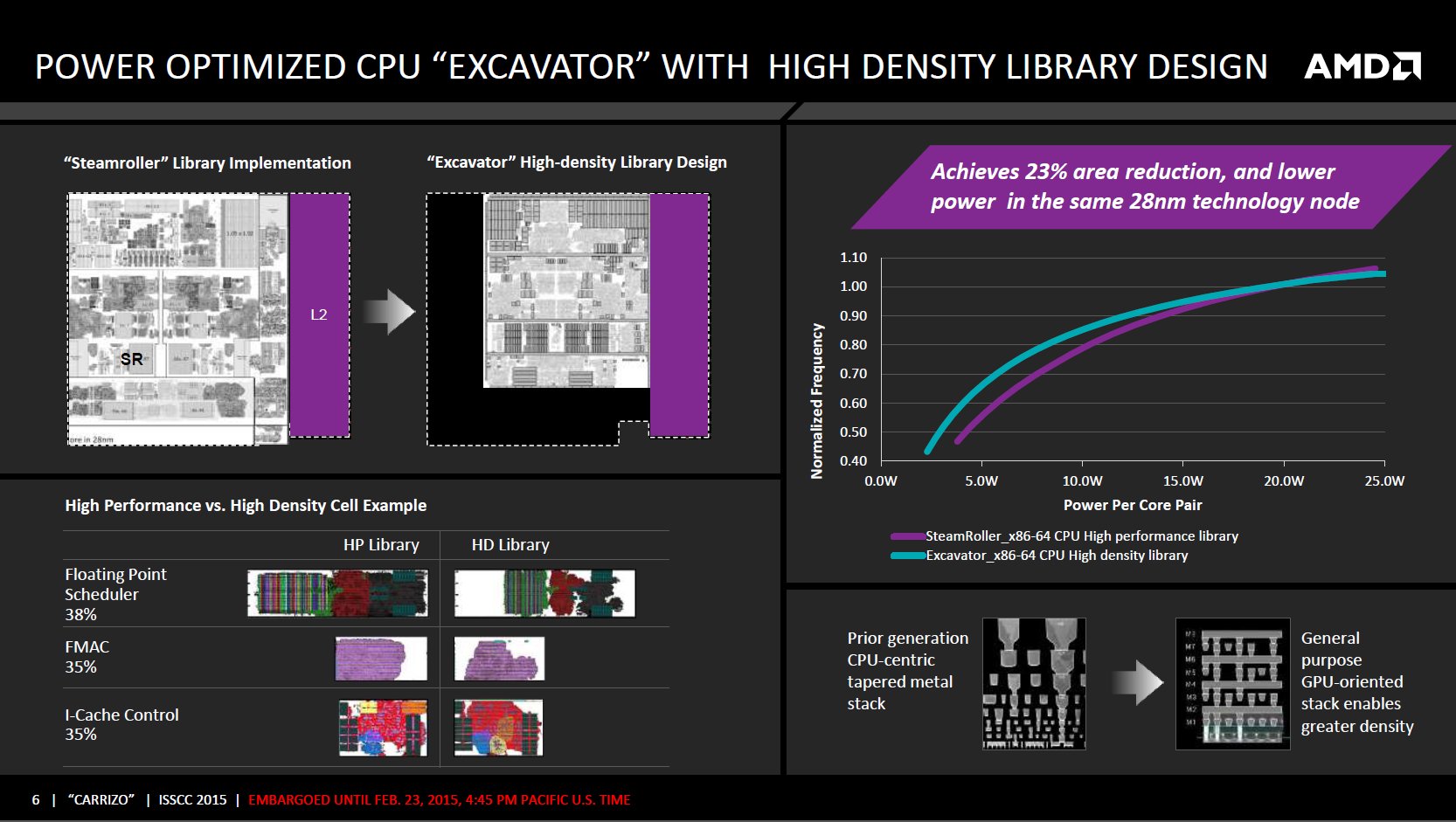

AMD nutzt beim Carrizo-Design Verfahren, die bei klassischen Grafikchips bereits seit Jahren zum Einsatz kommen. Mit der „High Density Library“ werden dank fortschrittlichen automatisierten Design-Tools diverse Bereiche komplett neu angeordnet und letztendlich so platzsparend auf dem Die untergebracht, dass allein die Prozessorkerne insgesamt 23 Prozent weniger Fläche trotz gleichbleibender 28-nm-Fertigung nutzen. Der frei gewordene Platz wird unter anderem genutzt, um den Chipsatz, von AMD Fusion Controller Hub (FCH) genannt, im gleichen Die unterzubringen, während bei der Grafikeinheit nur kleinere Platzoptimierungen greifen konnten. Unterm Strich bringt AMD so 3,1 Milliarden Transistoren auf 245 mm² unter, der Vorgänger kam auf 2,41 Milliarden Transistoren bei gleicher Flächengröße.

Auf Seite der Spezifikationen sind einige Punkte aber auch heute noch unklar, diese will AMD erst in den kommenden Wochen enthüllen. Bisher hieß es, dass beispielsweise der L2-Cache von zwei auf ein Megabyte pro Modul halbiert wird, die Folie aus der Präsentation zeigt jedoch exakt die gleiche Fläche, die der L2-Cache belegen soll, was eine Verkleinerung ausschließt.

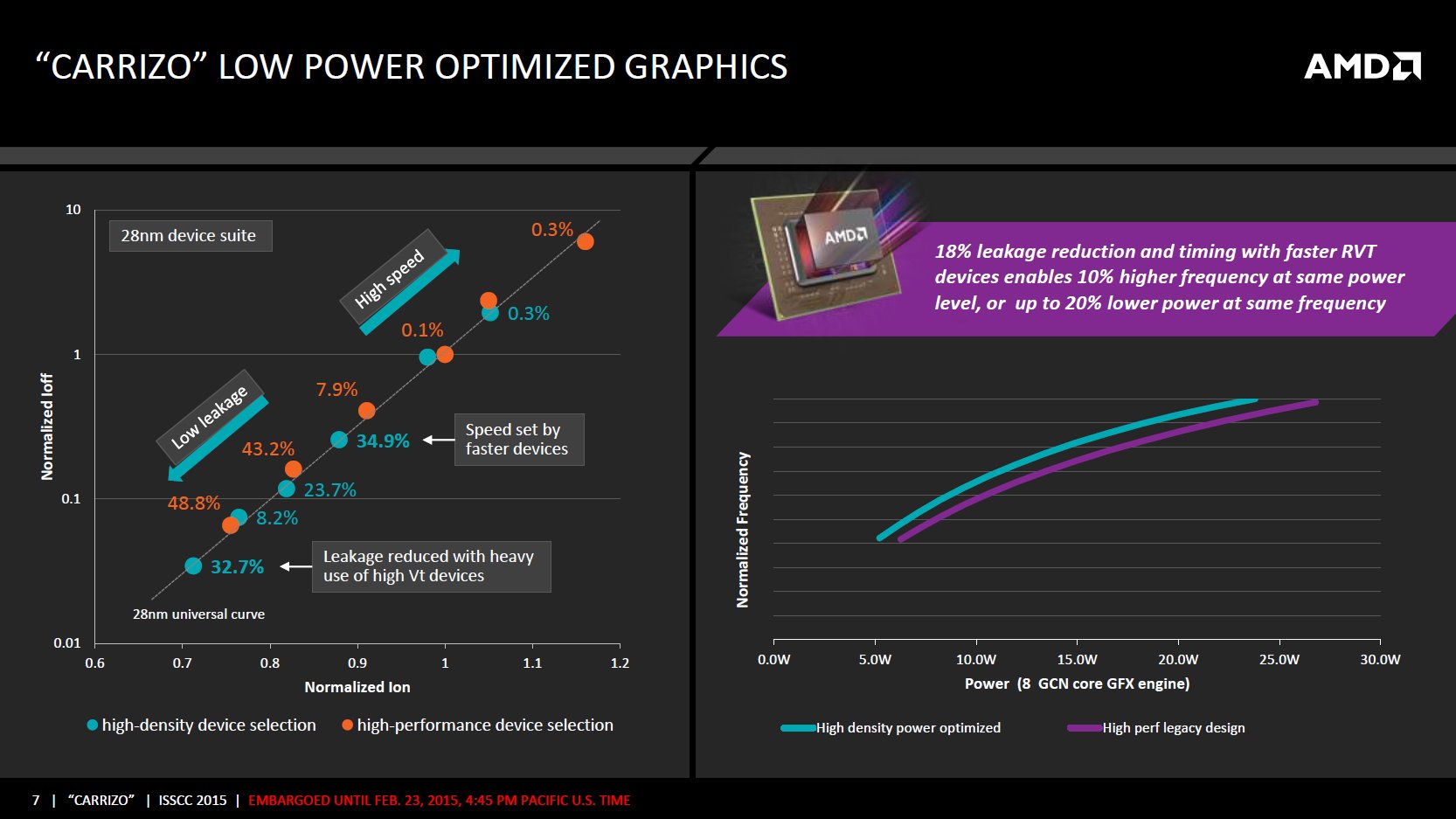

Auch ist bisher immer lediglich von dem Vollausbau der Grafikeinheit die Rede, keine eventuell für 12 Watt angepassten Varianten wurden bisher genannt. Dass im kompletten Bereich von 12 bis 35 Watt zwei Module mit ihren vier Threads sowie die 512 Shader starke Grafikeinheit zum Einsatz kommen, gilt als unwahrscheinlich, soll laut AMD jedoch möglich sein. Denn bei der Graphics-Core-Next-Grafikeinheit greifen keine gravierenden architektonischen Neuerungen, in erster Linie wurde auch dort an der Leistungsaufnahme gearbeitet. Alternativ kann so aber auch ein zehn Prozent höherer Takt ermöglicht werden. Die Neulinge bieten noch einen Vorteil: Bei der Nutzung des neuen HEVC/H.265-Standards soll mehr als die 3,5-fache Leistung bei der Decodierung gegenüber Kaveri erzielt werden.

Strom sparen stand bei allen Punkten des Designs der Carrizo-APU ganz weit vorn, AMD hat dort aber auch einen großen Rückstand aufzuholen. Kaveri als Vorgänger konnte bereits in einigen Punkten deutlich verbessert auftreten als die bisherigen Modelle, für eine verstärkte Präsenz im Handel hat das aber erneut nicht gereicht.

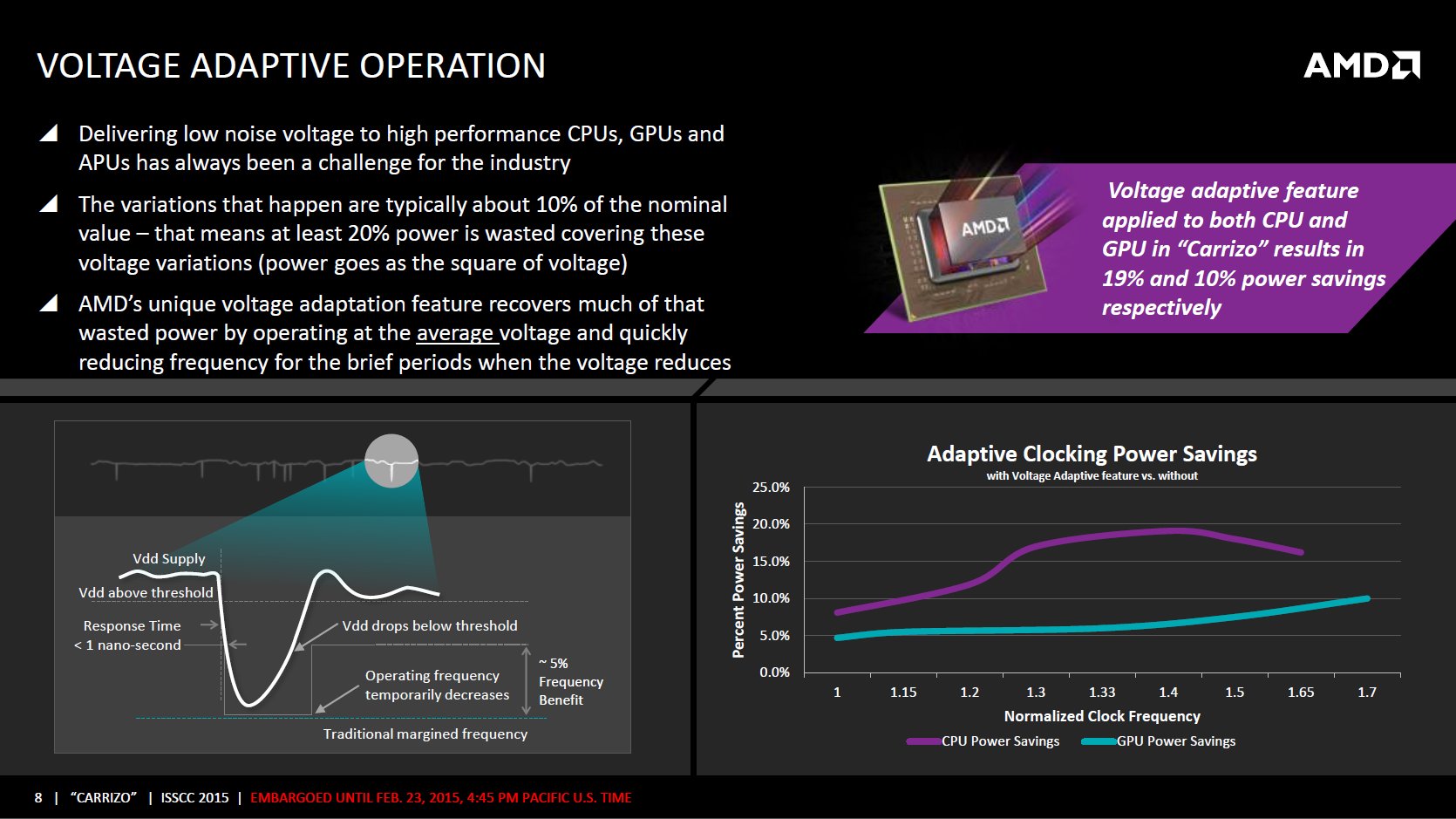

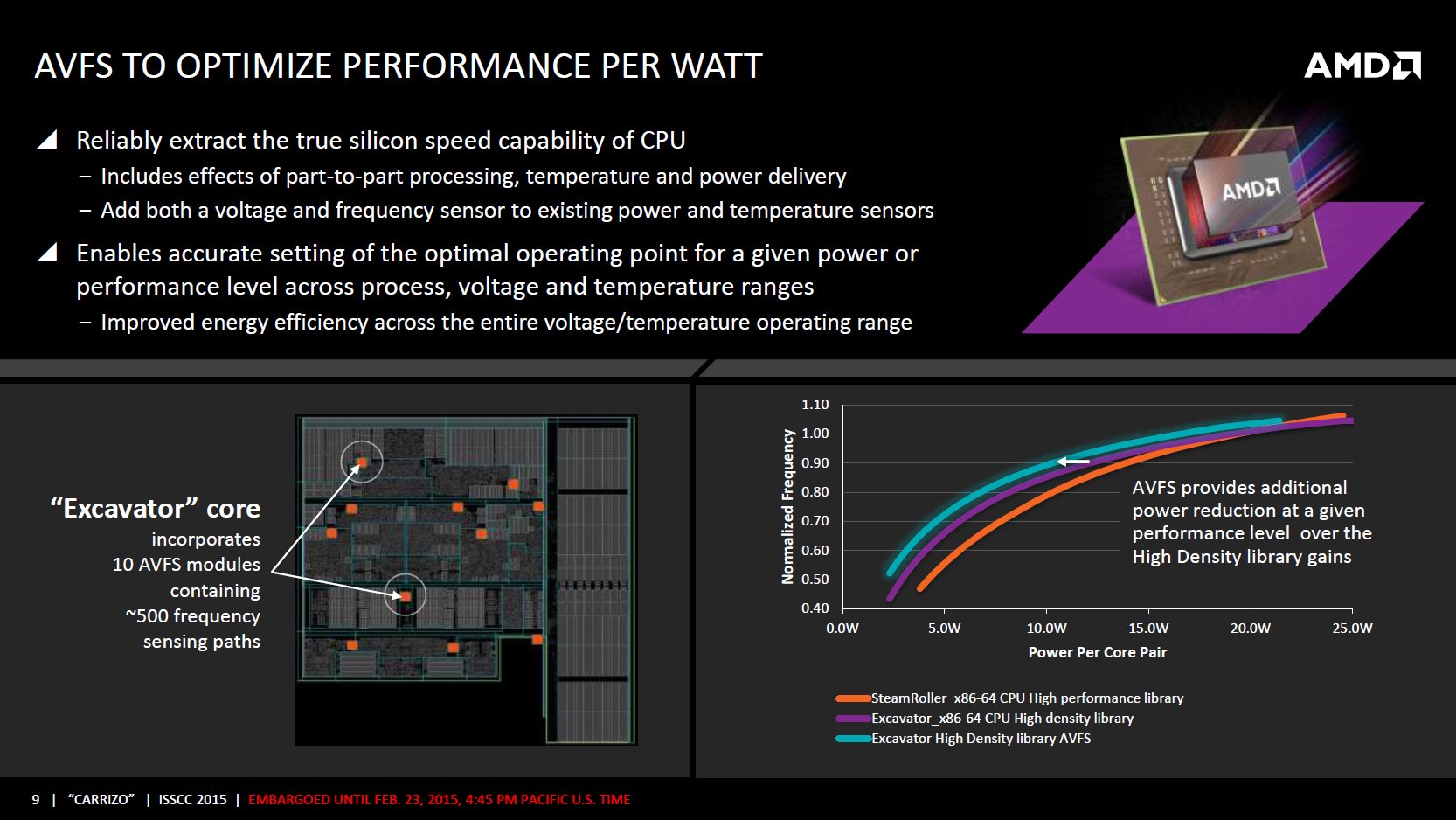

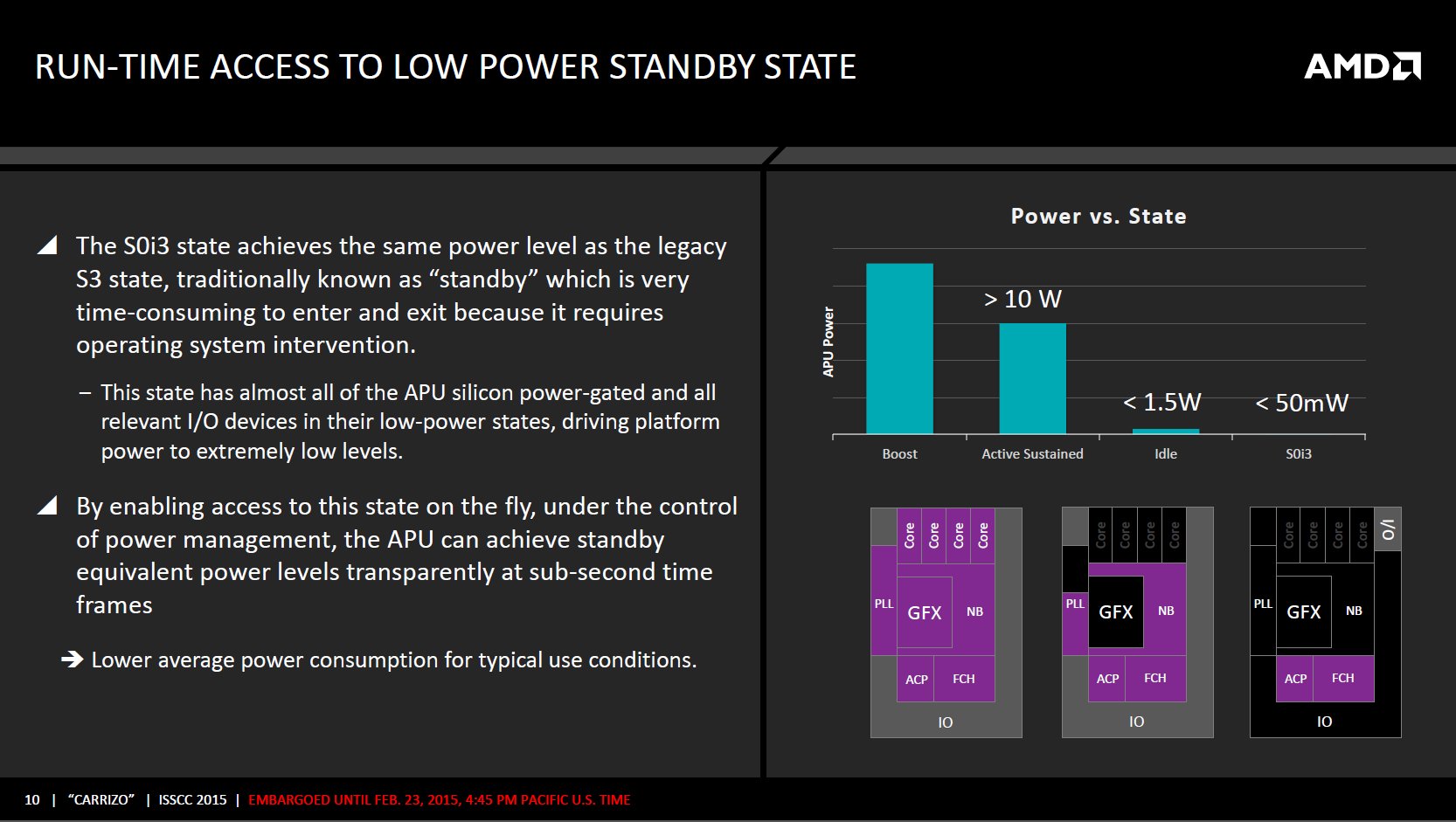

Bei Carrizo nutzt AMD mehrere kleine Kniffe, um der Leistungsaufnahme Herr zu werden. Diese versprechen im Detail oft große prozentuale Einsparungen. Hervor sticht das Voltage Adaptive Feature, welches bei einem plötzlichen Einbruch der Spannung den Takt leicht absenkt, um so eventuell auftretenden Fehlern zu begegnen. Normalerweise wird die Spannung bei gleichbleibendem Takt angehoben, um dem zu begegnen. AMD geht jedoch in die andere Richtung, um so die Effizienz zu erhöhen. Mit von der Partie sind auch neue Takt- und Spannungssensoren im CPU-Kern, mit dem S0i3-Stromsparmodus greift zudem eine angepasste S3-Standby-Funktion, die nahezu alle Teile der APU bis auf grundlegende Features an der I/O-Schnittstelle und dem Chipsatz (FCH) innerhalb von maximal 500 ms abschaltet – im Notebook-Segment besonders wichtig.

AMDs Carrizo-APUs sollen in den kommenden Monaten in den TDP-Klassen von 12 bis 35 Watt eingeführt werden. Details zu Taktraten und der Ausstattung des integrierten Chipsatzes wollte AMD noch nicht preisgeben. Da sich bisher aber alle offiziell bekannt gegebenen Informationen mit der inoffiziellen Präsentation aus dem letzten Sommer decken, sind die noch fehlenden Variablen leicht ablesbar. Einen Termin gibt es ebenfalls noch nicht, im Webcast vorab hieß es nur dieses Jahr. Dabei wird die Plattform letztlich kompatibel zum kleinen Ableger Carrizo-L sein, was die Kosten für Partner senkt. Details zu Carrizo-L wurden aber ebenfalls nicht bekannt gegeben.