- Registriert

- Juli 2010

- Beiträge

- 12.918

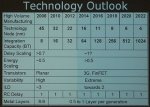

Seit über zehn Jahren forscht IBM zusammen mit anderen Unternehmen und Institutionen der Halbleiterbranche an neuen Technologien zur Herstellung von Mikrochips. Die Zusammenarbeit mit UMC im Rahmen der sogenannten Technology Development Alliance wird für neue Herstellungstechniken vertieft.

Zur News: UMC und IBM vereinen Kräfte für 10-nm-Fertigung

Zur News: UMC und IBM vereinen Kräfte für 10-nm-Fertigung