- Registriert

- Juni 2001

- Beiträge

- 18.348

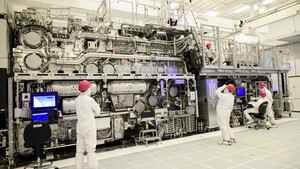

Im Rahmen der SPIE Photomask Technology Conference in Kalifornien hat Martin van den Brink,

Präsident und CTO des niederländischen Fabrikausrüsters ASML, die aktuellen Fortschritte bei der anstehenden EUV-Lithografie erläutert. In der Serienfertigung erwartet Brink die Technik erst bei 7 nm.

Zur News: ASML: EUV-Lithografie erst ab 7 nm in Serie

Präsident und CTO des niederländischen Fabrikausrüsters ASML, die aktuellen Fortschritte bei der anstehenden EUV-Lithografie erläutert. In der Serienfertigung erwartet Brink die Technik erst bei 7 nm.

Zur News: ASML: EUV-Lithografie erst ab 7 nm in Serie