Winder schrieb:

... Dir ist hoffentlich klar, das heutige Prozessoren nichts mehr mit RISC und CISC zu tun haben.

Die sind vor allem eines "Superskalar" ...

Das kommt drauf an, wie eng man den Begriff RISC fasst. Fasst man ihn sinnvoll etwas weiter, nämlich so, dass das "reduced" in RISC lediglich bedeutet, dass alle Befehle der ISA die gleiche Länge haben, dann existiert dieser Unterschied nach wie vor genauso wie eh und je. Und das macht gerade

mit den Decodern einen erheblichen Unterschied im Stromverbrauch, weil das Übersetzen der x86-Befehle durch die variable Länge dieser wesentlich aufwändiger zu implementieren ist, also aufwändigere, mehr Strom verbrauchende Decoder voraussetzt. Die Hoffnung der x86-Welt bestand ein Jahrzehnt lang auf der Argumentation, dass man ja mit immer mehr Kernen immer weniger Prozent der Transistormasse für die Decoder brauchen würde - was aber nur funktioniert, wenn eben nicht jeder Kern seinen eigenen Decoder bekommt und es gibt genau zwei x86-Designs, die das umgesetzt haben: AMD Bulldozer und Piledriver. Was daraus geworden ist, sieht man an Steamroller (Kaveri, Berlin) - Pustekuchen. Warum Intel dennoch besser ist in Leistung pro Watt? Weil Fertigungsprozess und andere Designentscheidungen den Stromverbrauch ebenfalls beeinflussen. Das heißt aber eben nicht, dass der negative Einfluss des Decoders nicht existieren würde. Er ist nur bei der derzeitigen Marktlage mit Intels Fertigungsvorsprung nicht offensichtlich.

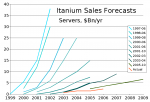

Nichtsdestotrotz spielt die Frage RISC vs. CISC beim Itanium keine große Rolle. Hier gehts

vielleicht um sowas wie, dass vor zehn Jahren, als die Modelle noch nicht von Intel mit veralteter Fertigung herausgebracht wurden, die Marketingabteilungsleiter nicht verstanden, dass eine geringere RAM-Bandbreite dann kein Nachteil ist, wenn ein Prozessor weniger mit dem RAM kommunizieren muss, weil er ein riesiges Registermonster ist, das wesentlich mehr im Rechenwerk speichern kann als die x86-Prozessoren. Itanium hätte sich lohnen können, wurde aber die letzten zehn Jahre nicht ernsthaft gefördert und der Markt für Nicht-86 ist offensichtlich zu klein für mehr als Power, z, Sparc.