Hi

ich versuche hier mal SOI und Strained Silicon zu beschreiben.

SOI

SOI bedeutet das reines Silizium auf einer Siliziumdioxid schicht drauf ist.

Im Bild sieht man das grob dargestellt. Das rote ist SiO2 und das Schwarze ist Silizium.

Hier im zweiten Bild ist dargestellt wo die bauelemte dann sind. die zerstückelte dünne schicht Si sind die bauelemte.

Zur Herstellung.

Es gibt grob gesagt nur 2 herstellungsverfahren.

1. man benutzt zwei wafer, der eine wird an der oberfläche Oxidiert und dann auf den

anderen "geklebt". In der halbleiterindustrie sagt man bonden dazu. Beim bonden passiert nichts weiter als das durch elementare kräfte diese beiden wafer zu einen werden.

Da jetzt aber die SiO2 schicht zu weit im wafer liegt muss das Si von einer seite Entfernt werden. Dies geschieht etweder durch abschleifen (MCP) oder durch Smart-Cut.

2. Man nimmt einen Wafer. In diesen Wafer wird Sauerstoff iplantiert. Dies geschieht mit hilfe von Ionenimplanter. Sauerstoffionen mit einer gewissen energie dringen in den wafer eine bestimmte tiefe ein. diese Tiefe ist relativ gut einstellbar. dadurch wird aber jetzt die kristallstrucktur der durchdrungenden schicht zerstört. Um wieder eine monokristalline struktur zu ereichen wird der ganze Wafer erwärmt, diesen Schritt nennt man heilen. außerdem entsteht auch das SiO2 mit diesen schritt.

Vor UND Nachteile von SOI

Vorteile

Durch die vollständige Isolierung von den bauelemten untereinander, gibt es keine ungewollten PNP/NPN Transistoren, Feldeffekttransitoren und keine Tyristoren. Damit wird auf diesen gebiet die entwicklung leichter. Die Leckströme sinken nur marginal, weil der haupteil des leckstroms im transistor selber fließt.

Nachteile

Der gravierenste Nachteil ist die extrem geringe Wärmeleitfähigkeit des SiO2. Da der Prozessor immer von der rückseite des wafer gekühlt wird muss die ganze wärme durch die SiO2 schicht. Diese wirk jetzt aber wie eine Isolierschicht.

So um hier noch ein paar grundlegende Begriffe zu klären.

Monokristallin, bedeutet das Im kompletten wafer nur eine ausrichtung des kristalls entsteht. bei Silizium heist das im ganzen wafer eine regelmäsige würfelstruktur entsteht.

Polykristallin bedeutet das zwar im kleinen bereichen "körner" genannt noch alles monokristallin ist, die "körner" haben aber untereinander immer eine andere ausrichtung.

Amorph ist ein stoff wenn er keine erkennbare ausrichtung hat, nichtmal in kleinen bereichen.

Silizium im Wafer ist Monokristallin meist mit der Ausrichtung 110 (millersche Indexes). Siliziumdioxid ist Amorph.

kommen wir zum Strained Silicon.

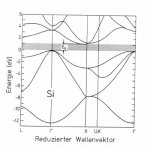

Die meisten wissen ja das Strained Silicon, bedeutet gestrecktes Silizium. Hergestellt wird es indem auf einen Silizium Germanium Wafer, Silizium epitaktisch (Heist Monokristallin) aufgewachsen wird. Germaniumatome sind größer als Siliziumatome, das bedeutet das die kristallkonstante von einem Silizium Germanium Gemisches größer ist, als die von reinen Silizium. Durch das epitaktisch Aufwachsen von Silizium auf diesen Wafer orinentiert sich jetzt das aufgewachsend Silizium an der unteren Kristallstruktur.

Die roten Punkte sind Siliziumatome und die blauen sind Germaniumatome.

Vorteile und Nachteile

Vorteil

Gestrecktes Silizium leitet besser wie wie normales Silizium, das heist man kann die kernspannung senken.

Nachteil

Ist teurer wie Normaler Wafer. Ich schätze der Leckstrom steigt wenn die kernspannung gleich bleibt. Da aber der großteil des Leckstromes immernoch durch das schalten der komplementären transistoren geschiet wird im gesamten der Leckstrom weiter sinken.

Kombinieren kann man nun beide verfahren nicht, man kann also keinen reinen SS SOI Wafer bauen. Denn um das gestreckte Silizium beizubehalten muss eine Si-Ge-Schicht darunter sein, Diese schicht wird aber nicht für die bauelemente benutzt. Bei SOI reichen die bauelemente aber bis runter zur SiO2 schicht.

Bevor ich es vergesse, ich weiß das meine rechtschreibung nicht so gut ist, also beschwert euch darüber nicht. und wenn noch einer fragen hat, fragt einfach.

ich versuche hier mal SOI und Strained Silicon zu beschreiben.

SOI

SOI bedeutet das reines Silizium auf einer Siliziumdioxid schicht drauf ist.

Im Bild sieht man das grob dargestellt. Das rote ist SiO2 und das Schwarze ist Silizium.

Hier im zweiten Bild ist dargestellt wo die bauelemte dann sind. die zerstückelte dünne schicht Si sind die bauelemte.

Zur Herstellung.

Es gibt grob gesagt nur 2 herstellungsverfahren.

1. man benutzt zwei wafer, der eine wird an der oberfläche Oxidiert und dann auf den

anderen "geklebt". In der halbleiterindustrie sagt man bonden dazu. Beim bonden passiert nichts weiter als das durch elementare kräfte diese beiden wafer zu einen werden.

Da jetzt aber die SiO2 schicht zu weit im wafer liegt muss das Si von einer seite Entfernt werden. Dies geschieht etweder durch abschleifen (MCP) oder durch Smart-Cut.

2. Man nimmt einen Wafer. In diesen Wafer wird Sauerstoff iplantiert. Dies geschieht mit hilfe von Ionenimplanter. Sauerstoffionen mit einer gewissen energie dringen in den wafer eine bestimmte tiefe ein. diese Tiefe ist relativ gut einstellbar. dadurch wird aber jetzt die kristallstrucktur der durchdrungenden schicht zerstört. Um wieder eine monokristalline struktur zu ereichen wird der ganze Wafer erwärmt, diesen Schritt nennt man heilen. außerdem entsteht auch das SiO2 mit diesen schritt.

Vor UND Nachteile von SOI

Vorteile

Durch die vollständige Isolierung von den bauelemten untereinander, gibt es keine ungewollten PNP/NPN Transistoren, Feldeffekttransitoren und keine Tyristoren. Damit wird auf diesen gebiet die entwicklung leichter. Die Leckströme sinken nur marginal, weil der haupteil des leckstroms im transistor selber fließt.

Nachteile

Der gravierenste Nachteil ist die extrem geringe Wärmeleitfähigkeit des SiO2. Da der Prozessor immer von der rückseite des wafer gekühlt wird muss die ganze wärme durch die SiO2 schicht. Diese wirk jetzt aber wie eine Isolierschicht.

So um hier noch ein paar grundlegende Begriffe zu klären.

Monokristallin, bedeutet das Im kompletten wafer nur eine ausrichtung des kristalls entsteht. bei Silizium heist das im ganzen wafer eine regelmäsige würfelstruktur entsteht.

Polykristallin bedeutet das zwar im kleinen bereichen "körner" genannt noch alles monokristallin ist, die "körner" haben aber untereinander immer eine andere ausrichtung.

Amorph ist ein stoff wenn er keine erkennbare ausrichtung hat, nichtmal in kleinen bereichen.

Silizium im Wafer ist Monokristallin meist mit der Ausrichtung 110 (millersche Indexes). Siliziumdioxid ist Amorph.

kommen wir zum Strained Silicon.

Die meisten wissen ja das Strained Silicon, bedeutet gestrecktes Silizium. Hergestellt wird es indem auf einen Silizium Germanium Wafer, Silizium epitaktisch (Heist Monokristallin) aufgewachsen wird. Germaniumatome sind größer als Siliziumatome, das bedeutet das die kristallkonstante von einem Silizium Germanium Gemisches größer ist, als die von reinen Silizium. Durch das epitaktisch Aufwachsen von Silizium auf diesen Wafer orinentiert sich jetzt das aufgewachsend Silizium an der unteren Kristallstruktur.

Die roten Punkte sind Siliziumatome und die blauen sind Germaniumatome.

Vorteile und Nachteile

Vorteil

Gestrecktes Silizium leitet besser wie wie normales Silizium, das heist man kann die kernspannung senken.

Nachteil

Ist teurer wie Normaler Wafer. Ich schätze der Leckstrom steigt wenn die kernspannung gleich bleibt. Da aber der großteil des Leckstromes immernoch durch das schalten der komplementären transistoren geschiet wird im gesamten der Leckstrom weiter sinken.

Kombinieren kann man nun beide verfahren nicht, man kann also keinen reinen SS SOI Wafer bauen. Denn um das gestreckte Silizium beizubehalten muss eine Si-Ge-Schicht darunter sein, Diese schicht wird aber nicht für die bauelemente benutzt. Bei SOI reichen die bauelemente aber bis runter zur SiO2 schicht.

Bevor ich es vergesse, ich weiß das meine rechtschreibung nicht so gut ist, also beschwert euch darüber nicht. und wenn noch einer fragen hat, fragt einfach.