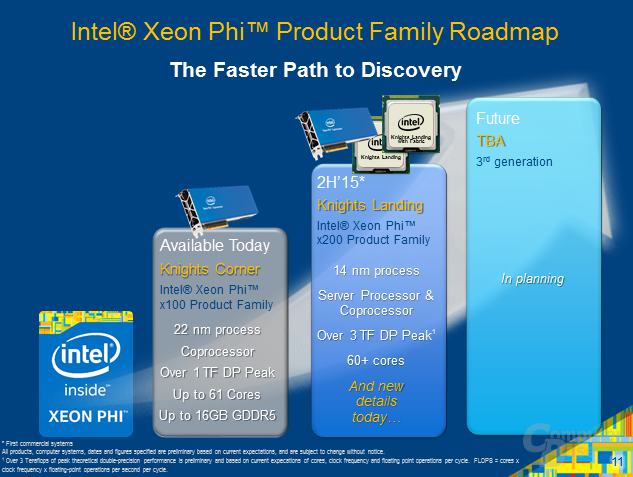

Xeon Phi „Knights Landing“ mit 72 Kernen und On-Package DRAM

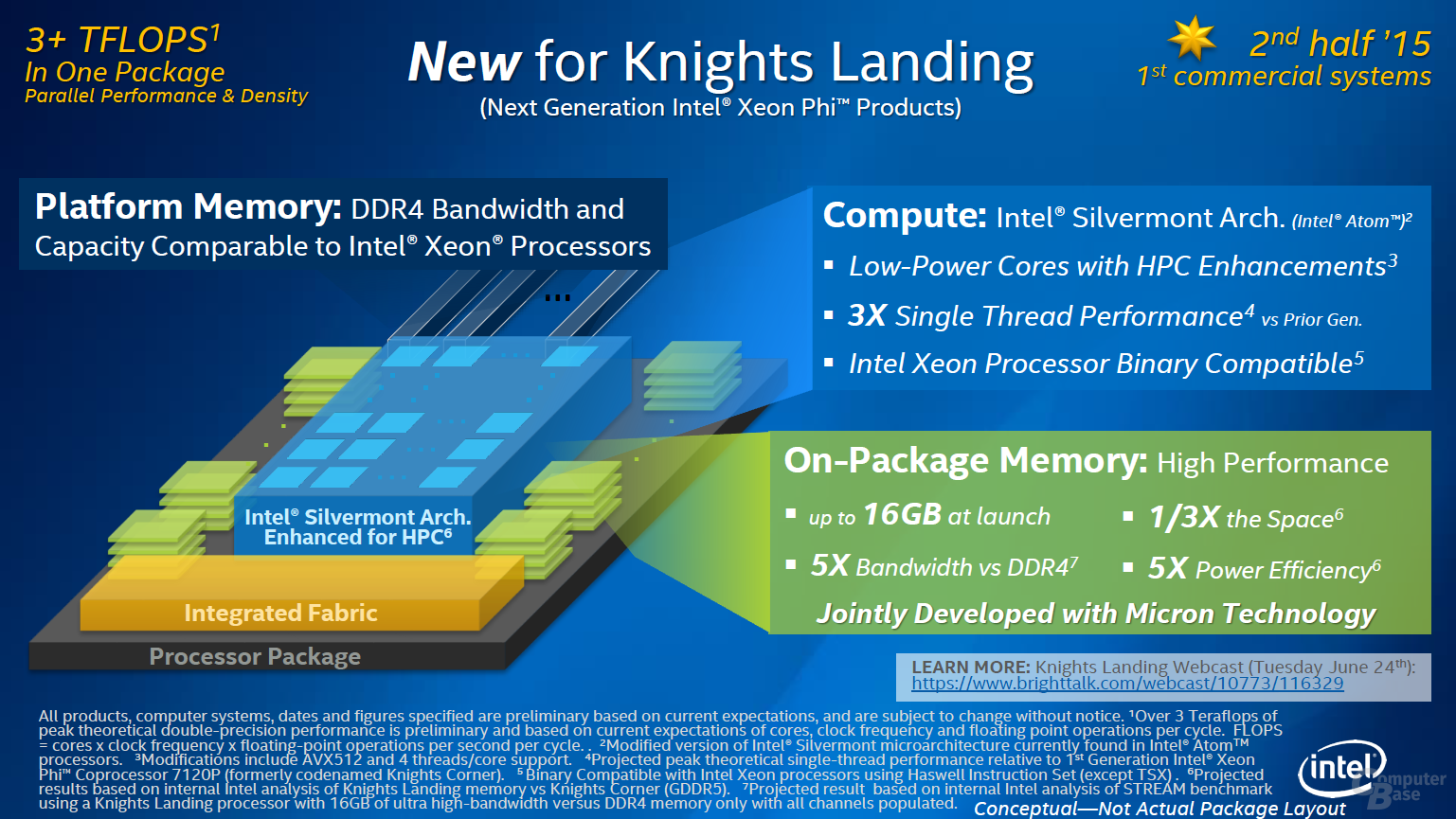

Zum Auftakt der ISC 2014 in Leipzig hat Intel einige Details zum zukünftigen Ableger der Xeon Phi mit dem Codenamen „Knights Landing“ preisgegeben. Der neue HPC-Chip setzt auf eine verbesserte „Silvermont“-Architektur, die unter anderem aus einem Kern vier Threads bereitstellt, hinzu kommt sehr schneller On-Package DRAM.

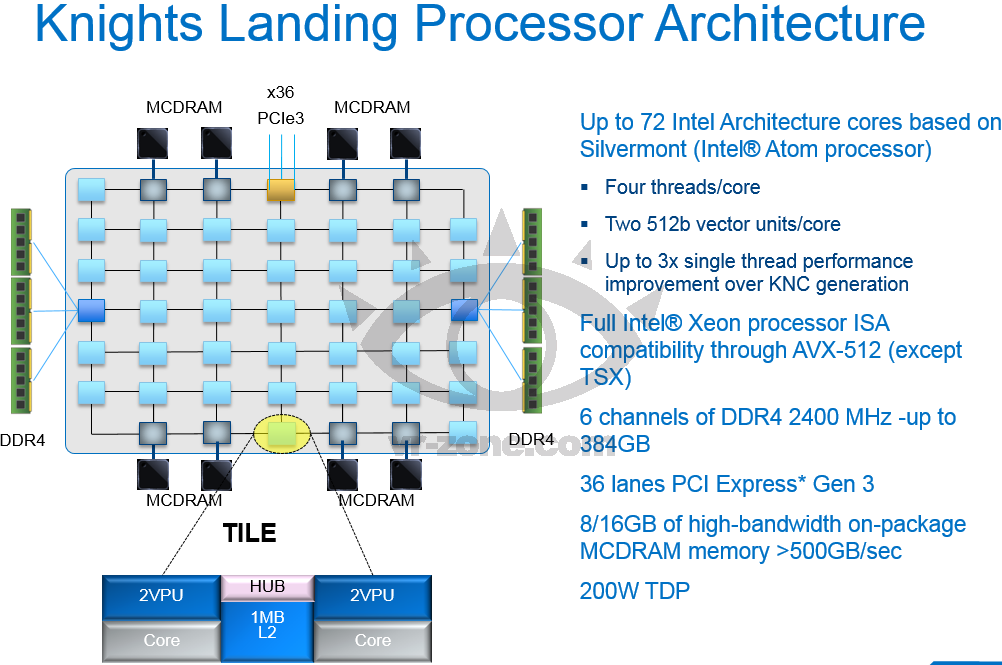

Beim Speicher will Intel derzeit aber noch nicht verraten, welche Lösung zum Einsatz kommt, da „Knights Landing“ erst im zweiten Halbjahr 2015 an Kunden ausgeliefert werden soll. Die angegebenen hohen Leistungswerte bei geringer Leistungsaufnahme sowie die Zusammenarbeit mit Micron lassen die Vermutung auf die Verwendung von Hybrid Memory Cube zu, was Intel vorab jedoch weder bestätigen noch dementieren wollte. Durchgesickerte Folien sprechen von MCDRAM, was für Memory Cube DRAM stehen könnte.

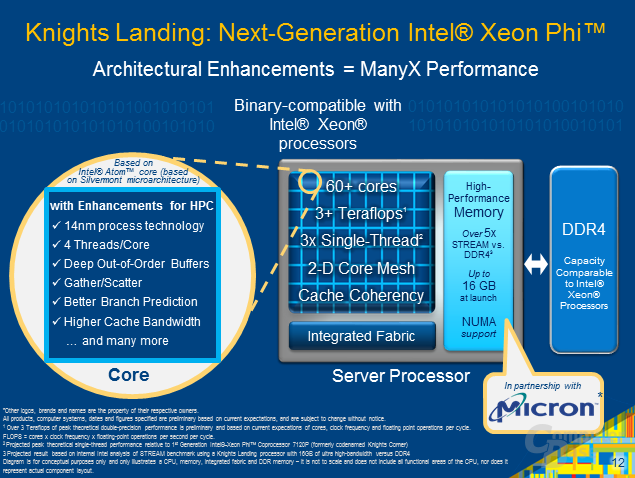

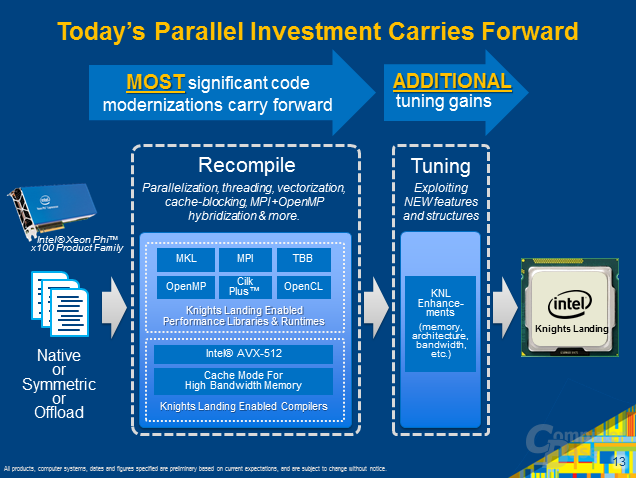

Zu den bereits teilweise bekannten, aber nun noch einmal etwas genauer definierten Tatsachen zählt die zugrundeliegende Architektur. Die aktuell von den Atom-CPUs der „Bay Trail“-Serie bekannten „Silvermont“-Kerne wertet Intel in Richtung HPC auf und verbaut diese als Ablöse der Uralt-Pentium-Kerne aus der ersten Xeon-Phi-Serie „Knights Corner“. Statt einem Thread pro Kern kommen so vier zustande, was bei spekulierten 72 Kernen satte 288 Threads bedeutet. Gleichzeitig werden Features wie AVX-512 unterstützt, wofür die integrierten Pipeline-Stufen deutlich ausgebaut werden müssen. Hand angelegt werden muss auch an dem Speicherinterface, denn das Atom-Segment stellt nicht ansatzweise die Bandbreite zur Verfügung, die „Knights Landing“ bieten soll. Mit bis zu 16 GByte On-Package DRAM und einer zusätzlichen Anbindung für bis zu 384 GByte DDR4-Speicher fällt dieser Bereich deutlich umfangreicher aus.

Die von Intel prognostizierten Leistungsdaten im Vergleich zum Vorgänger zeigen deutliche Zugewinne. Die Double-Precision-Leistung soll bei über 3 TFLOPS liegen, die reine CPU-Leistung in der Spitze um das Dreifache ansteigen. Die Vorteile des neuen Speichers sowie deren Anbindung sollen sich massiv auswirken.

Mit „Omni Scale“ kommt auch eine neue Generation Fabric zum Einsatz. Diese basiert auf der Zusammenarbeit mit Cray und QLogic und soll das komplette Programm von einfachen Adaptern, Switches über Kabel bis hin zur passenden Software umfassen. In den director switches wird Intel zudem erstmals auf die „Silicon Photonics“-Lösung zurückgreifen. Echte Details zu all dem sind aber noch Mangelware.

Intels Vorhaben hat aber auch eine Kehrseite: Damit der Die des neuen Xeon Phi nicht auf eine riesige Größe wächst und gleichzeitig die Leistungsaufnahme ausufert, ist Intel bei den „Knights Landing“ auf die 14-nm-Fertigung angewiesen. Diese bereitet Intel derzeit aber selbst mit den kleinen „Broadwell“-Chips (rund 150 mm² Die-Fläche) ihre Probleme, sodass bei riesigen „Knights Landing“-Chips (vermutet werden knapp 700 mm² wie bei beiden Vorgängern) die Yield-Rate und damit die Ausbeute an perfekten Chips massiv fallen würde. Auch deshalb gibt sich Intel noch mehr als ein Jahr Zeit, um „Knights Landing“ im zweiten Halbjahr 2015 zusammen mit „Broadwell-EP“ in der 14-nm-Fertigung präsentieren zu können.

Gegenüber EETimes bestätigte Micron die Nutzung von Hybrid Memory Cube für Intels „Knights Landing“. Der Speicher wird laut Micron dabei so schnell und für Programmierer dennoch einfach zu adressieren sein, dass er quasi als bis zu 16 GByte großer L3-Cache gesehen werden kann.

Am heutigen Abend hat Intel weitere kleine Details der Xeon Phi x200 als Nachfolger der aktuellen Xeon Phi 7100 offenbart. Dabei betonte der Hersteller, dass die genutzten „Silvermont“-Cores nicht mehr viel mit dem gemein haben werden, was aktuell bei „Bay Trail“ & Co zum Einsatz kommt. Dies beginnt bei einer überarbeiteten Sprungvorhersage und geht über die zusätzlichen Threads pro Kern bis hin zur neuen Cache-Hierarchie. Dabei bestätigte Intel, was Micron gestern bereits bekannt gab: Der On-Package DRAM kann mittel „Cache Mode“ so konfiguriert werden, dass er quasi als L3-Cache funktioniert.

Am Ende wird auch das neue Package eine Rolle spielen. Denn im sockelbaren Design wie die klassischen Xeon-Prozessoren werden sich Platzvorteile ergeben, sodass statt bisher maximal zwei „Knights Corner“-Lösungen in einem schmalen 1U-Rack drei oder noch mehr Lösungen verbaut werden können. Zusammen mit der deutlich gesteigerten Leistung soll der Weg zum Exascale-Supercomputer zum neuen Jahrzehnt einen großen Schritt vorangehen. Der nächste ist bereits geplant.