Xeon Phi: Intel bestätigt 72 Kerne für Knights Landing

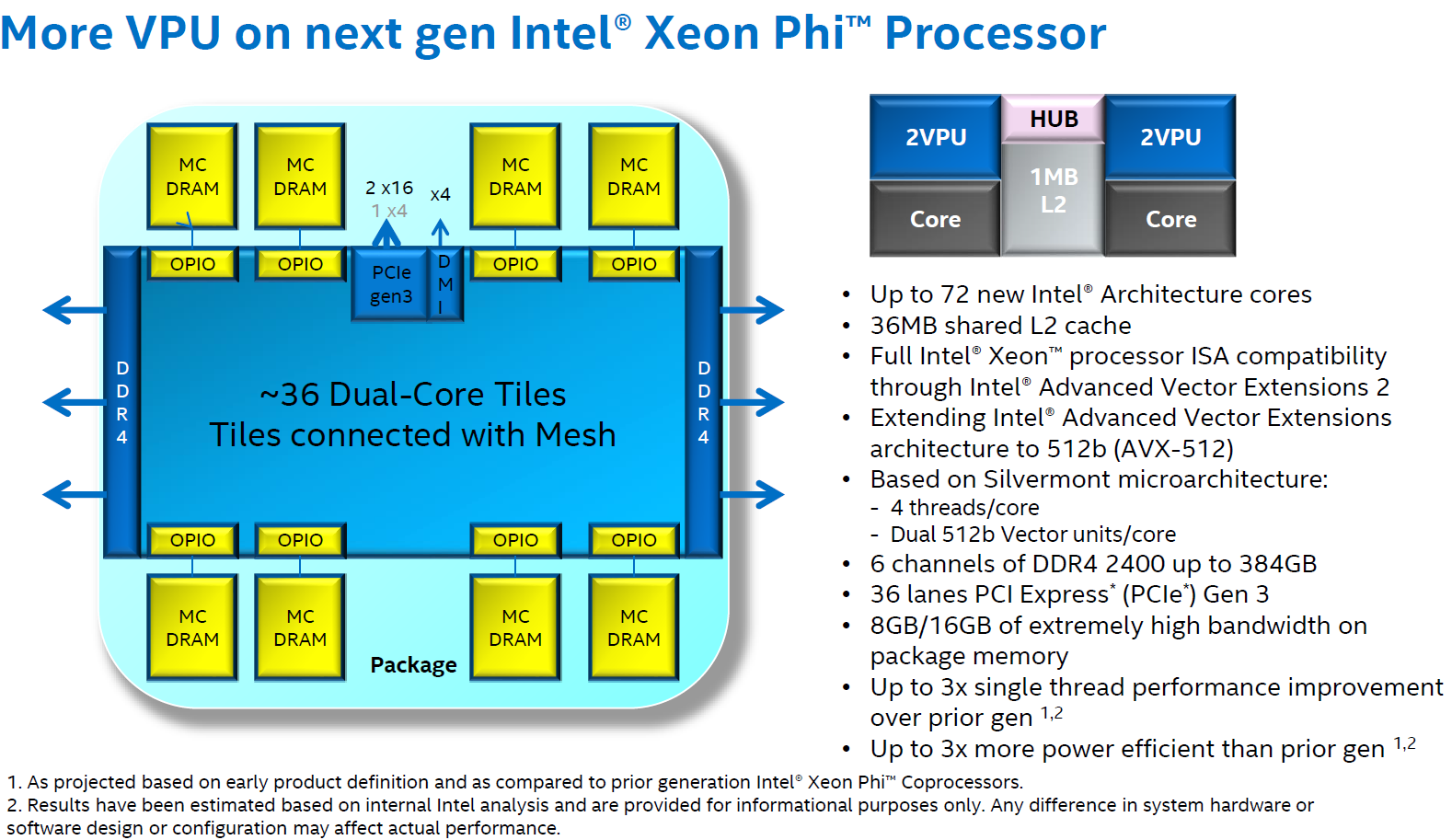

Monatelang ist Intel um die maximale Anzahl der Kerne beim neuen Xeon Phi herum gesprungen und gab diplomatisch lediglich „mehr als 60“ an. Zum IDF 2015 in Shenzen rückt der Hersteller nun mit der finalen Zahl heraus, die seit dem Jahr 2013 bereits vermutet wurde: 72 Kerne und 36 MByte L2-Cache wird das Flaggschiff bieten.

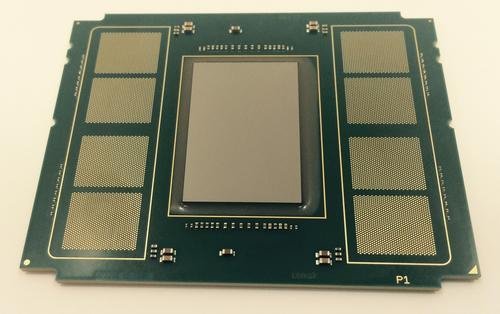

Die Basis für die neuen Xeon Phi ist die 14-nm-Fertigung, ohne die das Produkt nicht aufgelegt werden könnte. Die maximal 72 Kerne, 36 MByte L2-Cache, 36 PCI-Express-Lanes sowie ein Sechs-Kanal-Speicherinterface mit der Unterstützung für DDR4-2400 fördern einen Die zutage, der bei 7,2 oder 8,0 Milliarden Transistoren mit Fabric rund 700 mm² groß ist. Um den Die selbst werden die bis zu acht Speicherchips von Micron auf dem gleichen Package untergebracht. Es handelt sich um HMC-Speicher (Hybrid Memory Cube), der mit Kapazitäten von 8 oder 16 GByte eine sehr hohe Bandbreite bei geringen Latenzen bietet.

Die 72 Kerne basieren in der Basis auf der Silvermont-Architektur, wurden jedoch massiv angepasst. Dazu zählt unter anderem ein angepasster L1-Cache, der für Daten von 24 auf 32 KByte ausgebaut wurde und damit mit dem L1I-Cache gleichzieht. Die aufgewertete Variante der Silvermont-Kerne bietet bei Knights Landing zudem satte vier Threads pro Kern statt bisher einen. Darüber hinaus unterstützt der Neuling auch AVX-512 als neueste, bisher höchste Ausbaustufe dieser Instruktionen – und exklusiv für Xeon Phi. Zwei dieser Kerne teilen sich wie bisher auch ein L2-Cache-Paket in Größe von einem Megabyte und bilden zusammen mit zwei VPUs (Vector Processing Unit) und einem Hub für die Kommunikation mit den anderen Dual-Core-Paketen eines der 36 Tiles.

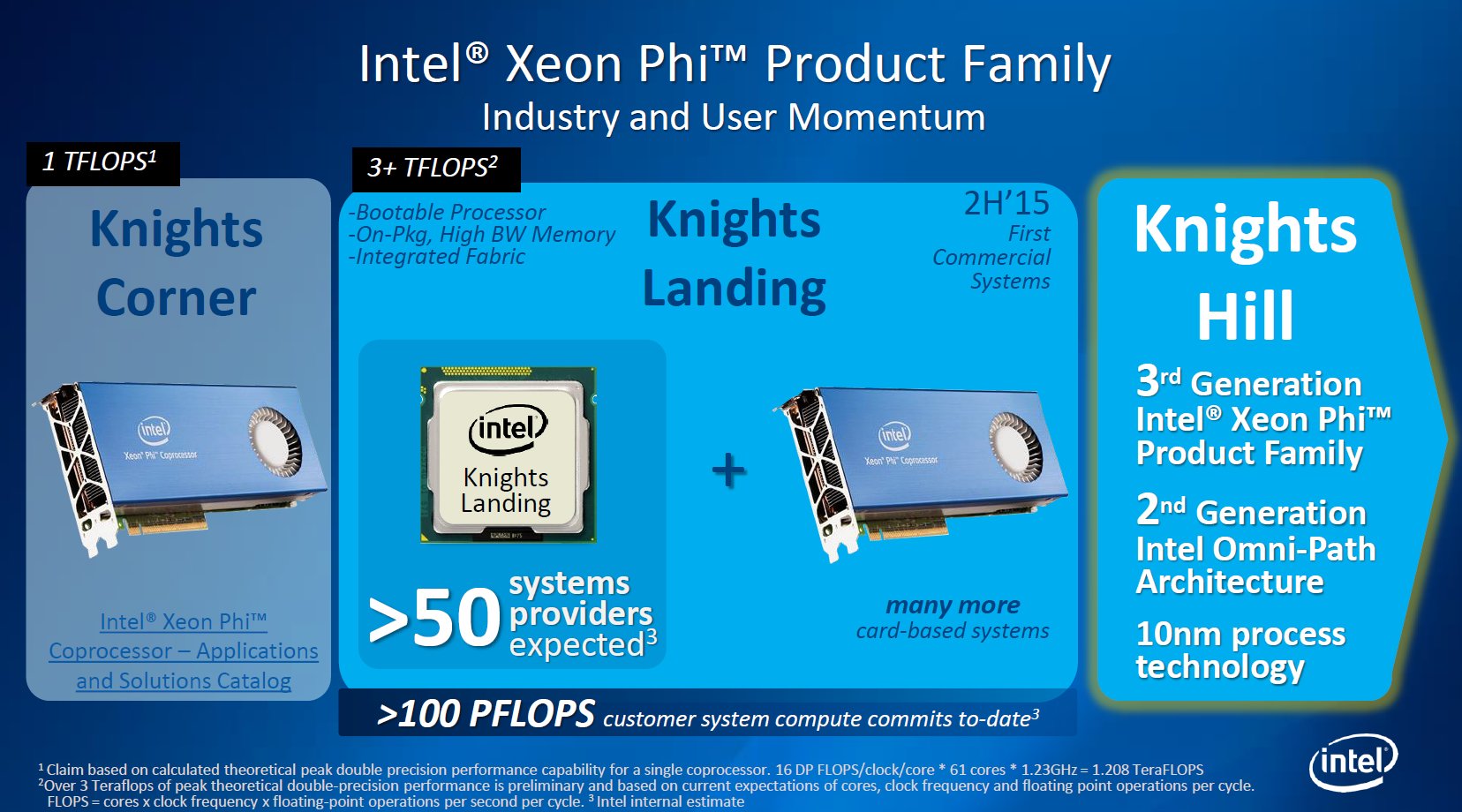

Insgesamt drei Varianten von Knights Landing wird Intel ab dem zweiten Halbjahr dieses Jahres anbieten. Das klassische Produkt des Co-Prozessors via PCI-Express-Slot ist die erste Variante, gefolgt von gesockelten, bootbaren Prozessoren. Diese wiederum sind noch einmal unterteilt, die erste Variante ohne integrierte Fabric, die zweite als Vollausbau mit Intels Omni Path. Omni Path wird in Zukunft bei Intel eine große Rolle spielen, denn nicht nur die Xeon Phi sollen darauf setzen, sondern auch die klassischen Xeon-Server-Prozessoren. Erwartet wird die Verschmelzung bei Skylake-EP/EX. Intels Xeon Phi wird in der Zwischenzeit auch weiterentwickelt, bereits jetzt arbeitet Intel an Knights Hill, dem Nachfolger in 10-nm-Fertigung.