Phase-Change Memory: Funktionsfähiger TLC‑PCM mit 3 Bit von IBM Research

Seit vielen Jahren wird an Phasenwechselspeicher, geläufiger unter dem englischen Namen Phase-Change Memory (PCM), geforscht. Ein Teilziel ist die Speicherung von mehreren Bit pro Zelle, um die Speicherdichte zu erhöhen. IBM-Forschern ist es gelungen, erstmals drei Datenbit pro Zelle zuverlässig zu sichern und zu erhalten.

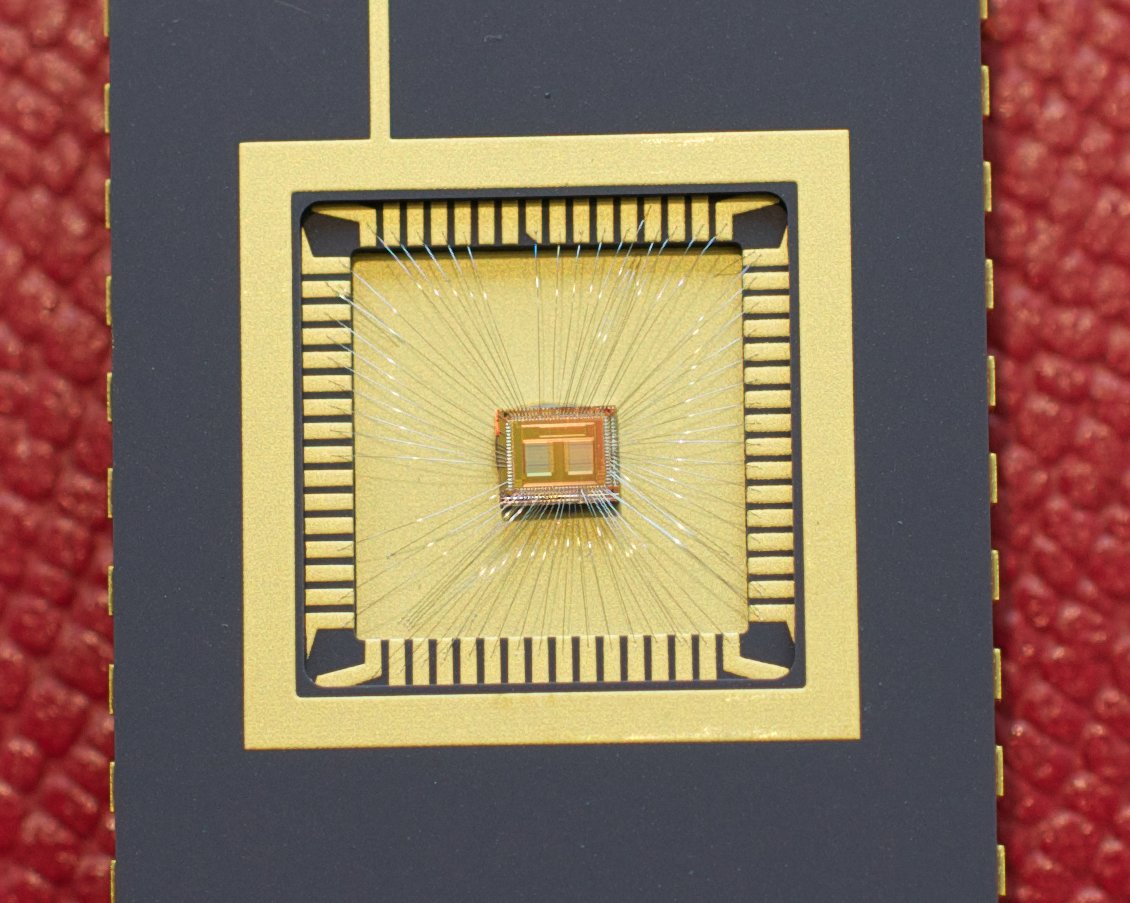

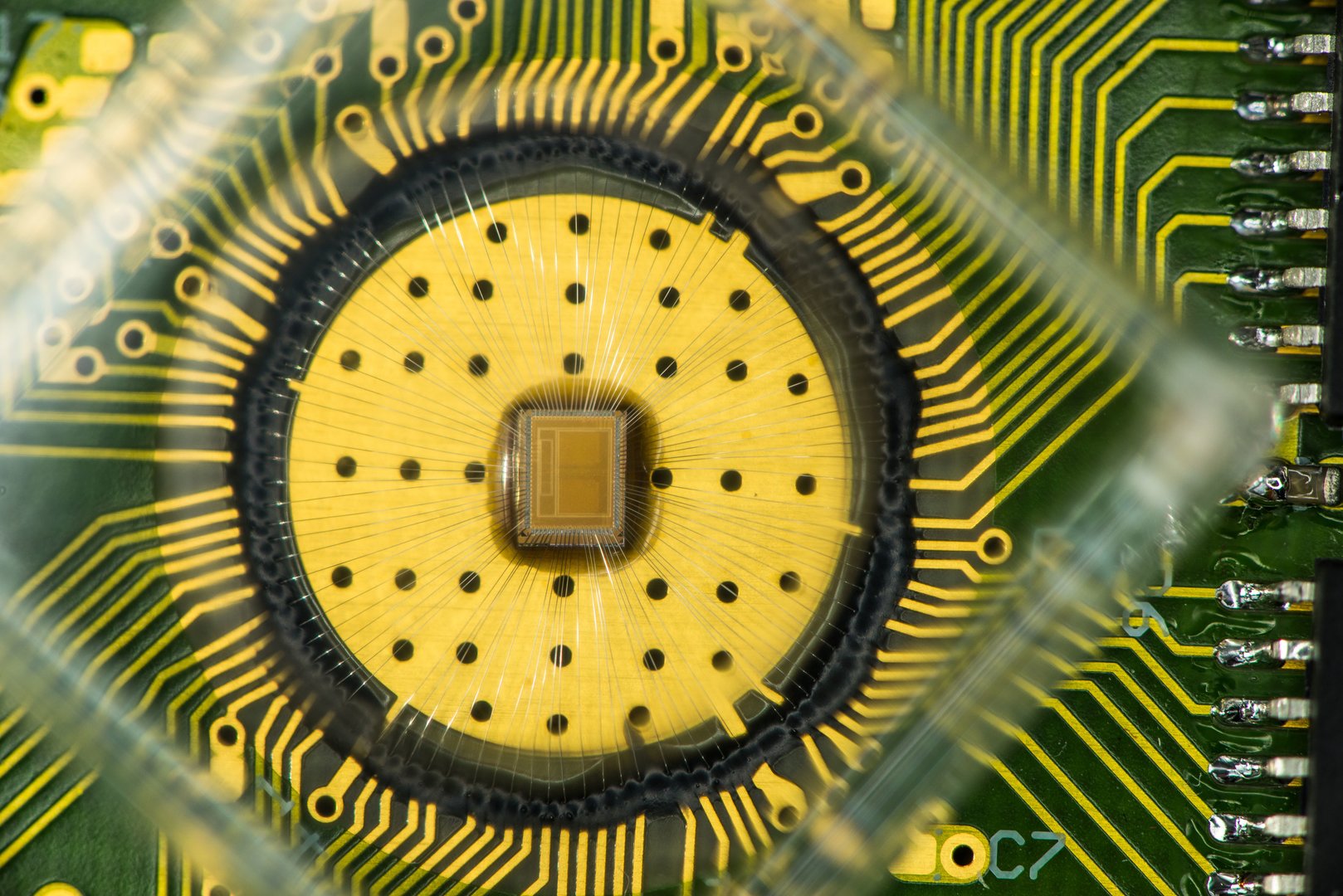

Bereits 2011 hatte IBM Research Fortschritte im Bereich des Multi-Level-Cell-PCM verkündet und erstmals über einen längeren Zeitraum zwei Bit pro Speicherzelle sichern können. Fast fünf Jahre später folgt der erste Triple-Level-Cell (TLC) Phase-Change Memory. Der Prototyp besteht aus zwei Bereichen (arrays) mit je zwei Millionen Zellen, die jeweils drei Datenbit speichern können. Daraus resultiert eine Gesamtkapazität von 12 Megabit.

Auf Nachfrage wies Dr. Haris Pozidis, der Manager der Forschungsgruppe von IBM Research – Zürich, darauf hin, dass es sich dabei um einen experimentellen Testballon handelt. Serienreife Chips sollten später eine weitaus höhere Speicherkapazität vorweisen. Der Test-Chip besitze eine Größe von 2 × 1.000 μm × 800 μm, einer der beiden Zellenbereiche ist damit lediglich 0,8 mm² groß.

Gefertigt wurde der Prototyp in einem 90-nm-CMOS-Verfahren in der IBM Burlington fab, die inzwischen zu Globalfoundries gehört.

Wie bei Flash bedeutet TLC auch Nachteile

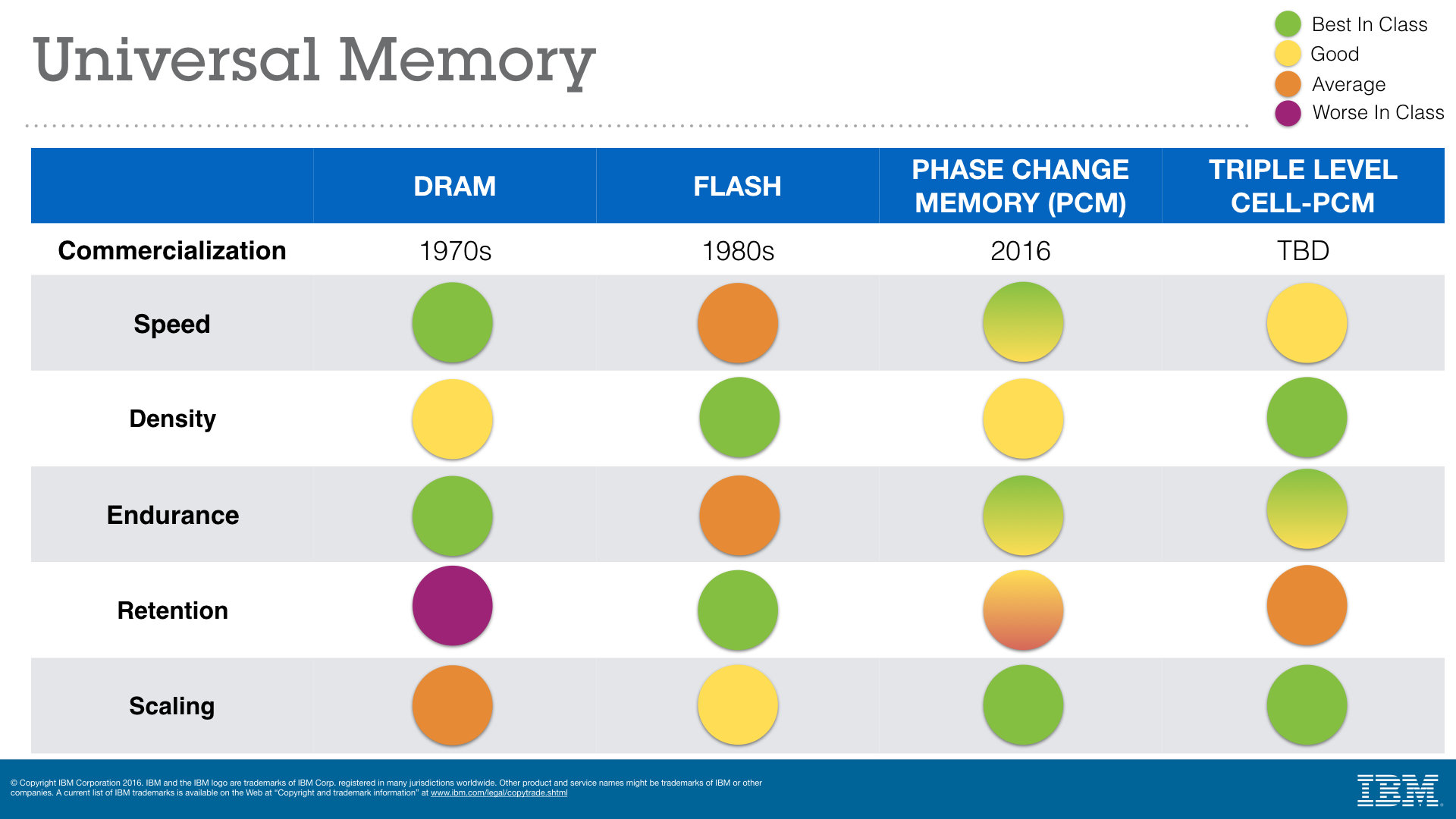

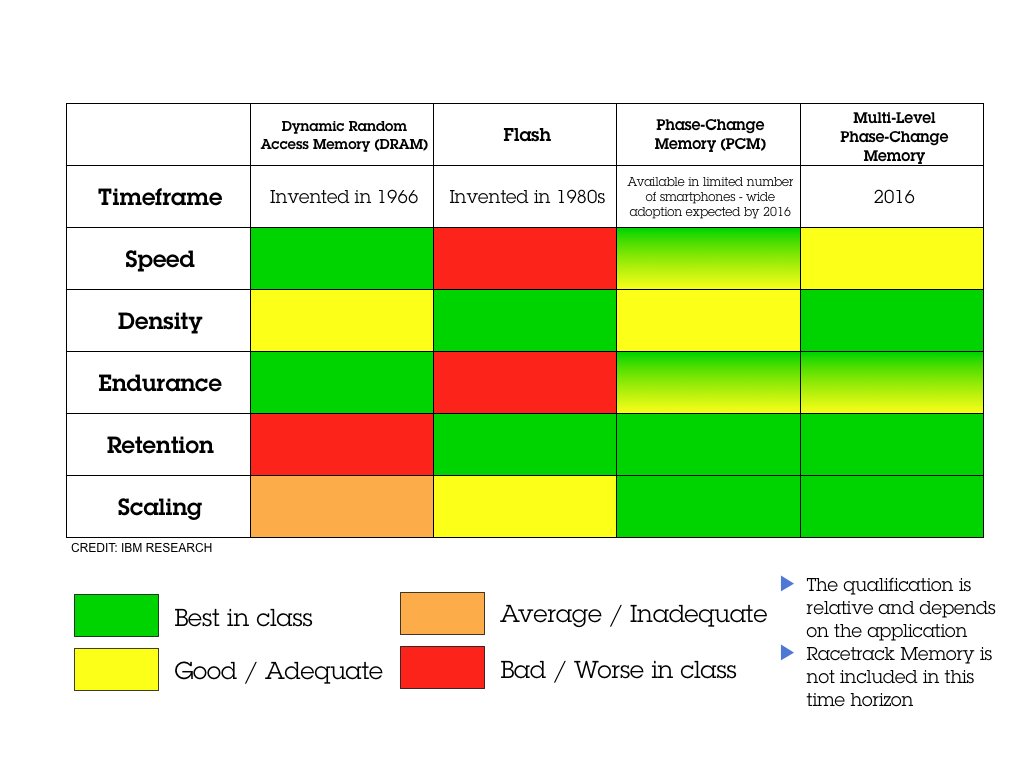

Wie bei NAND-Flash bedeutet der Wechsel auf TLC nicht nur den Vorteil der höheren Speicherdichte und damit reduzierten Kosten pro Bit. Die Unterscheidung zwischen acht verschiedenen Widerstandswerten macht das Lesen und Schreiben aufwendiger gegenüber 2-Bit-MLC (vier Widerstände) und SLC mit nur einem Bit (zwei Widerstände). Bei IBMs Vergleichsschema mit verschiedenen Speichertechnologien wird dies daran deutlich, dass sich TLC-PCM bei der Datendichte (Density) zwar verbessert, bei der Geschwindigkeit (Speed) aber niedriger eingestuft ist.

In der aktuellen Presseaussendung von IBM Research heißt es, dass neue Verfahren die als Resistance Drift umschriebene schleichende Veränderung des Zellzustandes verhindern. Dazu wurden Maßnahmen ergriffen, um die Schwellwerte konstant zu halten und dem Drift entgegen zu wirken. „Somit kann der Zellzustand zuverlässig auch nach Ablauf einer beträchtlichen Zeit seit der Programmierung des Speichers ausgelesen werden. Der Speicher ist also nichtflüchtig“, wird in der IBM-Mitteilung erklärt.

Dennoch schneidet TLC-PCM beim Datenerhalt (Retention) laut der aktualisierten Grafik schlechter als herkömmlicher PCM ab. In der Grafik von 2011 hatte es bei der Retention keine Unterschiede zwischen Single-Bit-PCM und Multi-Bit-PCM gegeben.

Die durch die Zahl der möglichen Schreibzyklen bestimmte Haltbarkeit (Endurance) hat laut der Grafik nicht abgenommen. Im damaligen Bericht zu Multi-Bit-PCM war von mindestens 10 Millionen Schreibzyklen die Rede. Dass bei TLC zumindest eine Million Write-Cycles möglich sind, wollen die IBM-Forscher in diesen Tagen auf dem IEEE International Memory Workshop anhand einer Speichereinheit mit 64.000 Zellen demonstrieren.

Schneller als Flash, langsamer als DRAM

Auf Nachfrage verriet Dr. Pozidis, dass MLC- und TLC-PCM typische Latenzen von 200 bis 500 Nanosekunden beim Lesen erreiche und damit erheblich schneller als NAND-Flash mit mehreren 10.000 Nanosekunden arbeite. DRAM ist mit Latenzen im einstelligen Nanosekundenbereich aber nochmals erheblich schneller.

Beim Schreiben wird insbesondere durch das TLC-Verfahren mehr Zeit benötigt, sodass die Latenz hier eine Mikrosekunde (1.000 Nanosekunden) erreiche, damit aber immer noch zigfach schneller als Flash arbeite. Die Datentransferraten sollen im Bereich von 500 bis 2.000 MB/s beim Lesen und 100 bis 500 MB/s beim Schreiben liegen. Die Datenrate hänge aber von diversen Faktoren wie der Zugriffsgranularität und der Pipeline-Fähigkeit des Chips ab. Im Verbund mehrerer Chips sind weitaus höhere Datenraten denkbar.

Funktionsweise von Phase-Change Memory

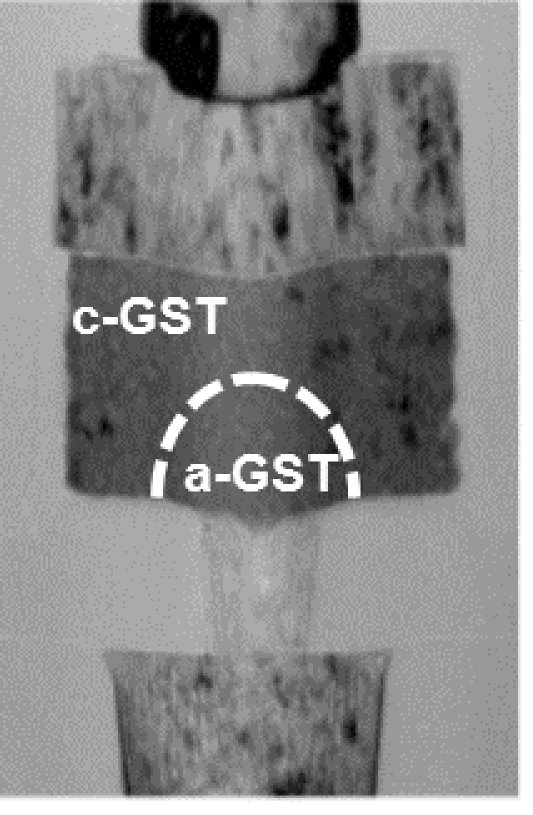

Die auch als PRAM bezeichnete PCM-Technik macht sich die Eigenschaften von Chalkogenid-Legierungen zu eigen, die bei einer bestimmten Temperatur vom kristallinen in den amorphen Zustand und umgekehrt wechselt – der sogenannte Phasenwechsel.

Die beiden Aggregatzustände bedeuten unterschiedliche elektrische Widerstände, die zur Speicherung der Informationen genutzt werden. Durch kurze Stromimpulse wird eine Aufheizung des Materials bis zum jeweiligen Temperaturschwellwert, der den Phasenwechsel einleitet, erreicht. Das Auslesen der Information erfolgt über die Ermittlung des jeweiligen Widerstandswerts. Laut IBM entspricht das Verfahren grundlegend jenem einer wiederbeschreibbaren Blu-Ray-Disk.

PCM als Universalspeicher zwischen DRAM und Flash

Derzeit wird PCM vor allem für den Einsatz als schneller Cache-Speicher erwogen. In der SLC-Variante mit einem Bit pro Zelle wird er bereits seit Jahren unter anderem für den Mobilbereich angeboten. Im Unternehmensumfeld könnten durch höhere Speicherkapazitäten vollständige Datenbanken im nicht flüchtigen und schnellen PCM vorgehalten werden, um Online-Anwendungen wie Finanztransaktionen zu beschleunigen. Der 3-Bit-PCM könnte aus Sicht der Forscher auch in den Bereichen Internet of Things, Cloud-Storage oder Smartphones Verwendung finden. Denkbar ist dabei eine Anbindung an herkömmliche DRAM-Schnittstellen (DDR3/DDR4), aber auch PCIe-Karten wären möglich.

Dr. Pozidis erklärte, dass die PCM-Technik nun „ausgereift und bereit für die Lizenzierung“ sei. Derzeit sei man auf der Suche nach Partnern zur Entwicklung und Herstellung der Chips.

„Die Fähigkeit 3 Bits pro Zelle zu speichern, ist ein wichtiger Meilenstein für PCM, denn bei dieser Speicherdichte liegen die Kosten für PCM deutlich unter denen von DRAM und viel näher an denen von Flash.”

Dr. Haris Pozidis, Manager der Non-Volatile Memory Research-Gruppe bei IBM Research – Zürich

PCM hat viel mit 3D XPoint gemein

PCM gehört zu einer der neuen Speichertechniken, die sich von der Geschwindigkeit her zwischen schnellem und teurem DRAM und langsameren aber günstigen NAND-Flash etablieren wollen. Micron hat zusammen mit Intel die PCM-Alternative 3D XPoint entwickelt, die mit Chalkogenid-Material zumindest eine Eigenschaft mit PCM gemein hat. Der Vorteil gegenüber DRAM liegt in beiden Fällen im Datenerhalt ohne Stromzufuhr (non-volatile) und niedrigeren Kosten pro Bit, die näher bei den Kosten für NAND-Flash liegen sollen.