IBM stellt Microns „Hybrid Memory Cube“ her

Microns Hybrid Memory Cube (HMC) soll in naher Zukunft die traditionellen DRAM-Module ablösen. Verglichen mit diesen ermöglicht der dreidimensionale Aufbau des Speicherwürfels viel höhere Datenübertragungsraten und verringert die Leistungsaufnahme.

Zur Einführung der ersten kommerziell verfügbaren CMOS-Technologie zum Stapeln von Chips mit TSV-Verbindungen wird IBM den Hybrid Memory Cube im Halbleiterwerk in East Fishkill, New York in 32 Nanometer Strukturbreite und mit High-k+Metal-Gate-Technik herstellen. Weitere Details zu seiner TSV-Technik, die nicht nur im HMC zum Einsatz kommen soll, will IBM am 5. Dezember auf dem IEEE Electron Devices Meeting in Washington, D. C. präsentieren. Wann genau die HMCs in Stückzahlen ausgeliefert werden, wird in der aktuellen Pressemitteilung offen gelassen. Zuletzt wurde 2013 als Jahr für die ersten kommerziellen Lösungen im Unternehmensbereich genannt.

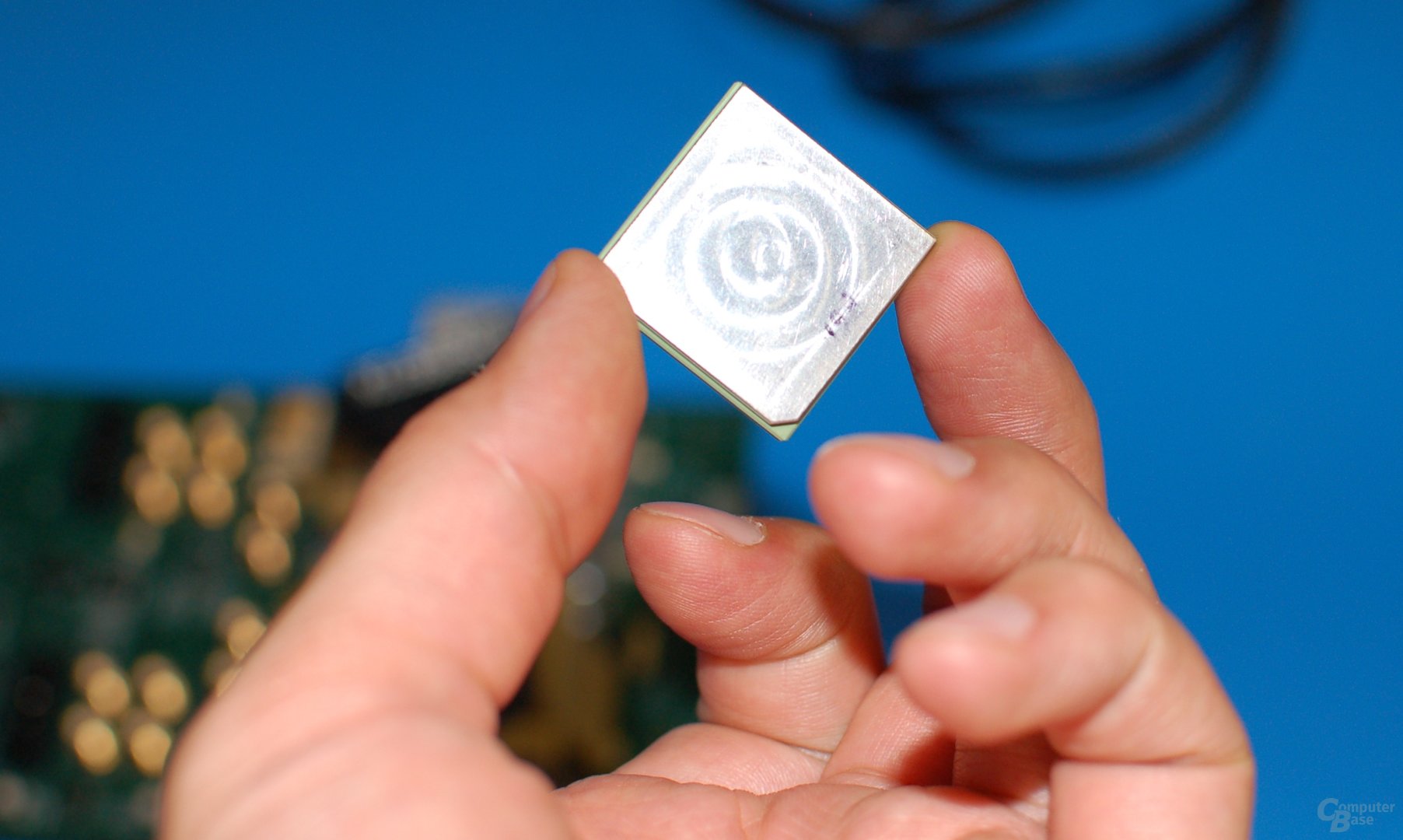

Stapel aus Logik-Chip und DRAM-Chips

Ein HMC besteht aus mehreren, übereinander gestapelten DRAM-Dies, die mit TSV-Verbindungen direkt auf einem Steuerungschip aufgesetzt werden. Solch ein „Stapel-RAM“ ist an sich nicht neu und wird zum Beispiel schon von Samsung in speziellen RDIMMs eingesetzt. Der On-Chip-Controller ist in dieser Form bisher allerdings neu und für den Schub in puncto Leistung verantwortlich.

Ein 512 MB große HMC-Prototyp, den Micron Anfang September auf dem Intel Developer Forum zeigte, erreicht eine Datenübertragungsrate von 128 Gigabyte pro Sekunde. Ein 4 GB großes DDR3-1333-Modul ist im Gegensatz dazu mit 10,66 GB/s deutlich im Hintertreffen. Auch zur Leistungsaufnahme der platzsparenden Bausteine gibt es erste Informationen. Bezogen auf die Übertragungsrate gibt Micron für den HMC 62,23 Milliwatt pro GB/s an, während das oben beschriebene Speichermodul auf 431,83 Milliwatt kommt.