Yonah mit „Smart Cache“ und Sockel 478

Im Rahmen des „Mobile Day 2005“ hat Intel am gestrigen Donnerstag in San Francisco der anwesenden Fachpresse weitere Details zum kommenden Dual-Core-Notebook-Prozessor „Yonah“ verraten, wenngleich ein Teil der Informationen der Gerüchteküche schon seit längerer Zeit bestens bekannt ist.

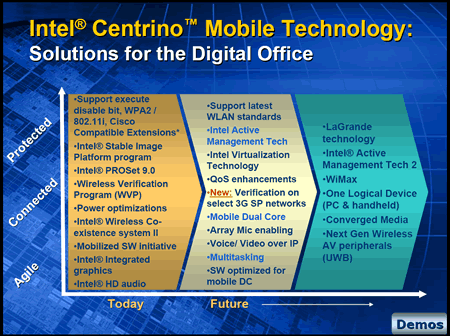

Yonah stellt als Prozessor der „Napa“-Plattform neben dem Calistoga-Chipsatz (i945GM, i945PM,i955XM, i945GMS) und dem WirelessLAN-Modul Golan (PRO/Wireless 3945ABG) einen wichtigen Grundpfeiler der dritten Centrino-Generation dar, die nun offiziell im ersten Quartal des nächsten Jahres vorgestellt werden soll. Ursprünglich hatte Intel den in 65 nm gefertigten Prozessor als Beweis der eigenen Führungsrolle im Halbleitersektor im zweiten Halbjahr 2005 präsentieren und in geringen Stückzahlen ausliefern wollen. Dabei wollten die Notebook-Hersteller nicht mitspielen, da Anfang dieses Jahr mit Sonoma vor gar nicht all zu langer Zeit erst die zweite Centrino-Generation vorgestellt worden ist. So bleibt allen Beteiligten noch mehr Zeit, die nächste Generation weiter zu perfektionieren. Bereits jetzt stehen über 120 Plattform-Designs auf Basis der Napa-Plattform zur Verfügung (bzw. befinden sich in der Entwicklung) – schätzungsweise 30 mehr als beim vergleichbaren Entwicklungsstand von Sonoma.

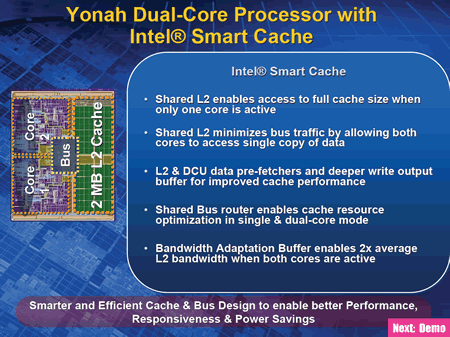

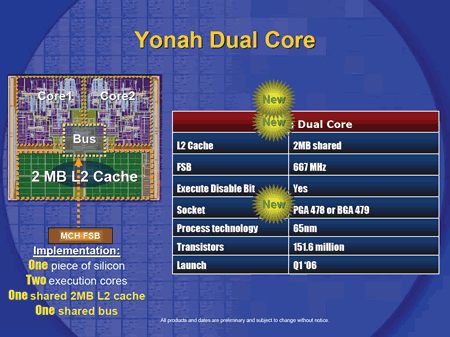

Mit dem Yonah, bzw. der Napa-Plattform, wird der Frontside-Bus von derzeit 533 MHz auf 667 MHz beschleunigt werden. Damit steigt die Bandbreite zwischen Prozessor und Speichercontroller von derzeitigen 4,2 GB/s auf 5,3 GB/s. Anders als beim Dual-Core-Prozessor Pentium D und Pentium Extreme Edition für den Desktop-Markt hat sich Intel bei der Cache-Struktur und der Bus-Anbindung etwas mehr Mühe gegeben. So wird Yonah wie AMDs Athlon 64 X2, der kommende Dual-Core Itanium 2 „Montecito“ oder Dual-Core Xeon MP „Paxville“ gegenüber der Northbridge als eine einzige Last erscheinen. Eine Logik im Prozessor, wie der Arbiter beim Montecito, sorgt bereits im Prozessor für Ordnung und reguliert den Busverkehr. Auch der L2-Cache vereint diverse Besonderheiten in sich, die ihm die Bezeichnung „Smart Cache“ einbringen. Anders als die bereits verfügbaren Dual-Core-Prozessoren von Intel oder AMD besitzt der Yonah einen einzigen, zwei Megabyte großen L2-Cache, auf den beide Prozessorkerne gemeinsam zugreifen können.

Die Konzeption geht dabei soweit, dass, sollte nur eine CPU aktiv sein, diese über den kompletten Zwischenspeicher verfügen kann; sind beide Prozessoren aktiv, wird der Cache in Abhängigkeit der jeweiligen Last aufgeteilt. Darüber hinaus ist es möglich, dass sich beide Prozessoren ein Cache-Datum teilen; ein Umweg über den Hauptspeicher entfällt und der Frontside-Bus wird entlastet. Das ist insbesondere dann nützlich, wenn auf beiden Kernen Threads laufen, die voneinander abhängen und auf gemeinsame Daten zugreifen. Mittels „Bandwidth Adaptation Buffer“ soll außerdem die effektive L2-Bandbreite jedes Kerns verdoppelt werden können.

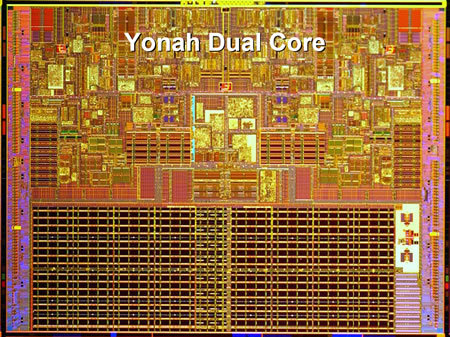

Trotz des kompliziert anmutenden Caches und dem integrierten Bus-Controller bleibt der Yonah mit insgesamt 151,6 Millionen Transistoren recht genügsam. Der Pentium D (Smithfield) bringt im Vergleich dazu 230 Mio. Transistoren auf die Waage, auch beim Athlon 64 X2 sind es 154 (2x512 kB) bzw. 233 (2x1 MB) Millionen. Da beim Yonah darüber hinaus die 65-nm-Fertigungstechnologie zum Einsatz kommt, wird auch der Die entsprechend klein ausfallen, wie bereits erste Bilder Anfang des Jahres belegten.

Im letzten Jahr hat Intel im Rahmen des Intel Developer Forums 2004 Fall (IDF 2004 Fall) verkündet, mit Hilfe des „Battery Life Optimization Programm“ bis spätestens 2010 für Notebooks eine Batterielaufzeit von 8 Stunden zu erreichen. Mehr als zwei Drittel des Stromverbrauchs entfallen dabei auf das Display (31%), den Chipsatz (21%), Prozessor (10%) und der Effizienz der Spannungswandlung (12%). Die Arbeit der 2002 ins Leben gerufenen „Mobile PC Extended Battery Life Working Group“ scheint dabei schon erste Früchte zu tragen. Aufgrund des während der Entwicklung des 65-nm-Halberleiterprozesses gewonnen Selbstvertrauens rechnet man inzwischen damit, das für 2010 gesteckte Ziel schon 2008 erreichen zu können.

Um mit Napa einen Schritt in diese Richtung gehen zu können, wird Yonah mit „Dynamic Power Coordination“ (DPC) eine Stromspartechnologie bieten, die es ermöglicht, den Prozessortakt jedes Kerns unabhängig voneinander zu steuern. Hat eine CPU weniger zu tun, so kann sie sich ohne Rücksicht auf ihren Begleiter heruntertakten.

Mit Yonah wird darüberhinaus Intels Virtualization Technology (Codename: Vanderpool, VT), Active Management Technology (iAMT) und SSE3-Support Einzug halten. Die Sicherheitstechnologie LaGrande Technology (LT) wird es entgegen der ursprünglichen Ankündigung wohl doch erst mit dem Nachfolger der Napa-Plattform geben. Diese wird neben Active Management Technology der zweiten Generation auch WiMAX unterstützen. Der Prozessor dieser Notebook-Plattform dürfte mit ziemlicher Sicherheit der Merom sein. Mit diesem wird Centrino auch endlich um 64-Bit-Support ergänzt werden – Yonah wird der Akkulaufzeit zuliebe ohne entsprechende EM64T-Erweiterung ausgeliefert werden.

Die offiziellen Details zum Yonah werden mit den Angaben zum Sockel abgeschlossen: PGA 478 oder BGA 479 (Pin Grid Array bzw. Ball Grid Array). Insbesondere die erste Variante klingt mehr als interessant: Soll der nächste Mobil-Prozessor etwa mit dem Sockel 478 des mittlerweile auf dem Abstellgleis platzierten Pentium 4 daherkommen? Intel hat sich zu diesem Sachverhalt bisher noch nicht geäußert.

Abseits der offiziellen Präsentation haben wir einige weitere Details zum Yonah und dessen Derivaten. So wird die Standard-Variante des Yonah (Dual Core) mit 2,17 GHz (x50), 2,00 GHz (x40), 1,8, GHz (x30) und 1,67 GHz (x20) angeboten werden. Die erste Zahl des Modellratings steht dabei noch nicht fest. Voraussichtlich wird man zur acht greifen, da die sieben bereits in Benutzung ist. Die Leistungsaufnahme (TDP) wird voraussichtlich bei 31 Watt liegen. Der Low Voltage Yonah (Dual Core) mit seinen 1,67 GHz (x48) oder 1,50 GHz (x38) wird sich wohl mit 15 Watt begnügen. Neben den Dual-Core-Varianten wird es den Yonah auch als Single-Core-Ausfühung mit zwei Megabyte Cache und 1,67 GHz Prozessortakt geben. Des Weiteren steht ein Ultra-Low-Voltage-Single-Core-Yonah auf dem Plan, der sich allerdings mit einem 533 MHz schnellen Frontside-Bus begnügen müssen. Details zu den Taktraten oder dem Verbrauch liegen hier noch nicht vor. Im zweiten Quartal 2006 wird auch der Celeron auf den in 65 nm gefertigten Single-Core-Yonah umschwenken. Die neue Celeron 400er-Serie wird dabei über einen 1 MB großen L2-Cache und einen 533 MHz schnellen Frontside-Bus verfügen. Ein Ultra-Low-Voltage-Celeron mit Yonah und einem Prozessorkern ist ebenfalls geplant.

Auch wenn in den Dokumenten vom Sockel 478 die Rede ist, wird der Pentium M „Yonah“ ausschließlich im Sockel 479 beheimatet sein. Eine Kompatibilität zum Sockel 478 des Pentium 4 ist definitiv nicht gegeben.