foofoobar schrieb:

TSMC nimmt einfach mehr Kohle pro Forschungseinheit ein als Intel , das ist etwas was sich schon lange abzeichnet, denn Intel verkauft keine Telefone.

Das gilt heute.

Aber es gibt eine Vorgeschichte, also lass mich Mal abschweifen.

Früher konnte Intel sehr hohe Margen bei den CPUs erzielen. Da hat es auch keine Rolle gespielt, dass die Halbleiterfertigung bei Intel teuer war. Sie war gut und hat es ermöglicht dass Intel Premium-Produkte verkaufen konnte.

Man muss sehen dass TSMC erst 1987 eingestiegen ist. Zu Beginn war TSMC 2 Jahe hinter dem Mainstream.

Aber das hat keine Rolle gespielt, weil TSMC ein neues Geschäftsmodell gegründet hat. Die Foundry. d. h. TSMC fertigt ausschließlich für seine Kunden und verkauft keine eigenen Halbleiterprodukte. Damit ist grundsätzlich ausgeschlossen dass TSMC mit seinen Kunden konkurriert.

Die Fremdfertigung war schon im Silicon Valley Standard. Jeder Halbleiterhersteller musste seine teuren Fabs auslasten. Wenn eigene Kapazität frei war, hat man für andere gefertigt, wenn die eigene Kapazität zu klein war ging man zu anderen Halbleiterherstellern. Aber es gab Interessenkonflikte (Kapazitätschwankungen, Zeitplan, ...) zwischen Fab und Kunde.

In dem 80er Jahren wurden in den USA Halbleiterunternehmen gegründet, die gar keine Fab haben wollten. Die Kapitalbindung und das Auslastungrisikos einer eigenen Fab waren für ein kleines Unternehmen viel zu hoch. Xilinx war eines der ersten dieser fabless Halbleiterhersteller und AFAIK war AMD der erste Fertigungspartner.

Die fabless Halbleiterhersteller und TSMC waren prinzipiell der perfekte Match. Witzigerweise hat Xilinx. einer der fabless Pioniere, sehr lange gebraucht. um zu TSMC zu kommen. Aber letztendlich landete Xilinx so um 2009/10 auch bei TSMC.

Einige kleinere Halbleiterhersteller in Taiwan haben erkannt, dass es als Foundry leichter wird und haben die eigenen Produkte eingestellt und wurden zur Foundry. Das Foundry-Modell wurde so erfolgreich, dass große Halbleiterhersteller ihre Fremdfertigung als Foundry tituliert haben. Aber nur weil die Fab behauptet eine Foundry zu sein, verschwinden die Interessenskonflikte zwischen 2 Halbleiterherstellern nicht.

Solange der Planartransistor verwendet wurde war es einfach von Fab zu Fab zu wechseln. Die Halbleiterhersteller konnten mit ihren Masken zu einer Fab gehen und diese mit der Fertigung beauftragen. Und später ihre Masken wieder mitnehmen und zu einer anderen Fab gehen.

Mit dem Wechsel vom Planartransistor auf FinFET hat sich dies drastisch geändert. Die Halbleiterunternehmen müssen ihr Design mit dem PDK (Prozess Design Kit) der Fab erstellen. Nach dem Tapeout erstellt die Fab aus den Designunterlagen des Kunden die Masken. Das Chipdesign des Kunden ist damit an die Fab gebunden. Wenn der Kunde mit diesem Chip zu einer anderen Fab gehen will muss das gesamte Chipdesign mit dem PDK der anderen Fab neu gemacht werden.

Und dann haben sich in den 90ern und 2000ern Unternehmen etabliert, die gar keine Chips herstellen wollten, sondern nur IP (Funktionsblöcke) verkaufen haben. Das bekannteste Unternehmen dieser Art ist Arm. Andere bieten PCIe- Speicher, USB-Kontroller, SRAM-Makro, ... an. Wobei der Übergang zwischen Herstellern von EDA-Tools und Anbietern von IP fließend ist.

TSMC hat dies erkannt und schließlich in der Open Innovation Plattform OIP die Zusammenarbeit mit Herstellern von EDA-Tools und IP-Anbietern gebündelt. AFAIK hat TSMC das größte Angebot an IP aller Fabs. D. h. wenn ein Kunde wechseln will, muss alle zugekaufte IP, die sein Chip verwendet, für die PDKs der anderen Fab verfügbar sein. Ist sie nicht verfügbar muss nicht nur das Chipdesign neu gemacht werden, sondern auch der RTL-Code angepasst werden, um die Ersatz-IP einzubinden.

So und jetzt kommen wir zum eigentlichen Punkt, die Fab hat vollen Zugriff auf das Chipdesign des Kunden. Auf die IP die der Kunde gekauft hat und auf die IP die der Kunde selbst entwickelt hat. Also muss der Kunde darauf vertrauen, dass die Fab dies nicht missbraucht in dem sie seine IP aus dem Chipdesign selbst verwendet oder anderen Kunden Zugriff darauf gibt. Oder den eigenen Entwicklern Zugriff auf das Kundendesign gibt.

Die Fab eines Halbleiterherstellers wird nicht dadurch zur Foundry, weil sie auf der Website so bezeichnet sind. Einiges kann man machen in dem man glaubwürdige Trennmauern zwischen der Fab und den eigenen Designabteilungen hochzieht. Die Interessenkonflikte, die entstehen weil Halbleiterhersteller und Kunde gegeneinander konkurrieren verschwinden nicht.

So war es unausweichlich, dass Apple von Samsung zu TSMC wechselt. Die Konzernschwester hat im Mobilphonemarkt gegen Apple konkurriert, Samsung LSI entwickelte wie Apple CPU-Kerne.

Mit Apple kam nicht nur neues Volumen zu TSMC. TSMC und Apple sind eine tiefgreifende Kooperation eingegangen. Diese Kooperation hat TSMC gezwungen Apple im Jahresrythmus verbesserte Prozesse zur Verfügung zu stellen. Das hat dazu geführt dass TSMC 10 nm, 7 nm und 5 nm in schneller Folge eingeführt hat. Bei 3 nm hatte TSMC Probleme. Nach den letzten Verlautbarungen wird 2 nm 2025 für Apple bereitstehen.

Intel hat sich traditionell auf Performance konzentriert. Da Intel oft einen Vorsprung von einer Generation und mehr hatte, waren die Prozesse trotzdem auch bei Power und Area besser als die Konkurrenz. Kann Intel den Fokus auf Performance beibehalten?

foofoobar schrieb:

Zusätzlich sind die Prozesse für Telefone keine HPC-Prozesse -> schnellerer ROI/Forschungseinheit.

Ich sehe es als viel Entscheidenter an dass TSMC ein viel größeres Volumen als Intel hat. Und außerdem kann TSMC die Investitionen in die Fabs viel länger nutzen als Intel. Es gibt genügend Kunden für die alten Prozesse. Intel hat bisher die bestehenden Fabs umgerüstet. Eine Fab für einen neuen Prozess umzurüsten bedeutet im Klartext Maschinen auszubauen und durch neue zu ersetzen. AFAIK werden die bisher eingelagert bzw. verschrottet.

Intel kann die eigene Halbleiterfertigung nur dann retten, wenn Intel genügend Volumen als Auftragsfertiger generiert und von der Anzahl der Waferstarts nicht noch weiter hinter TSMC zurückfällt. Aber um glaubhaft als Auftragsfertiger auftreten zu können, muss Intel zuerst einmal neue Fabs hochziehen.

Neben der Prozessentwicklung ist die zweite Herausforderung, die Kapazität dieser neuen Fabs in Volumen umzuwandeln.

foofoobar schrieb:

Solange sich daran nichts ändert wird Intel weiter zurückfallen.

Vor allem wenn Intel als Großkunde von TSMC sowohl die eigene Forschung als auch die von TSMC finanziert.

Wir müssen ganz einfach sehen wie Intel bei den Prozessen liefert. Und damit meine ich nicht Anzukündigen man hat den Prozess fertig, sondern Produkte ausliefern.

Wenn die Roadmap eingehalten wird, dann sieht es ganz passabel aus. Wenn es so läuft wie bei intel 4 schreien der Prozess ist fertig und ein Jahr später das erste Produkt zu launchen.

Intel wird sehr kreativ mit den Namen der Prozesse.

Aber es genügt eben nicht nur Fabs hinzustellen und die Prozesse zu entwickln. Für die Prozesse müssen PDKs bereistehen. Und es muss genügend IP für die Kunden verfügbar sein. Die meisten Journalisten die über die Vereinbarung von Arm und Intel geschrieben haben, haben gar nicht verstanden welch ein Meilenstein diese Vereinbarung für Intel war. Intel hat traditionell für CPU und Chipssätze sehr gute eigene IP, aber das alleine wäre zu wenig. Auch IP anderer Anbieter muss für Chips verfügbar sein, die bei Intel gefertigt werden.

foofoobar schrieb:

Sowas wie das Carry-Bit von einem Adder auf einen Adder auf einem anderen Die zu schieben halte ich in nächster Zeit für ziemlich unwahrscheinlich.

Du musst die Folie im Kontext sehen.

Das hat Sam Naffziger im Dezember 2021 präsentiert und sollte auch ein Ausblick sein.

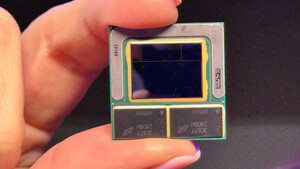

Wir haben gesehen, dass mit X3D der L3 Cache ergänzt wurde. Da SRAM in absehbarer Zukunft nur schlecht falls überhaupt skaliert ist es unvermeidbar Logik und SRAM zu trennen. Dabei muss es nicht bei einer Ebene fürs SRAM bleiben.

Vor allem sobald der Hauptspeicher auf den Prozessor kommt.

Die Herausforderung ist die gestapelten Chips im optimalen Temperaturbereich zu halten. Aber es geht beim Stapeln nicht nur um den Flächenzuwachs. Im selben Vortrag hat Sam Naffziger gesagt, dass der 96 MByte L3-Cache in einer Ebene nicht realisierbar gewesen wäre. Die Latenz wäre zu schlecht geworden.

Es wird unweigerlich 3-dimensional, CFET, BSPDN, 3D-Stacking mit Hybrid Bonding.

Wie die Techniken kombiniert werden wird sehr spannend werden. Insbesondere BSPDN und 3D-Stacking dürfen sich nicht in die Quere kommen.