N7+: TSMC liefert 7-nm-EUV-Chips in hoher Stückzahl

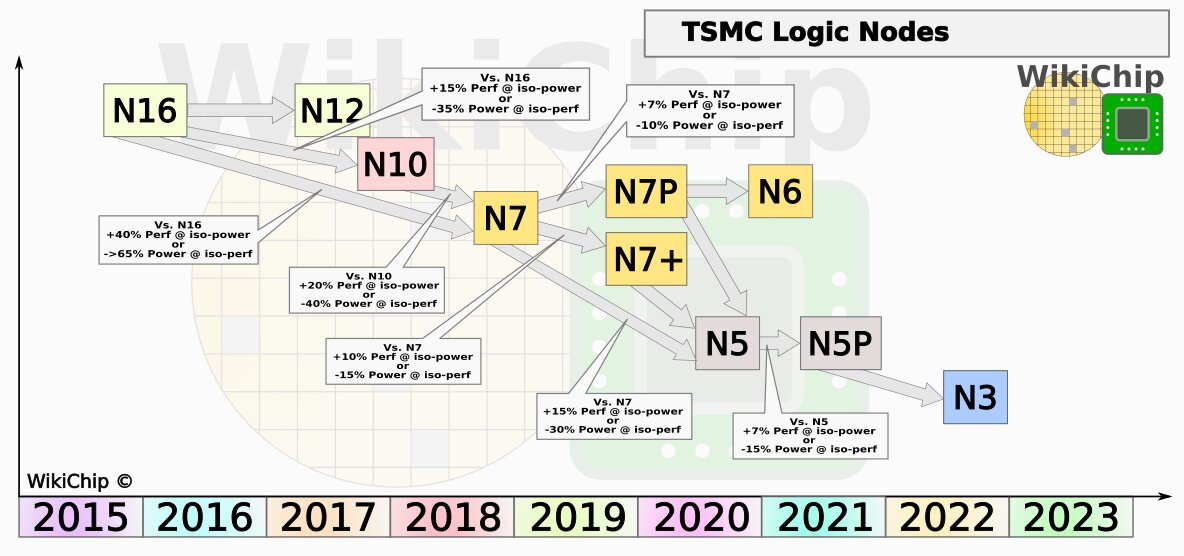

Nach dem Start der Massenfertigung im zweiten Quartal hat TSMC jetzt verkündet, dass finale Chips im neuen 7-nm-Verfahren mit EUV-Technik alias „N7+“ inzwischen in hohen Stückzahlen ausgeliefert werden. Für Ende 2020 plant TSMC den Beginn der Massenfertigung im N6-Verfahren mit EUV.

Um welche Produkte es sich bei den Chips handelt, verrät die Ankündigung von TSMC zwar nicht, doch ist bekannt, dass Huawei als Kunde das SoC Kirin 990 in der 5G-Variante im N7+-Verfahren bei TSMC herstellen lässt, das im Smartphone-Flaggschiff Huawei Mate 30 Pro eingesetzt wird.

Nach Angaben von TSMC läuft die EUV-Premiere sehr gut an, denn schon jetzt soll die Chipausbeute (Yields) auf ähnlichem Niveau wie beim ersten 7-nm-Verfahren liegen, das sich bereits seit einem Jahr in der Massenfertigung befindet.

Gegenüber dem herkömmlichen 7-nm-Prozess (N7) von TSMC wird bei N7+ erstmals die EUV-Lithografie verwendet. Vorerst werden aber nur einige Schichten (Layer) mit EUV belichtet, der Umstieg auf die neue Technik erfolgt schrittweise.

TSMC bewirbt N7+ mit einer Verbesserung der Transistordichte um 15 bis 20 Prozent gegenüber N7. Parallel soll die Leistung bei gleicher Leistungsaufnahme um bis zu 10 Prozent steigen; alternativ nehme die Leistungsaufnahme bei gleicher Leistung um etwa 15 Prozent ab.

Damit ist N7+ zumindest auf dem Papier besser aufgestellt als N7P als zweite Weiterentwicklung des 7-nm-Verfahrens, die aber noch kein EUV nutzt. Bei N7P (P für Performance) verspricht TSMC 7 Prozent mehr Leistung respektive 10 Prozent weniger Leistungsaufnahme.

Für das erste Quartal 2020 plant TSMC größere Gehversuche (Risc Production) mit dem N7-Nachfolger N6 (6 nm + EUV), der aber erst Ende 2020 den Status der Massenfertigung erreichen soll, womit die breite Verfügbarkeit darauf basierender Produkte ab 2021 zu erwarten ist.

Das parallel entwickelte 5-nm-Verfahren (N5) mit größerem Einsatz von EUV steht zeitlich sogar noch vor N6 auf der Roadmap und soll laut einer Ankündigung aus diesem April Anfang 2020 in die Serienfertigung starten. In der jüngsten Ankündigung von TSMC findet es aber keine Erwähnung.