V-NAND V7: Samsung setzt für 160 Layer oder mehr auf Double-Stack

Laut einem Bericht aus Südkorea wird Samsung bei der siebten Generation seines „V-NAND“ genannten 3D-NAND auf mindestens 160 Layer setzen. Die Rede ist von einer „super-gap strategy“. Etwas konkreter ist der Einsatz eines Double-Stack-Designs.

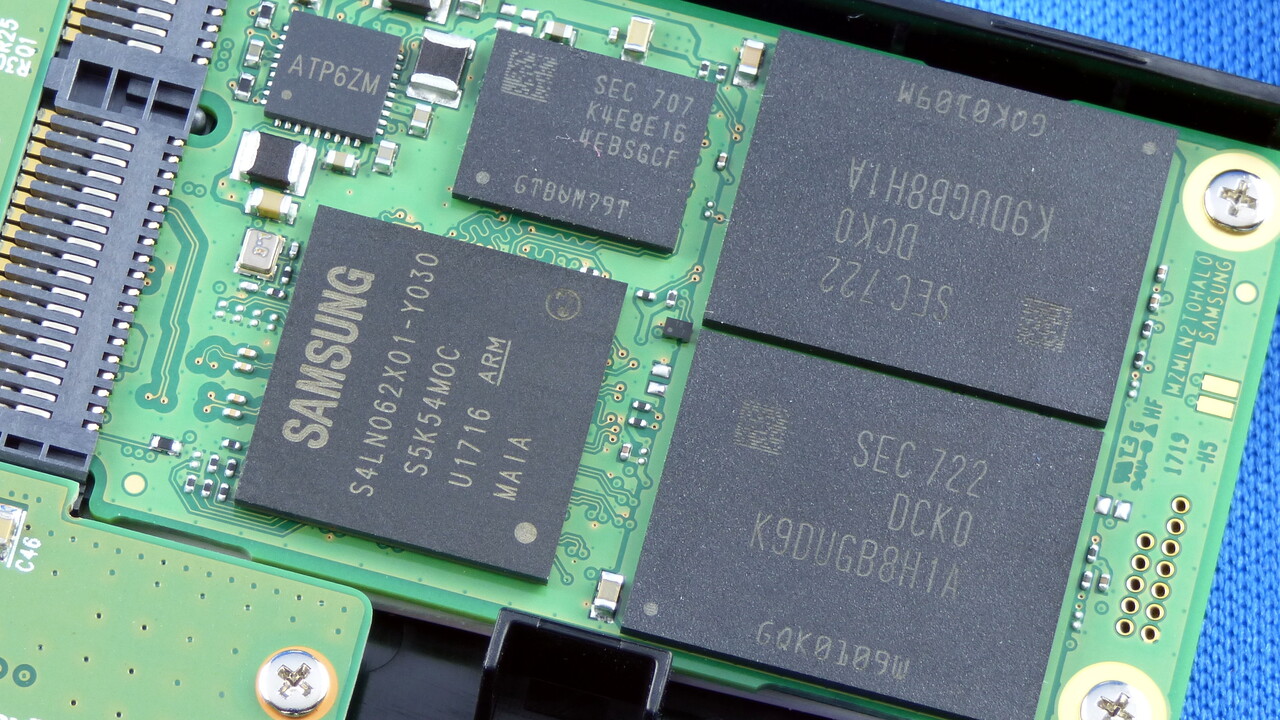

Die Informationen zur 7. Generation V-NAND (V-NAND V7) stammen von einer Aktionärsversammlung von Samsung berichtet The Electronic Times in ihrer englischsprachigen Ausgabe der etnews. Die technische Beschreibung im Artikel lässt noch viel Interpretationsspielraum, doch deutet sich an, dass Samsung auf ein Design mit zwei Layer-Türmen (Double-Stack) umschwenkt. Bei anderen NAND-Herstellern werden schon lange mehrere Stacks eingesetzt, um die Zahl der Zellschichten pro Chip auf derzeit bis zu 128 Layer zu erhöhen.

Nicht nur auf die Layer-Zahl kommt es an

Ähnlich wie die Nanometer-Angaben bei Prozessoren ist die Anzahl der Layer bei 3D-NAND kein vergleichbarer Maßstab und sagt allein nicht viel über den technischen Fortschritt aus. Viele weitere Faktoren bestimmen Kosten, Leistung, Effizienz und Haltbarkeit und damit die Konkurrenzfähigkeit von 3D-NAND. Die Steigerung der Zellschichten ist ein Mittel, um die Speicherdichte weiter zu erhöhen, die allerdings auch von der Chipfläche abhängt.

Bei der Speicherdichte hinkt Samsung hinterher

Diesbezüglich hat Samsung augenscheinlich Nachholbedarf, denn laut den auf der ISSCC 2019 publizierten Eckdaten zum V-NAND V6 liegt dieser bei der Speicherdichte weit hinter dem BiCS5 von Kioxia (früher Toshiba) und Western Digital zurück. Bei QLC-NAND will Newcomer YMTC aus China mit seinem neuen 128-Layer-NAND bei der Speicherdichte aktuell führen, doch fehlt dafür noch ein Beleg.

Beim BiCS5 werden zwei Stacks à 56 Layer zu einem 112-Layer-Chip vereint, obgleich früher von 128 Layern die Rede war, wie es auch SK Hynix bei seinem „4D-NAND“ angibt. Samsung hatte einst beim V-NAND V6 von „100+ Layer“ gesprochen, doch kursieren auch Angaben wie 110-120 Layer oder 136 Layer. Eine Erklärung für die unterschiedlichen Angaben ist, dass es neben den Schichten mit Speicherzellen noch Ebenen für die Chip-Logik gibt.

Intel hat seinerseits 144-Layer-NAND in Aussicht gestellt, während Ex-Partner Micron einen radikalen Design-Wechsel auf die Replacement-Gate-Technik zunächst mit 128 Layern vollziehen will.

Hersteller planen mit Hunderten Layern

Für die ferne Zukunft planen Hersteller wie Samsung schon mit mehr als 300 Layern, SK Hynix hatte sogar schon von 800 Layern geträumt. Die kommenden Jahre werden zeigen, wie hoch die Hersteller noch stapeln können. Parallel werden Möglichkeiten gesucht, um etwa die Zellen an sich zu verkleinern oder aber noch mehr Bit pro Zelle zu speichern. Aktuell werden bis zu vier Bit pro Speicherzelle beim sogenannten QLC-NAND gesichert, was aber in puncto Leistung und Haltbarkeit einen weiteren Rückschritt von SLC (1 Bit) auf MLC (2 Bit) und TLC (3 Bit) bedeutet. Dennoch erwägt die Branche mit PLC-NAND bereits Lösungen mit 5 Bit pro Zelle.