DDR5: JEDEC verabschiedet finale Spezifikationen

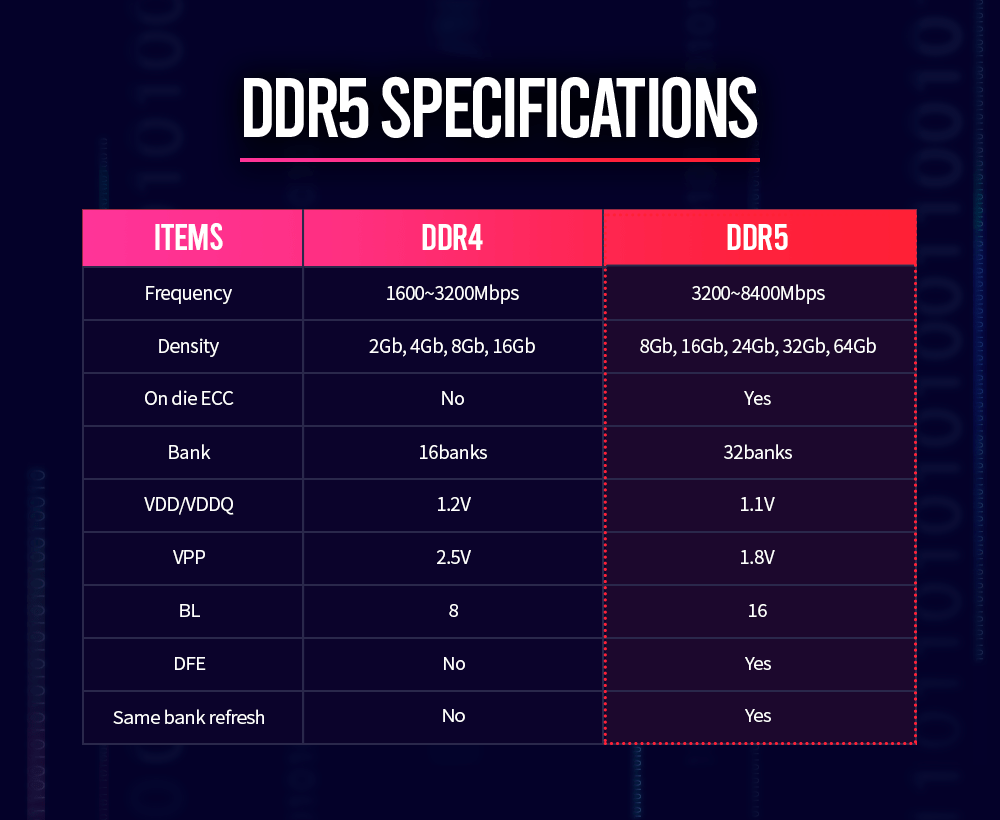

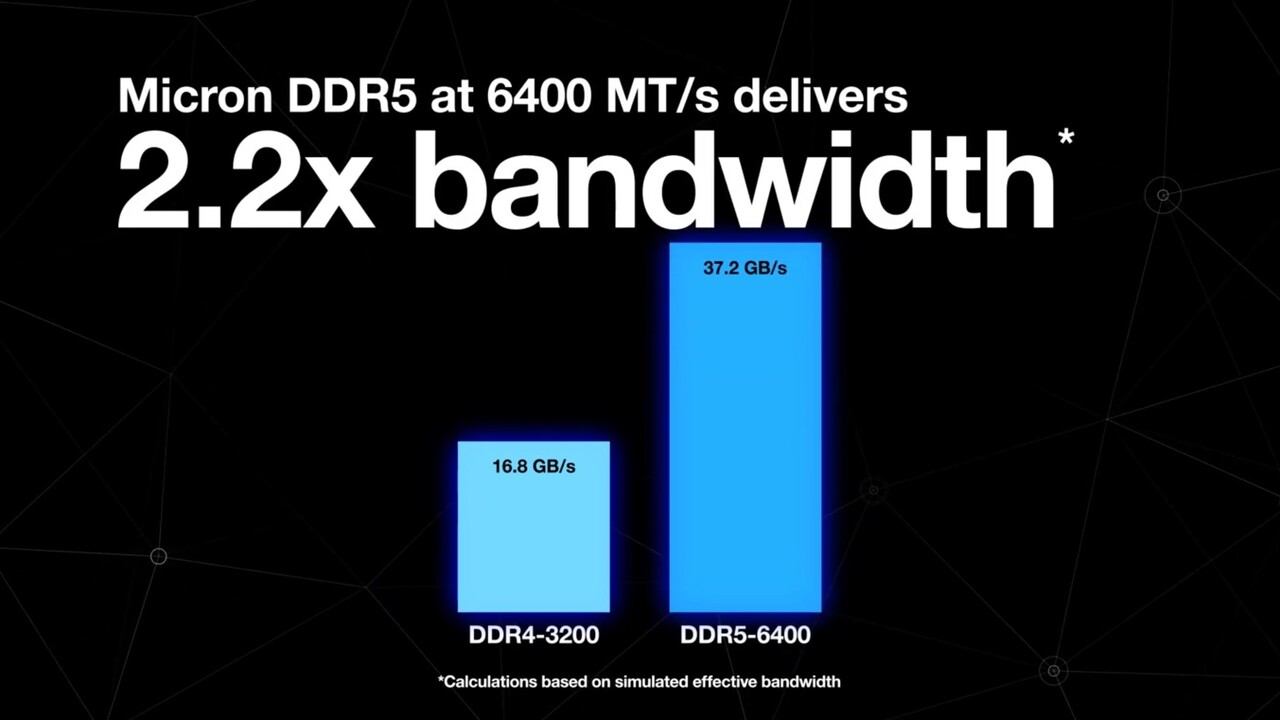

Mit dem neuen JESD79-5-Standard hat die JEDEC die offiziellen Spezifikationen für Arbeitsspeicher vom Typ DDR5 final verabschiedet. Während mit dem Vorgänger DDR4 offiziell bei 3.200 MT/s Schluss war, startet der neue Speicherstandard bei effektiven 4.800 MHz und erreicht mit DDR5-6400 mehr als die doppelte Bandbreite.

DDR5 startet 2021 im Server und Desktop

Zudem wurde die Versorgungsspannung der Speichermodule, die sogenannte VDIMM, von 1,2 Volt auf 1,1 Volt gesenkt, was sich in einer gesteigerten Effizienz der DRAM-Kits bemerkbar machen soll. Die JEDEC Solid State Technology Association (JEDEC) und deren mehr als 150 Partnerunternehmen machen mit der Verabschiedung der finalen Spezifikationen den Weg frei für eine Markteinführung von DDR5 im Jahr 2021.

DDR5 offiziell mit bis zu 6.400 MT/s spezifiziert

Während SK Hynix bereits DDR5 mit effektiven 8.400 MHz in Aussicht stellt, bestätige Micron die offiziellen Spezifikationen der JEDEC und kündigte Anfang des Jahres an, dass sich DRAM-Module mit DDR5-6400 bereits im Sampling befinden.

64 Gbit pro Chip und bis zu 2 TB pro Modul

Neben einem effektiv höheren Speichertakt und einer daraus resultierenden höheren Speicherbandbreite wurde die Kapazität pro DRAM-Chip und Speichermodul angehoben. DDR5 SDRAM bietet die vierfache Kapazität von DDR4 SDRAM.

Auch wenn die maximalen Kapazitäten analog zum maximalen Speichertakt erst in den kommenden Jahren erreicht werden, nennen die offiziellen Spezifikationen 64 Gbit pro DRAM-Chip (IC) sowie bis zu 2 TB pro Speichermodul. Zukünftig werden die DIMMs flexibler als bisher über zwei Speicherkanäle mit jeweils 32 Bit angesprochen, weshalb bei DDR5 von einem 64 Bit breiten Speicherbus die Rede ist.

Mit der Spezifikation JESD79-5 bestätigt die JEDEC im Grunde weitestgehend die bereits von SK Hynix und Micron genannten Eckdaten der neuen Speichertechnologie, auch wenn es sich bei DDR5-8400 zum einen um Zukunftsmusik und zum anderen um OC-Module handeln wird.

Zur Verbesserung der Signalintegrität bei hohen Taktfrequenzen kommt eine sogenannte Decision Feedback Equalization (DFE) zum Einsatz. Der dedizierte integrierte Schaltkreis, ein Integrated Circuit (IC), sorgt dafür, dass die engmaschigen Toleranzen vom DDR5-Speicherbus eingehalten werden.

288 Pins und eine eigene Spannungsversorgung

Speichermodule auf Basis von DDR5 sollen durch die Anpassungen am Design eine um bis zu 20 Prozent geringere Leistungsaufnahme pro Speicherchip aufweisen als die aktuelle Generation.

Die Spannungsmodulation erfolgt zukünftig nicht mehr über das Mainboard, sondern über eine eigene integrierte Spannungsregulierung auf den DDR5-DIMMs, UDIMMs und LRDIMMs. Die Module besitzen wie ihre Vorgänger erneut 288 Pins, die offiziellen Spezifikationen sehen aber neuerdings mindestens zwei Temperatursensoren pro Speichermodul vor.

Die JEDEC sieht folgende Spezifikationen als Highlights von DDR5:

- Fine grain refresh feature: as compared to DDR4 all bank refresh improves 16 Gbps device latency. Same bank selfrefresh offers better performance by enabling some banks to refresh while others are in use.

- On-die ECC and other scaling features enable manufacturing on advanced process nodes.

- Improved power efficiency enabled by Vdd going from 1.2V to 1.1V as compared to DDR4.

- Use of the MIPIÒ Alliance I3C Basic specification for system management bus.

- At the module level, voltage regulator on DIMM design enables pay as you go scalability, better voltage tolerance for improved DRAM yields and the potential to further reduce power consumption.

JEDEC – Additional features include

Als erste potenzielle Kandidaten für den Einsatz von DDR5 schicken AMD und Intel wahrscheinlich ihre Enterprise-Prozessoren EPYC („Genoa“) auf Basis von Zen 4 sowie Xeon („Sapphire Rapids“) auf der Plattform „Eagle Stream“ ins Rennen. Auch auf den Mainstream- und HEDT-Plattformen beider Hersteller ist ab Ende 2021 mit DDR5 zu rechnen.