Ponte-Vecchio-Nachfolger: Intel Rialto Bridge fasst 160 Xe-Cores in neuen Nodes

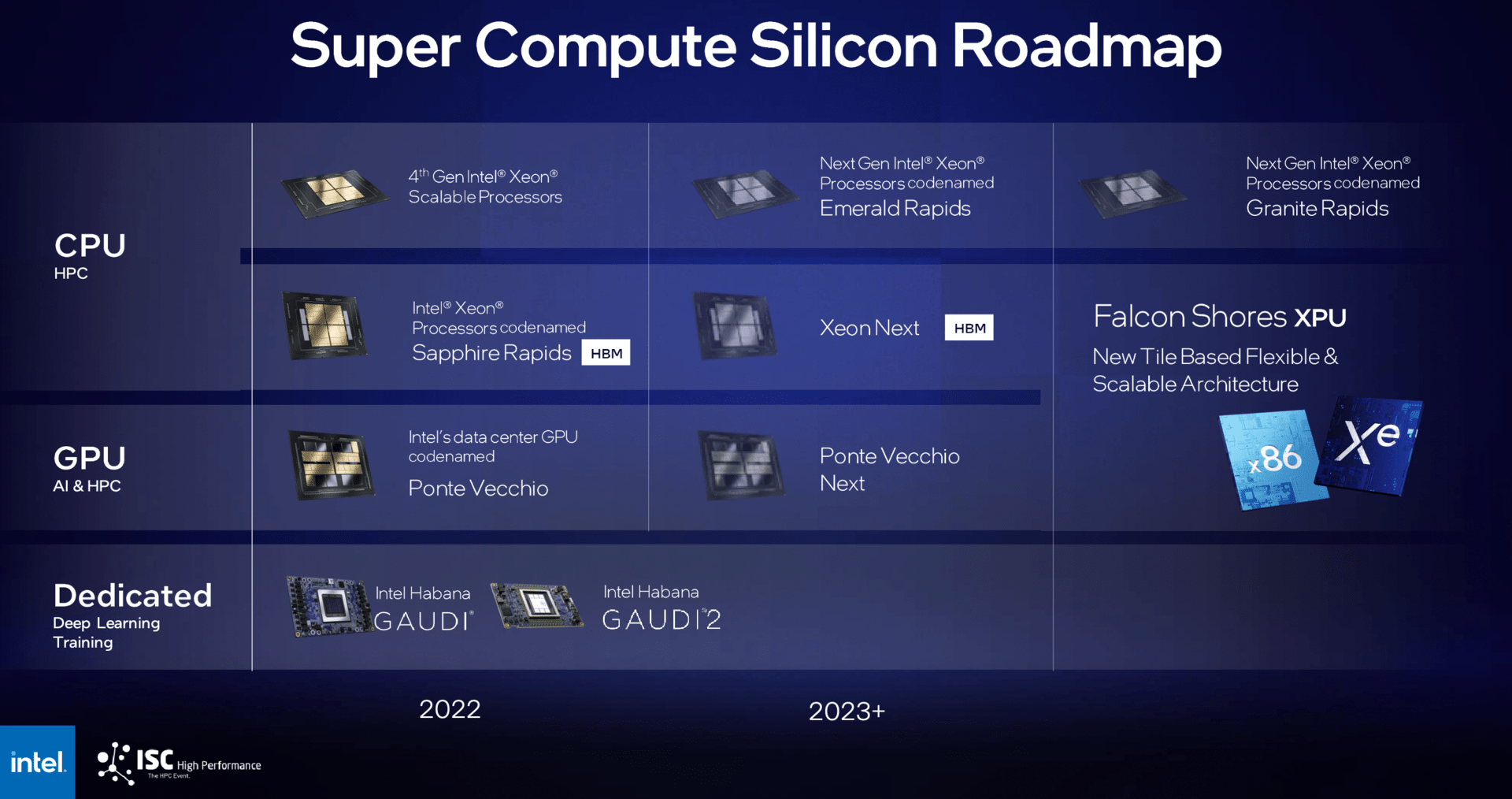

Zur ISC 2022 in Hamburg hat Intel erste Details zu den Next-Gen-HPC-GPUs Rialto Bridge als direkten Ponte-Vecchio-Nachfolger und Falcon Shores preisgegeben. Rialto Bridge erhöht als „Tick“ mit neuen Prozess-Technologien die Anzahl der Xe-Cores um 25 Prozent, Falcon Shores soll ab 2024 dann alles anders machen.

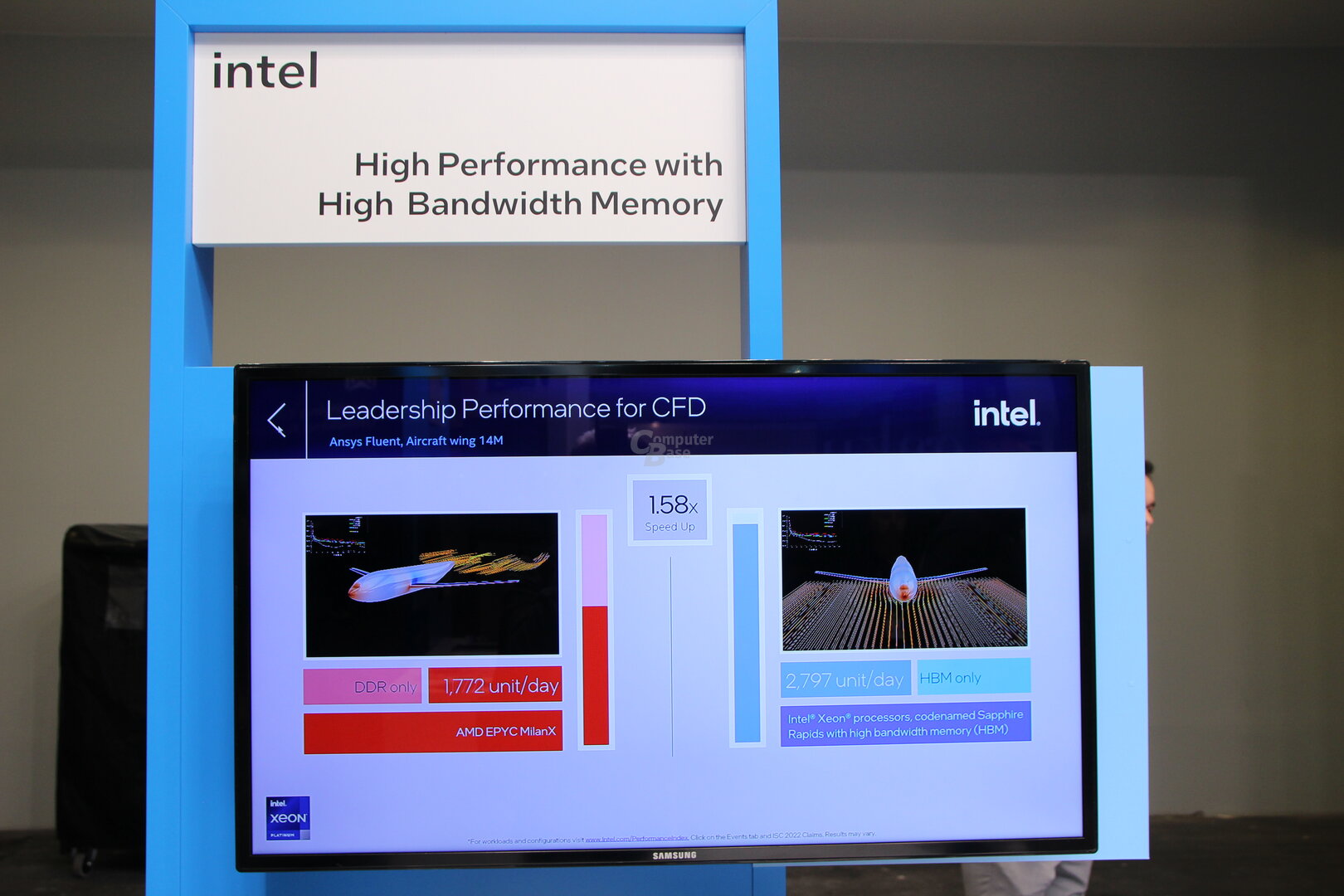

Benchmarks zu Sapphire Rapids mit HBM

Doch erst einmal war das Thema Sapphire Rapids, die Server-Variante der Alder-Lake-Architektur. Zur Messe zeigte Intel diese Chips in ausgewählten Benchmarks ohne, aber vor allem mit HBM. Dieses Alleinstellungsmerkmal sei ebenfalls bereits seit 2018 in der Mache, erklärte der Hersteller im Gespräch mit ComputerBase. Stolz zeigte Intel am eigenen Stand Anwendungen, in denen die Konkurrenz natürlich nicht gut wegkommt. Dabei wurde der neue Prozessor nur mit HBM betrieben, auf DDR5 als Ergänzung im System komplett verzichtet.

Das ist natürlich ein Spezialfall, denn hier limitiert unter anderem die Größe: Mehr als 64 GByte HBM pro CPU gibt es nicht. Zwei CPUs können sich die dann 128 GByte zwar teilen, allerdings mit entsprechender Latenzstrafe für die Kommunikation untereinander.

Sapphire Rapids mit HBM ist ein Aushängeschild für den Supercomputer Aurora. Der 2-ExaFLOPS-Supercomputer soll später im Jahr mit genau diesen Lösungen und der dreifachen Menge an Ponte-Vecchio-GPUs bestückt sein. Ein passendes Blade zeigt Intel zusammen mit HPE auf der Messe. HPE stellt dort auch ein Blade des ersten ExaFLOPS-Supercomputers Frontier mit CPUs und GPUs von AMD zur Messe aus.

Als Erscheinungstermin steht weiterhin das zweite Halbjahr 2022 in den Büchern. Die HBM-Variante sollte eigentlich später erscheinen, in Folge der Verzögerungen sind der normale Xeon und die HBM-Variante jedoch wieder etwas näher zusammen gerückt.

Eine lange Lebenszeit wird Sapphire Rapids letztlich ohnehin nicht eingeräumt, denn binnen eines Jahres soll bereits Emerald Rapids und dann Granite Rapids erscheinen. Die Kadenz von vier bis fünf Quartalen für neue Produkte soll in jedem Bereich gelten, erklärte Jeff McVeigh als Chef der Supercomputer-Sparte bei Intel.

Rialto Bridge wird Nachfolger von Ponte Vecchio

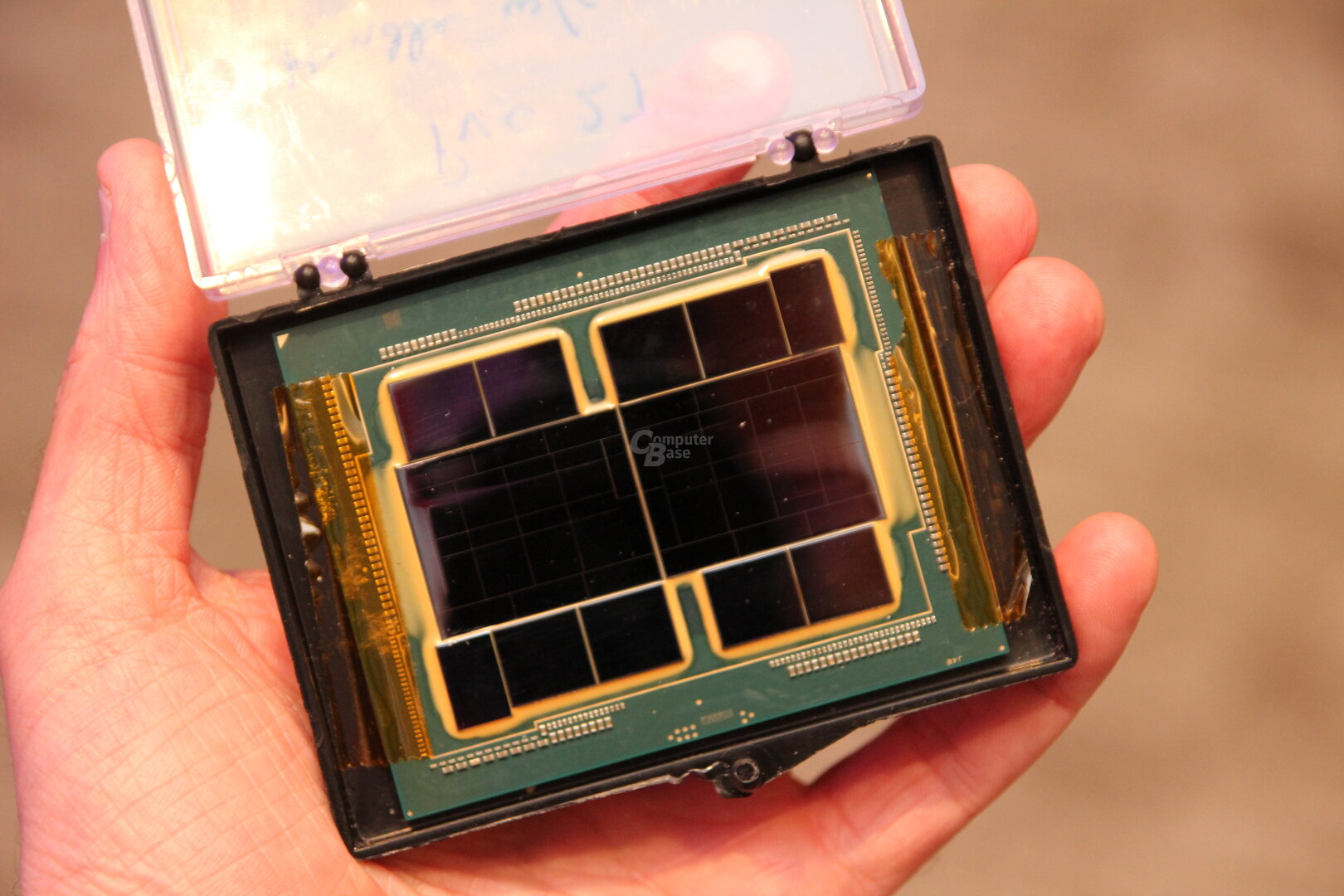

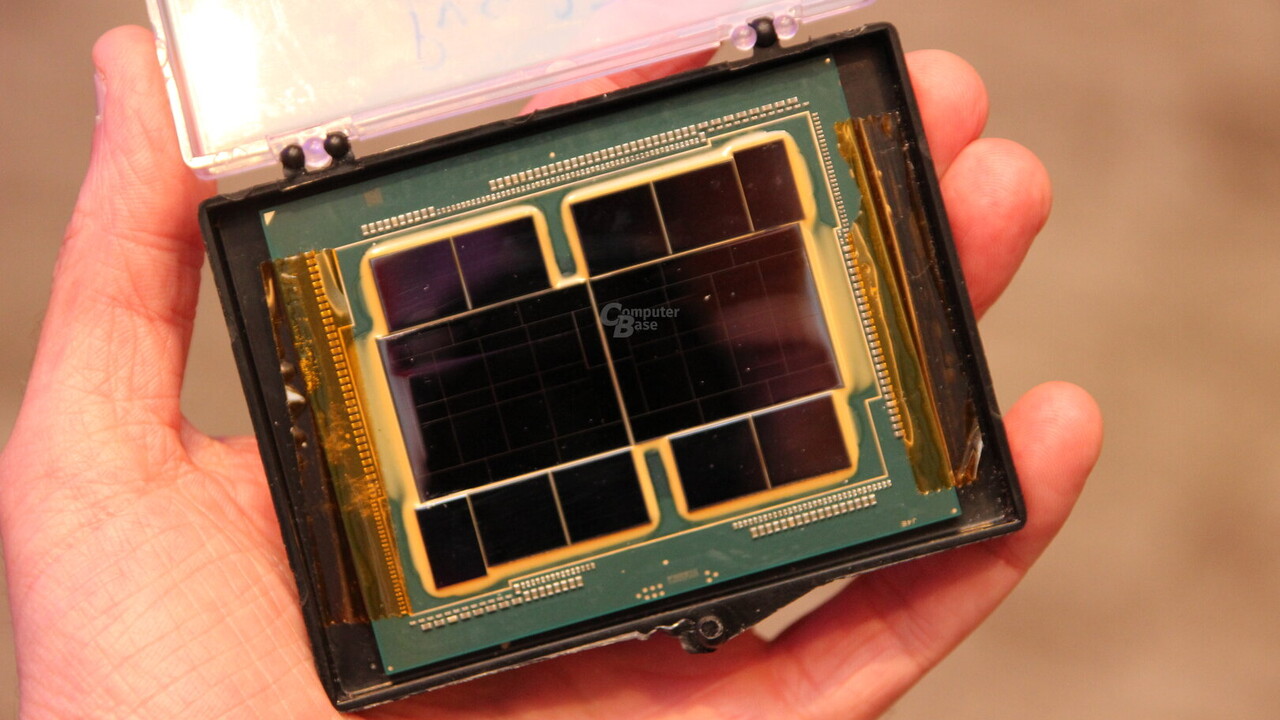

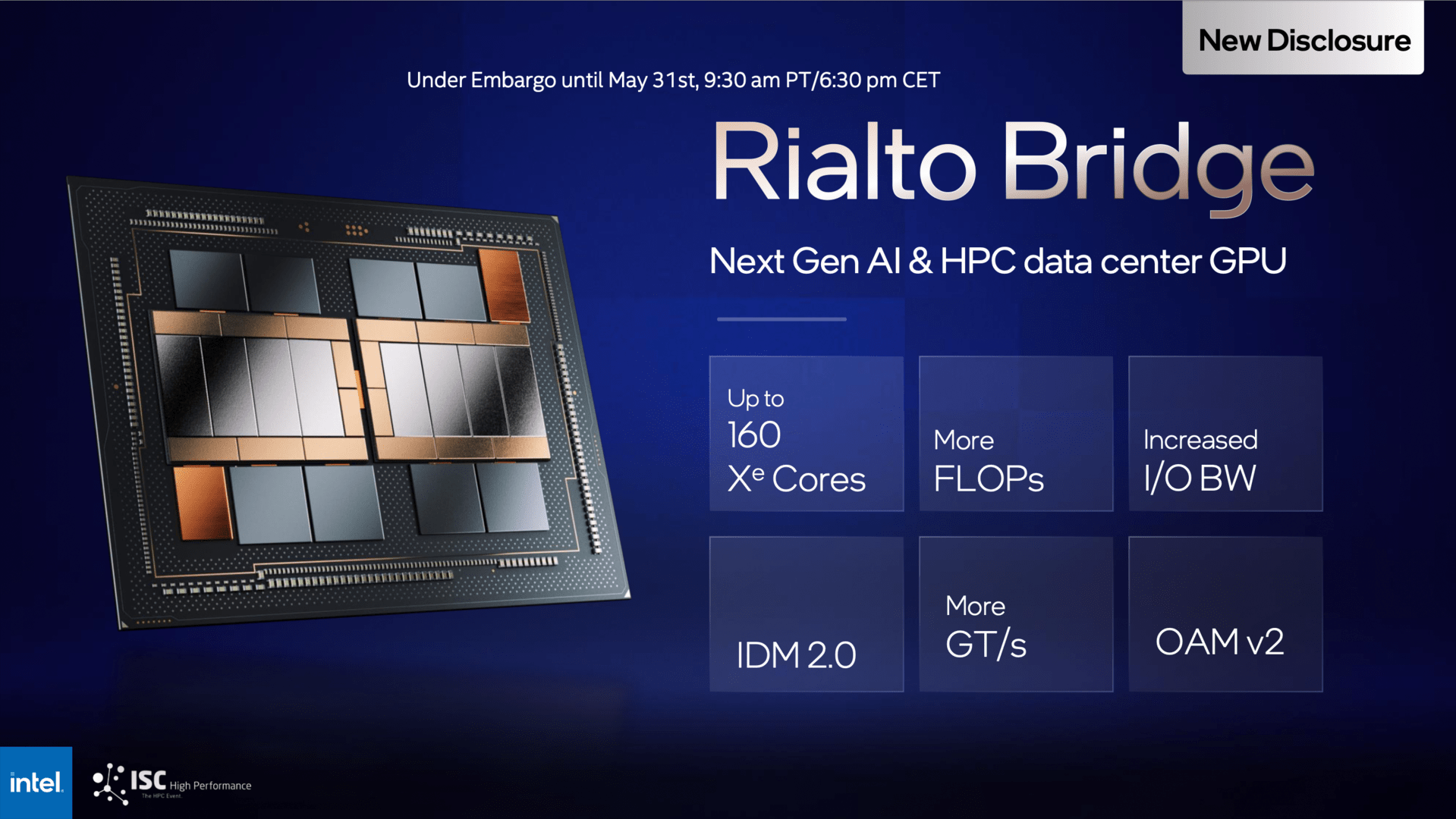

Bereits ab Mitte 2023 will Intel den Nachfolger von Ponte Vecchio ausliefern: Rialto Bridge. Ponte Vecchio ist die auf einem Multi-Chip-Ansatz basierende HPC-GPU auf Basis der Xe-Architektur.

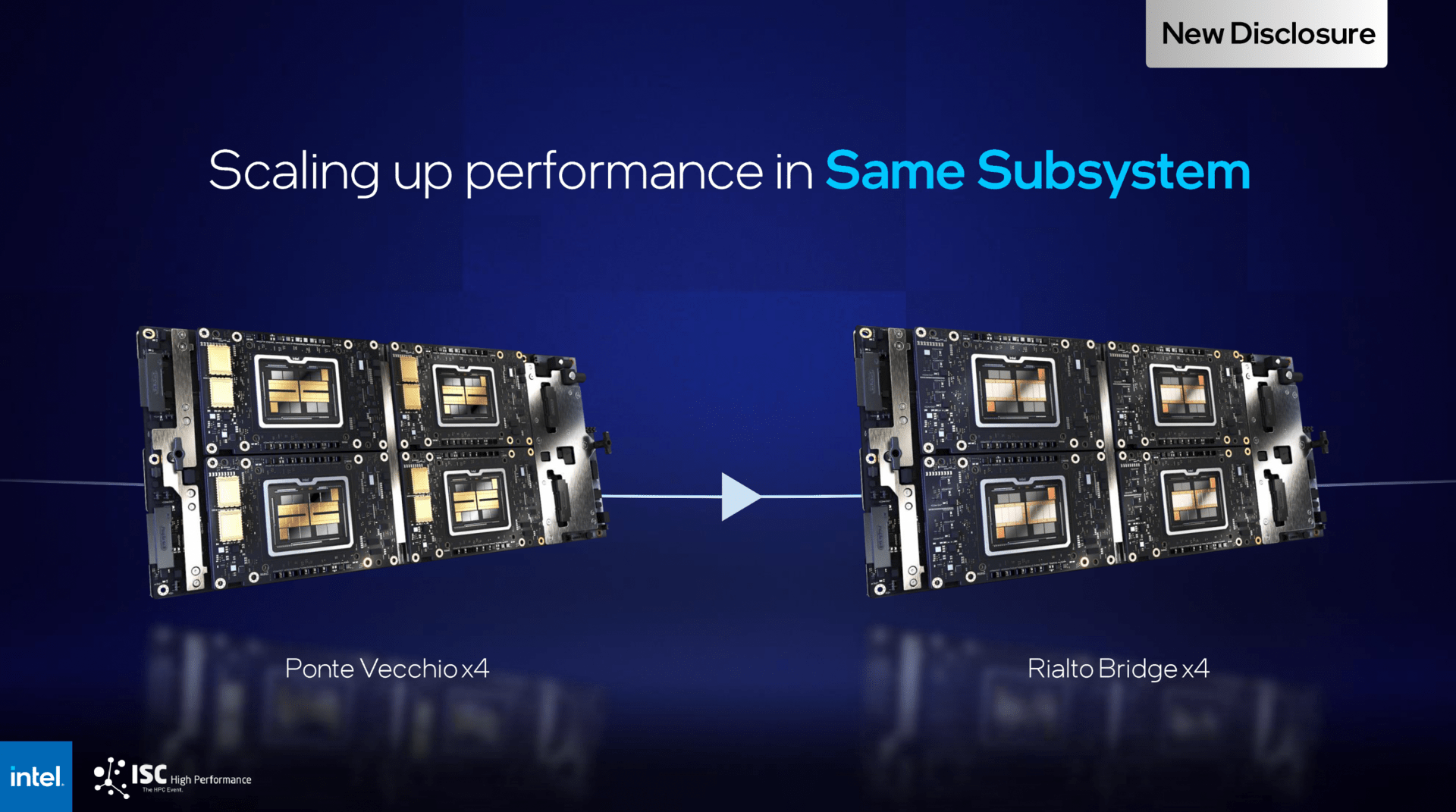

Dank neuer Technologien in der Fertigung soll mit Rialto Bridge auf ähnlicher Fläche mit Sockelkompatibilität und dank OAM-2.0-Support für höhere Verbräuche mehr Leistung bereitgestellt werden.

Dafür wird die Anzahl der Xe-Grafikkerne von 120 auf 160 angehoben. Zu welcher Generation diese gehören, sagte Intel nicht, vermutlich bleibt es aber beim Ursprung. Intel betonte in einem Pressegespräch vorab, dass Ponte Vecchio so etwas wie die ultimative Lösung sei: Eine maximale Anzahl an kleinen Chips (Tiles) kombiniert in einem Package.

Rialto Bridge soll dort einen etwas wirtschaftlicheren Weg finden, denn was zum Teil vielleicht beim einzelnen Chip bei Ponte Vecchio gespart wird, geht beim überaus komplizierten Package wieder verloren. Auf Nachfrage von ComputerBase, ob dies heißt, dass Rialto Bridge weniger Tiles bieten wird, gab Intel aber keine klare Antwort. Auf die nicht ganz ernst gemeinte Nachfrage, ob man denn nicht einfach die Chips auf dem präsentierten Bild zählen könnte, gab sich Intel zurückhaltend: Es sei nur ein Rendering.

Am Ende wird Rialto Bridge die berühmte Optimierung des ersten Produkts sein. Doch das allein soll mit dem Ausbau der Kerne, erhöhter Bandbreite und mehr FLOPs zu einem deutlich runderen Produkt reichen, erklärte Intel vorab. Im Rahmen einer Keynote könnten kurzfristig zusätzliche Details genannt werden, ComputerBase wird diese Meldung bei Bedarf aktualisieren.

ComputerBase hat Informationen zu diesem Artikel von Intel unter NDA erhalten. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.