Intel Pentium 4 „Prescott“ im Test: Rückschritt dank Fortschritt?

3/2990nm Fertigungsprozess

Die wichtigste und interessanteste Neuerung beim Prescott ist leider auch die komplizierteste. Hier sind wir eigentlich an einem Punkt angelangt, an dem wir den Sachverhalt kaum besser darstellen können als Intel selbst. Wir möchten es dennoch versuchen, im Zweifelsfalle haben jedoch Intels fachliche Abhandlungen recht.

Es war im März 2002, als Intel voller Stolz die Produktion eines funktionsfähigen 52 Megabit SRAM im 90 nm Fertigungsprozess verkündete. Das gute Stück brachte 330 Millionen Transistoren bei einer Fläche von lediglich 109 mm² auf die Waage. Der Prescott, der Mithilfe der gleichen Fertigungstechnologie zum Leben erweckt wird, möchte mit 125 Millionen Transistoren auf einer Fläche von 112 mm² überzeugen. Zum Vergleich: Der Athlon 64 bringt im 130nm Fertigungsprozessr "nur" 106 Mio. Transistoren auf einer Fläche von 193 mm² mit. Die Transistorendichte beim Prescott ist also weitaus höher.

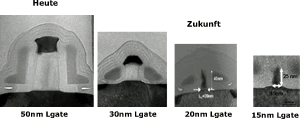

Dieser Vorteil des Prescotts ist eine Errungenschaft des 90nm Prozesses: Die Strukturen werden feiner. Doch bevor es darum geht, was mit den "90nm" überhaupt gemeint ist, soll der aktuelle Stand der Entwicklung eingeordnet werden:

| Prozessname | P856 | P858 | Px60 | P1262 | P1264 | P1266 |

|---|---|---|---|---|---|---|

| Produktion | 1997 | 1999 | 2001 | 2003 | 2005 | 2007 |

| Strukturgröße | 0.25µm | 0.18µm | 0.13µm | 90nm | 65nm | 45nm |

| Gate-Länge | 0.20µm | 0.13µm | unter 70nm | unter 50nm | unter 35nm | unter 25nm |

| Wafer (mm) | 200 | 200 | 200/300 | 300 | 300 | 300 |

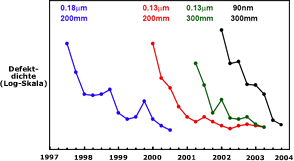

Der Prescott ist also ein Produkt des "P1262" Prozesses, der bereits im letzten Jahr zur Serienreife geführt wurde und seitdem die Lager mit Pentium 4 Prescott Prozessoren füllt. Aktuell sind Fab D1C und Fab 11X auf den 90 nm Fertigungsprozess auf 300 mm Wafern (großen Silizium-Scheiben, auf denen die Prozessorkerne mittels modernster Lithographie entstehen) umgestellt. Später in diesem Jahr folgt Fab 24 in Irland.

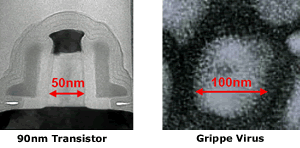

Doch was beim Prescott ist nun 90 nm groß? Ein Nanometer (nm), soviel dürfte klar sein, ist 10^-9 Meter. Ein menschliches Haar ist im Vergleich dazu in etwa 100 µm, also 10^-4 m dick. Die Größenangabe 90 nm bezieht sich im Allgemeinen auf die kleinste "Feature Size", also die Abmessungen der kleinsten Einheit eines Prozessors, dem Transistor (aktuell vom Typ CMOS). Damit ist der Transistor in etwa so groß wie ein Grippe-Virus (100nm). Das Transistor-Gate ist dabei aktuell 50 nm breit und besteht nun aus Nickel Silicide, welches sich für diese kleinen Strukturen besser eignet als das bisher verwendete Cobalt Silicide.

Durch die feineren Strukturen reduziert sich die Kapazität (also das Vermögen elektrische Ladungen zu speichern) des Transistors selbst, was – ie bereits im Athlon 64 Artikel beschrieben – in schnelleren Schaltgeschwindigkeiten mündet. Durch die Verfeinerung der Strukturen von 130 nm auf 90 nm verbessert sich die Schaltzeit um ca. 50 Prozent.

Um dem Prozessor noch mehr Dampf zu machen, hat Intel beim verwendeten Silizium etwas getrickst: Beim Prescott kommt sogenanntes gestrecktes Silizium (Strained Silicon) zum Einsatz. Diese Technik macht sich die naturgemäße Tendenz von Atomen zu Nutze, sich im Verbund gegeneinander auszurichten. Liegt Silizium oben auf einem Trägermaterial, so dehnen sich die Silizium-Atome aus, um sich mit den darunter liegenden Atomen abzugleichen. Dadurch wird das Silizium im wahrsten Sinne des Wortes gestreckt und Leitungselektronen stoßen bei ihrem Drift durch den Halbleiter auf weniger störende Gitterbausteine. Somit kommt es zu weniger Wechselwirkungen und in Folge dessen geben die Elektronen weniger kinetische Energie durch Stöße in Form von Wärme ab. Kurzum: Sie fließen schneller. Und der Kostenpunkt? Laut Intel schlagen die hierfür zur Verfertigung nötigen Schritte nur mit ca. zwei Prozent höheren Fertigungskosten zu Buche.

Desweiteren setzt Intel bei der 90nm Prozesstechnik ein neues kohlenstoffdotiertes Oxid (CDO) mit niedriger Dielektrizität (Low-K) als Dielektrikum zwischen den Leitungen (Interconnects) der Halbleiterbausteine ein. Das neue Material senkt ungewollte Kapazitäten im Vergleich zum bisher beim 130 nm Prozess verwendeten flourdotieren Siliziumoxid (SiOF) um gut 18 Prozent. Ein Vorteil dieser Technik ist die einfachere Herstellung, da dieses Dielektrikum nur in zwei Schichten übereinander aufgetragen wird.

Um die Transistorendichte neben der Verkleinerung der Transistoren an sich weiter steigern zu können, verwendet der 90 nm Prozess sieben Metalllagen für die Kupfer-Interconnects. Beim nächst kleineren Prozess (65 nm) werden es sogar acht Lagen sein. Die oberste und die unterste Isolationsschicht besteht dabei aus widerstandsfähigerem Siliziumdioxid und Siliziumnitrid (SiO2/SiN), da dies den mechanischen Belastungen besser Stand hält und hilft, die darunterliegenden Schichten zu entlasten. Die unterste Schicht direkt über den Transistoren hat eine Dicke von 150 nm, die Oberste, die den Sockel-Pins am nahsten ist, eine von 972 nm.

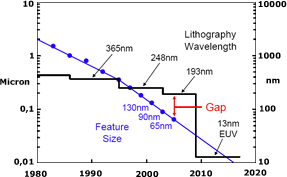

Zum Realisieren des ganzen Prozesses wird eine Kombination aus Lithographie-Ausrüstung für Lichtwellenlängen von 248 nm und 193 nm eingesetzt. Beim Northwood kam nur Licht mit einer Wellenlänge von 248 nm zum Einsatz. Gerade das ist der Punkt, an dem man ins Staunen gerät: Das Licht, welches zum Generieren der Strukturen genutzt wird, ist länger als die Strukturen selbst.

Gerade hier muss man sich besonderer lithographischer Tricks bedienen, um diesen offensichtlichen Rückstand in der Entwicklung auszugleichen. Erst im Jahre 2009 soll mit der EUV-Lithographie, bei der Licht der Wellenlänge 13,5 nm (Extremes Ultraviolett) zum Einsatz kommt, diese Lücke geschlossen werden.