AMDs „Steamroller“-Architektur und der kleine Schwenk zurück

AMDs Roadmap für die High-Performance-Prozessorarchitektur ist bereits seit fast einem Jahr klar, jetzt werden jedoch weitere Details zum Nach-Nachfolger der „Bulldozer“ bekannt: „Steamroller“. Der soll insbesondere über eine gesteigerte Single-Threaded-Leistung zurück ins Spiel kommen, bei der „Bulldozer“ arge Probleme hatte.

Anwendungen für einen Kern sind auch heute noch an der Tagesordnung. AMD hatte mit dem „Bulldozer“-Modul-Konzept darauf gebaut, dass durch eine hohe Parallelisierung die Prozessoren auch eine hohe Leistung abrufen können. Dies funktioniert bei Anwendungen wie POV-ray perfekt. Bei vielen Anwendungen ist man aber in der realen Welt noch nicht soweit, wo das Modul-Konzept mit den geteilten Ressourcen letztlich an ihre Grenzen kam und beispielsweise in iTunes mit ihren eigentlich acht „Kernen“ und deutlich höheren Taktfrequenzen gegen die günstigere Vorgängergeneration mit halb so viel Kernen bei geringerem Takt kein Land sah.

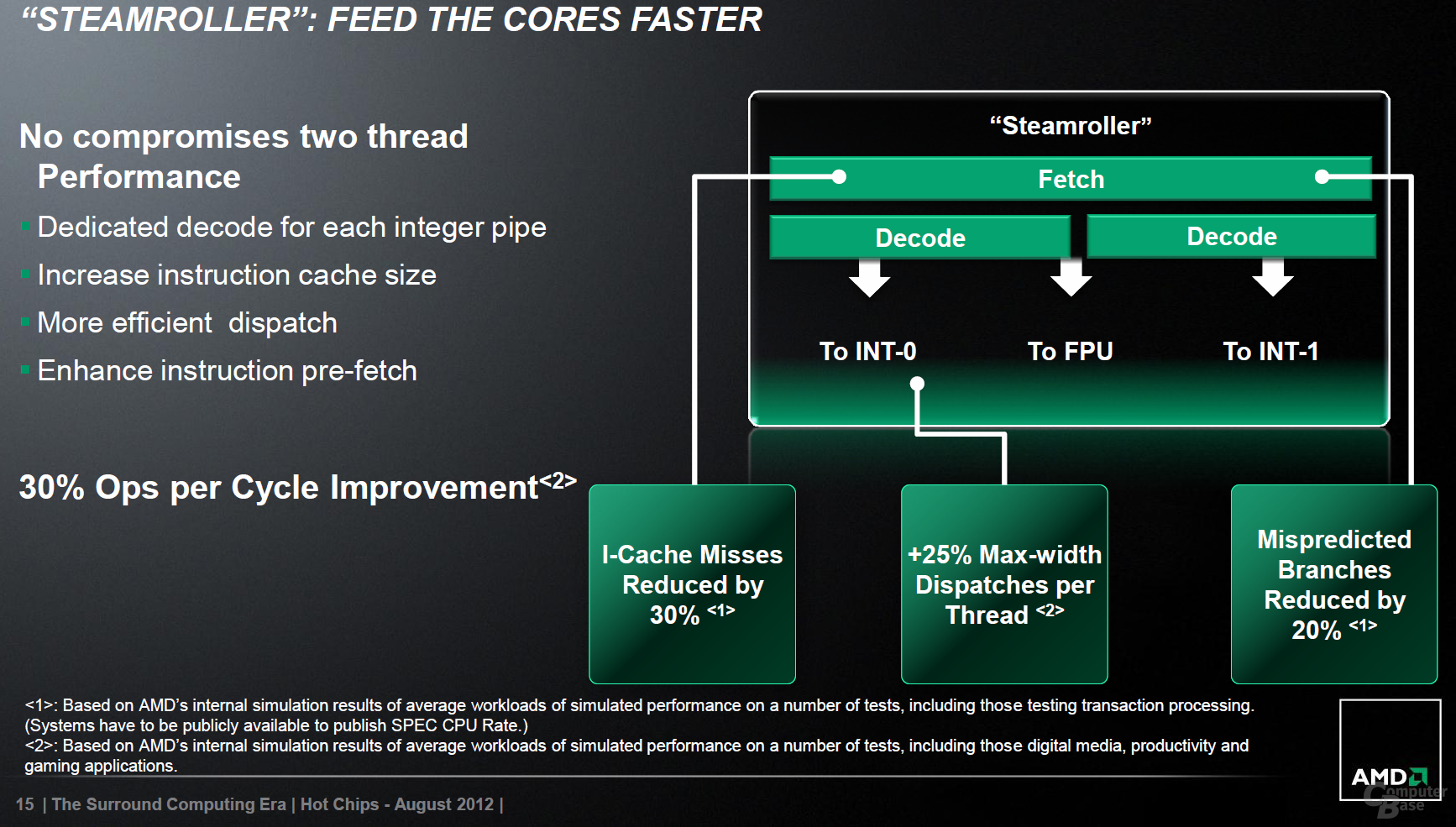

Mit „Piledriver“ geht AMD diese Baustelle bereits in diesem Jahr etwas an, bei „Steamroller“ wird das Prozedere aber erst entscheidend angepackt. So wird neben der Überarbeitung der Sprungvorhersage, die 20 Prozent weniger Fehlsprünge nach sich ziehen soll, auch der Instruktion-Cache ausgebaut und optimiert sowie der L1-Daten-Cache gehörig verbessert.

Die wohl gravierendste Änderung ist aber an anderer Stelle zu finden, die quasi einem kleinen Schwenk zurück zum klassischen CPU-Design und zurück von den vielfältig geteilten Ressourcen in einem Modul entspricht. Denn AMD weicht das Moduldesign auf, sodass statt einer Decoder-Einheit wie bei „Bulldozer“ und „Piledriver“ bei „Steamroller“ wieder zwei dieser Einheiten zum Einsatz kommen, wodurch bereits massive Vorteile erzielt werden sollen. Denn statt einer Einheit, die zwei Integer-Kerne und die Gleitkommaeinheit füttert, wird jeweils ein Decoder für einen Integer-Kern verantwortlich sein, während beide Decoder nebenbei die Gleitkommaeinheit (FPU) mit Daten versorgen.

Auch beim Drumherum wird AMD weiter Hand anlegen, sodass die vor knapp einem Jahr prognostizierte maximal 15 Prozent gesteigerte Performance pro Watt gegenüber dem Vorgänger – in diesem Fall „Piledriver“ – auch heute noch Bestand haben; ohne große Berücksichtigung der neuen 28-nm-Fertigung, auf der die „Steamroller“-basierten Produkte letztlich im kommenden Jahr setzen werden.

We expect to see up to a 15% improvement in performance per W over the "Piledriver" core (those are design-level improvements rather than process level ones).

Als erstes Produkt basierend auf der „Steamroller“-Architektur bestätigt AMD nochmals die „Kaveri“ getauften APUs, die Nachfolger der „Trinity“ werden sollen.