IBM stellt „weltweit schnellsten Chip“ vor

25 Prozent mehr reine Performance pro Prozessorkern, 30 Prozent bessere Anwendungsleistung insgesamt, dazu eine um 50 Prozent gesteigerte Gesamtkapazität – allein diese grundlegenden Informationen des neuen „zEC12“ aus IBMs aktualisierter Mainframe-Sparte beeindrucken.

Nach über drei Jahren Entwicklungszeit und über einer Milliarde Dollar an Forschungskosten hat IBM heute die Wundertüte geöffnet und den neuen Mainframe zEC12 präsentiert, der den bisherigen z196 als Flaggschiff ablösen wird. Diesem liegt aktuellste Technik zugrunde, sei es von aktualisierten CPU-Kernen über die Verwendung von Flash-Speicher bis hin zur ersten kommerziellen Nutzung von sogenanntem transactional memory.

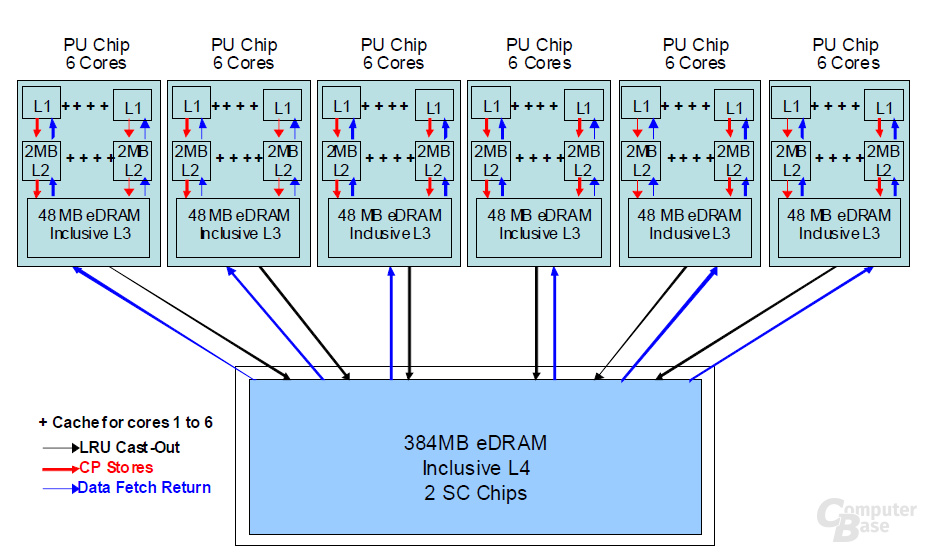

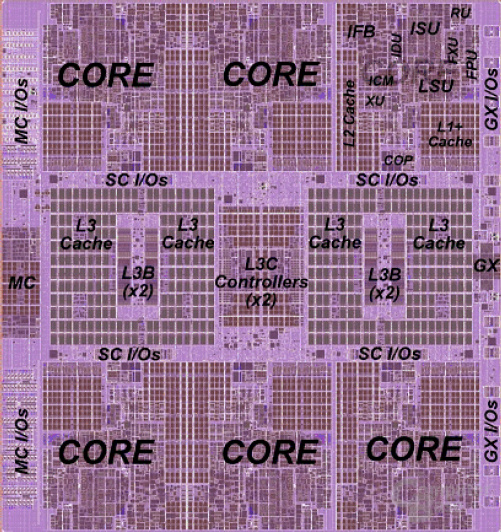

In der einfachsten Betrachtung kommen die eingangs erwähnten massiven Leistungssteigerungen von einer Aufwertung des zum Vorgänger kompatiblen Gesamtkonzepts. War der z196 im Grunde genommen ein Mainframe basierend auf Quad-Core-CPUs in Out-of-Order-Architektur bei maximal 5,2 GHz, ist der Nachfolger im zEC12 ein Sechs-Kern-Prozessor mit bis zu 5,5 GHz Takt. Weiterhin helfen ein komplett neu strukturierter L1-Cache (64 KB für Daten und 96 KByte für Instruktionen pro Kern) und ein vergrößerter L2-Cache mit 2 MByte (geteilt in jeweils 1 MB für Daten und Instruktionen pro Kern) sowie der auf 48 MByte verdoppelte L3-Cache (für alle sechs Kerne) und ein L4-Cache mit jetzt 384 MByte (pro MCM) – ebenfalls die verdoppelte Kapazität.

Die Liste der Verbesserungen gegenüber dem Vorgänger fällt für den nach IBM-Angaben schnellsten Chip der Welt umfassend aus. Kleine Notiz am Rande: Das deutsche Hardware-Team aus dem IBM Forschungs- und Entwicklungszentrum in Böblingen hat circa 50 Prozent des neuen Prozessor-Kerns sowie etwa ein Drittel des gesamten Prozessor-Chips entwickelt.

- Balanced Performance Growth

- 1.5 times more system capacity

- 50% more cores in a central processor chip

- Maximum number of cores increased from 96 to 120

- 3rd Generation High Frequency processor

- Frequency increased from 5.2 GHz to 5.5 GHz

- Up to 25% faster uniprocessor performance as compared to z196

- Innovative Local Data-Cache design with larger caches but shorter latency

- Total L2 per core is 33% bigger

- Total on-chip shared L3 is 100% bigger

- Unique private L2 cache (1 MB) design reduces L1 miss latency

- 2nd Generation of Out of Order design (OOO) with increased resources and efficiency

- Numerous pipeline improvements based on z10 and z196 designs

- Number of instructions in flight is increased by 25%

- Improved Instruction Fetching Unit

- New 2nd level Branch Prediction Table with 3.5 times more branches

- Improved sequential instruction stream delivery

- Dedicated Co-processor per core with improved performance and additional capability

- New hardware support for Unicode UTF8<>UTF16 bulk conversions (CU12/CU21)

- Improved start-up latency

- Multiple innovative architectural extensions for software exploitation

- Transactional Execution (TX), known in the academia as Hardware Transactional

Memory (HTM)

Allows SW-defined “lockless” sequences to be treated as an atomic “transaction” and

improves efficiency on highly-parallelized applications and multi-processor handling - Run-time Instrumentation

Allows dynamic optimization on code generation as it is being executed - Enhanced Dynamic Address Translation-2 (EDAT-2)

Supports 2 GB page frames

- Increased Issue / Execution / Completion throughput

- Improved instruction dispatch and grouping efficiency

- Millicode Handling

- Next Instruction Access Intent

- Load and Trap instructions

- Branch Prediction Preload

- Data Prefetch

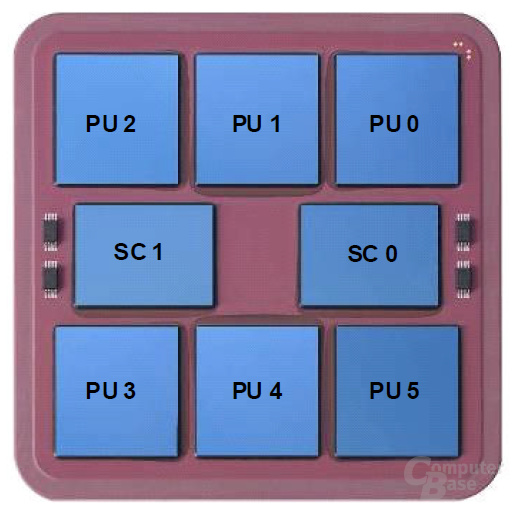

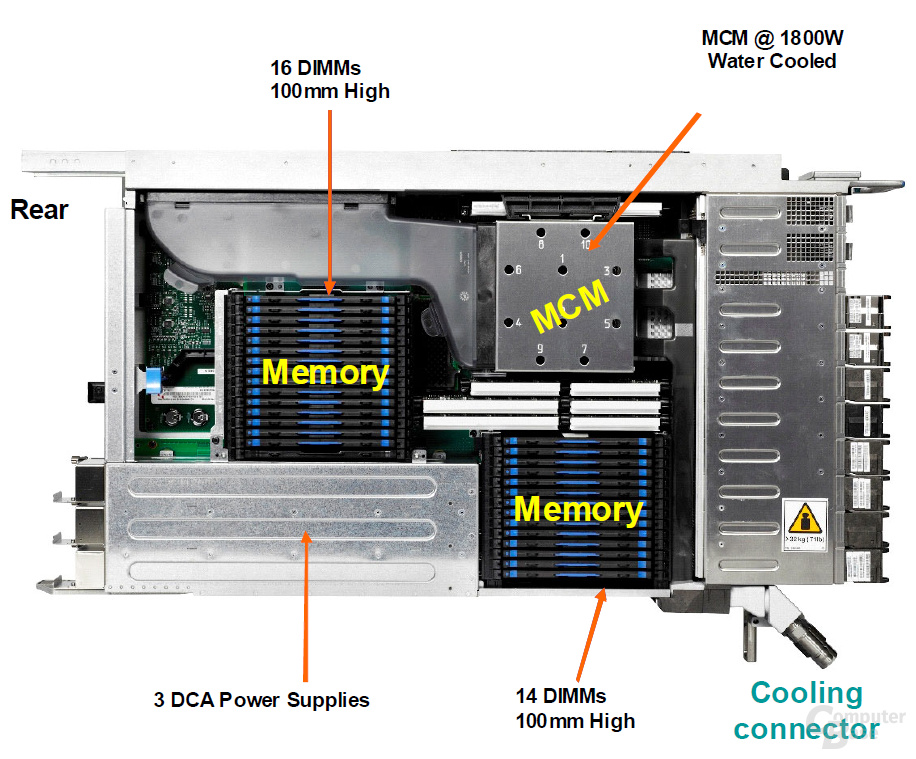

Jeder der einzelnen Sechs-Kern-Prozessoren wird im 32-nm-SOI-Verfahren gefertigt und weist bei einer Menge von 2,75 Milliarden Transistoren eine Die-Größe von 597,24 mm² auf. Durch Zusammenschaltungen über Multi Chip Module (MCM) wie beim Vorgänger stehen insgesamt 120 nutzbare Kerne zur Verfügung. Sechs der Sechs-Kern-Prozessoren werden dafür zusammen mit zwei Storage-Controllern, die jeweils 192 MB eDRAM als L4-Cache beisteuern und ihrerseits so auch noch einmal 525,6 mm² groß sind, auf eines dieser MCMs gepackt.

Vier dieser MCMs können am Ende in einem Mainframe zusammen geschaltet werden, von den eigentlich 144 Prozessorkernen werden letztlich jedoch nur 120 genutzt. Der L4-Cache hat damit eine Gesamtgröße von 1.536 MByte und soll dadurch bereits eine Vielzahl von Daten bearbeiten können, ehe sie im maximal 3 TByte großen Hauptspeicher landen und noch weiter geleitet werden.

Zur Leistungssteigerung des Gesamtsystems trägt auch der neue Flash-Speicher bei. 1,6 TByte große Karten werden aufgrund von Redundanz und hoher Performance immer zweifach verbaut, vier dieser (doppelten) Karten können in einem zEC12 genutzt werden, was die Gesamtkapazität des Mainframe auf 6,4 TByte schnellen NAND-Flash als Massenspeicher erhöht. Erst danach kommen die klassischen Speicherlösungen über PCI Express, InfiniBand, Fibre Channel & Co. zum Einsatz. Zudem wird nach dem kürzlichen Einsatz der Transactional-Memory-Technologie im IBM Blue Gene/Q-Sequoia System als derzeit schnellsten Rechner der Welt auch im zEC12 diese Technologie für den Mainframe adaptiert, um Software zu befähigen, parallel laufende Berechnungen, die gemeinsame Datensätze nutzen, besser zu unterstützen.

Auf der Habenseite bietet der Neuling auch einen manipulationsresistenten kryptografischen Co-Prozessor (Crypto Express4S), der für die Absicherung von Transaktionen und sensiblen Daten zuständig ist. Der Kryptoprozessor enthält eine neu entwickelte Firmware, die die Sicherheitsanforderungen verschiedener Branchen und Regionen abdeckt. Zum Beispiel kann er dazu konfiguriert werden, digitale HQ-Signaturen zu unterstützen, die für Anwendungen im Umfeld intelligenter Pässe, Ausweise und gesetzlicher Onlineanwendungen eingesetzt werden. Damit lassen sich bisherige handschriftliche Unterschriften, wie von der EU und häufig im öffentlichen Sektor benötigt, ersetzen. Laut IBM sind die z-Server die einzigen kommerziellen Serversysteme, die die Sicherheitsklassifizierung Common Criteria Evaluation Assurance Level 5+ erreicht haben.

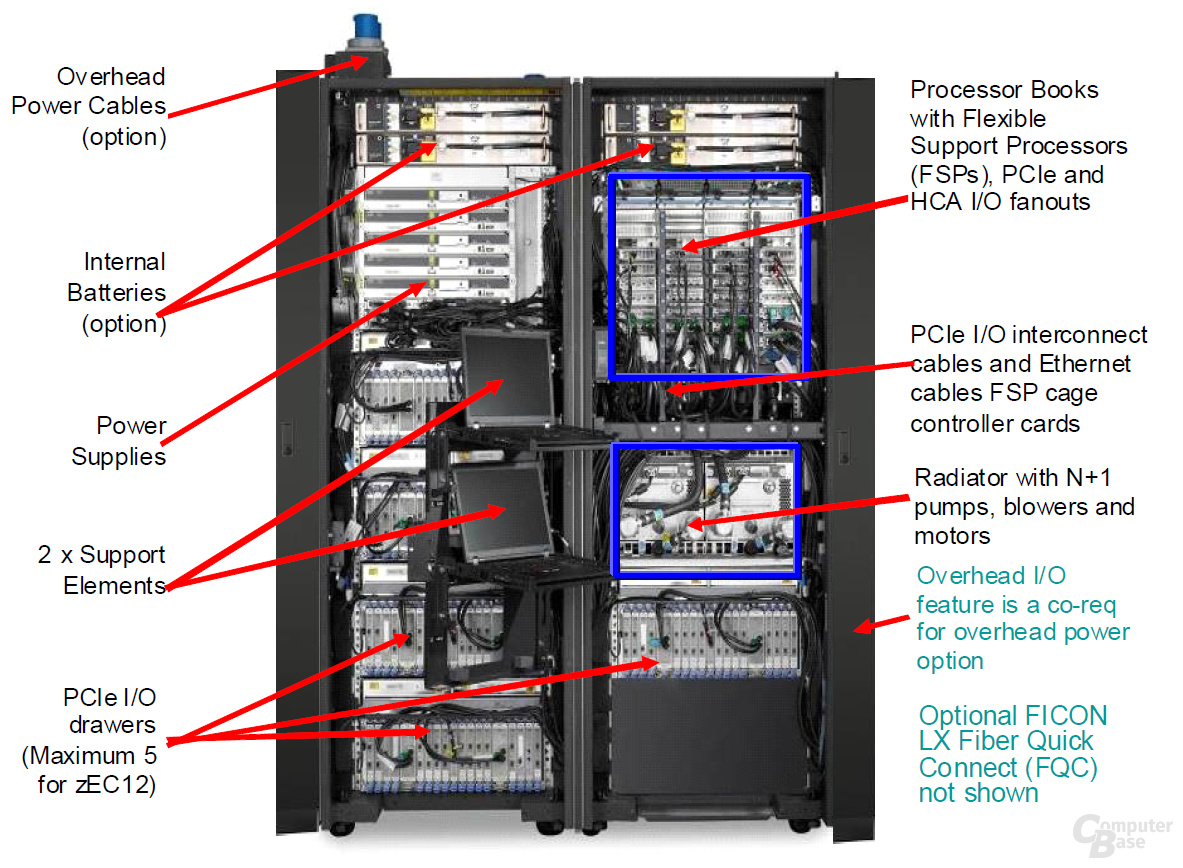

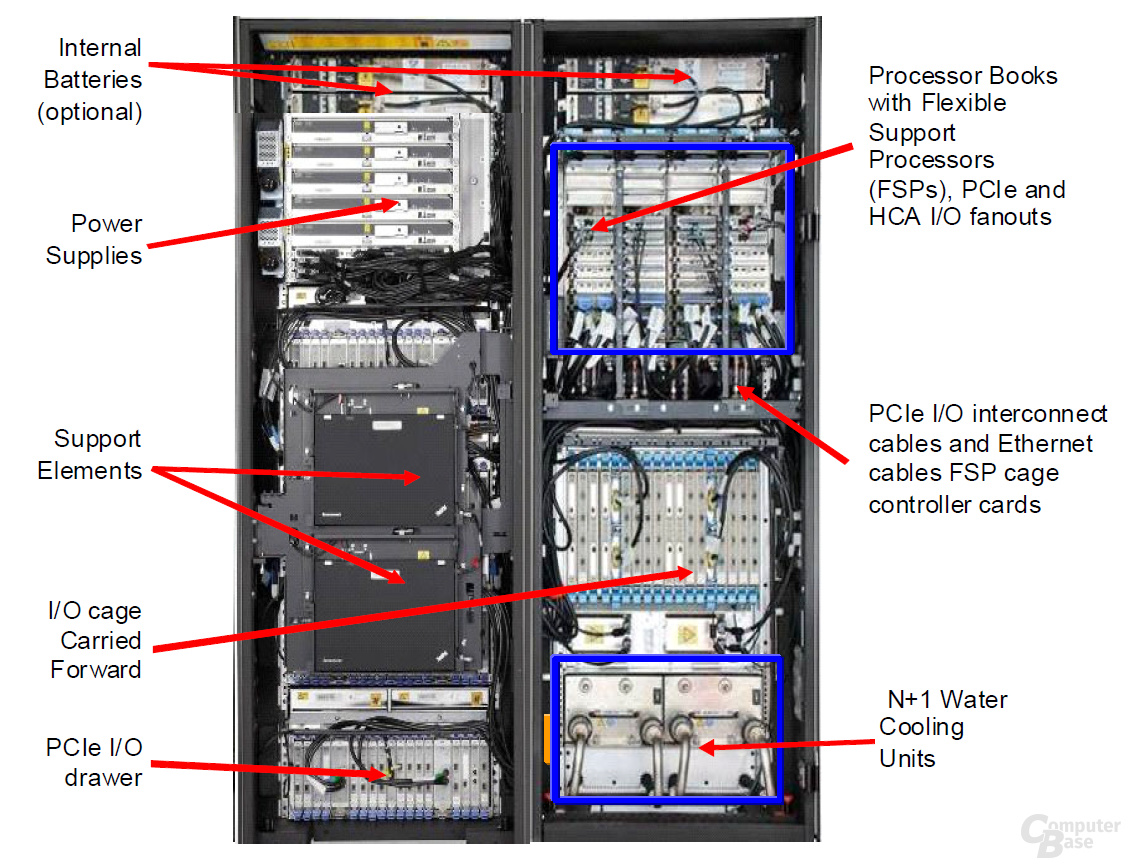

Unterm Strich soll der zEC12 trotz der größeren Leistung in etwa die gleiche Leistungsaufnahme wie der Vorgänger z196 haben (beginnend bei 1.800 Watt pro MCM), in der Maximalkonfiguration sind es laut IBM jedoch fünf Prozent mehr. Wie zuvor werden auch diesmal Luft- und Wasserkühlungsoptionen angeboten, einhergehend mit der Neuerung, dass Leitungen und auch Kabel von oben an den Mainframe herangeführt werden, sodass die Systeme auch auf herkömmlichen Betonböden platziert werden können.

Zusammenfassend erklärt IBM den zEC12 samt Einsatzgebiet wie folgt: