Intel Xeon D: Broadwell-DE als echter SoC in 14 nm mit bis zu acht Kernen

Vor fast genau einem Jahr enthüllte Intel die Entwicklung von „Broadwell-DE“ als SoC für den Server-Markt, in den letzten Wochen kamen viele kleinere Informationen hinzu. Ein Überblick über die Mitte 2015 als Xeon D erscheinenden Prozessoren für diverse Aufgabengebiete.

SoC ist gerade bei klassischen Prozessoren bereits ein häufig genutzter Begriff, oft jedoch an falscher Stelle. Denn im klassischen System-on-a-Chip sollen, wie die Bezeichnung bereits verrät, alle Funktionen in einem einzigen Chip vereint sein. Bisher sahen das Hersteller nicht so genau, funktionale Auslagerungen wie beispielsweise beim Multi-Chip-Modul (MCM) der aktuellen U/Y-Serie an Intel-CPUs, bei denen der Chipsatz neben der CPU auf dem gleichen Trägermaterial sitzt, werden weitläufig ebenfalls als SoC bezeichnet.

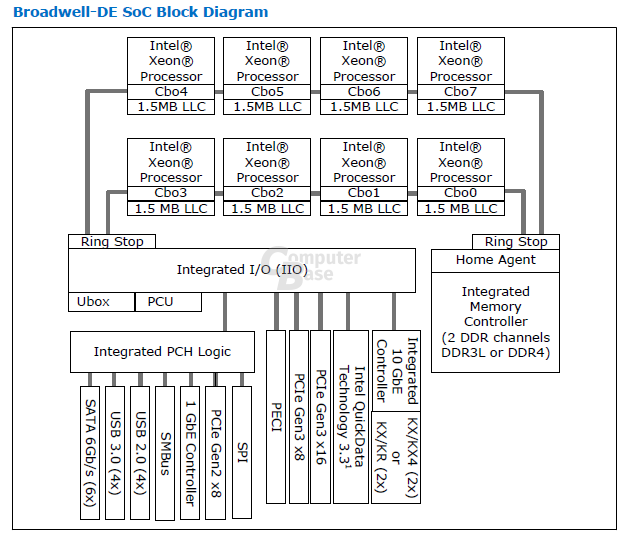

Vorab war deshalb fraglich, was „Broadwell-DE“ alias Xeon D sein wird, doch bereits seit einiger Zeit steht fest: Es ist ein echter SoC mit bis zu acht Kernen, integriertem Chipsatz, LAN und allem was dazugehört. Als Zielgruppe hat Intel mit den Xeon D und der „Grangeville“- Plattform Microserver, Storage-Systeme als auch den Kommunikationsmarkt im Visier, für die am Design jeweils leichte Anpassungen vorgenommen werden. Das Grundgerüst ist jedoch bei allen identisch.

Herzstück der Xeon D sind die bis zu acht Kerne inklusive Hyper-Threading-Unterstützung und einem Turbo-Modus. Die CPU-Architektur basiert dabei auf dem überarbeiteten „Haswell“-Kern in 14 nm, „Broadwell“, weshalb alle modernen Features wie AVX2, AES, TSX und alle Virtualisierungsfunktionen ebenfalls mit an Bord sind. Pro Kern stehen zudem maximal 1,5 MByte L3-Cache zur Verfügung, die Slices genannten Einzelstücke werden zusammen über alle Kerne als gemeinsam genutzter 12 MByte großer L3-Cache fungieren.

Am Ringbus, der seit „Sandy Bridge“ in allen modernen Intel-Prozessoren zum Einsatz kommt, werden Kerne und L3-Cache mit dem UnCore-Bereich wie dem Home Agent inklusive integriertem Speichercontroller (IMC) für bis zu 128 GByte DDR3L- oder DDR4-Speicher mit ECC-Unterstützung und der I/O-Schnittstelle verbunden. An letzterer hängen die Anschlüsse für die Außenwelt wie auch der erstmals komplett integrierte Chipsatz (Plattform Controller Hub, PCH).

Spezifiziert wurden von Intel vorab gleich sechs TDP-Klassen von 15 bis 45 Watt – jeweils in 5-Watt-Schritten. Dabei werden unterschiedlichste Einsatzgebiete inklusive derer mit großen Temperaturschwankungen abgedeckt. Um den Szenarien gerecht zu werden, wird Intel neben einer fest verlöteten BGA-Variante mit 1.272 Kontaktpunkten auch einen sockelbaren Ableger mit 1.667 Pins auflegen. CPU-World hat in dieser Woche die ersten neun Modelle grob spezifiziert, Details zur Unterstützung von Hyper-Threading sowie den Taktraten mit und ohne Turbo gibt es aber noch nicht. Vor dem Sommer 2015 ist kaum mit einer Einführung zu rechnen, im Frühjahr startet „Broadwell“ erst einmal in Notebooks, später folgt dann der restliche Markt inklusive Desktop.

| Bezeichnung | Kerne | TDP | Zielgruppe |

|---|---|---|---|

| Xeon D | 8 | 45 W | Microserver |

| Xeon D | 8 | 45 W | Microserver |

| Xeon D | 8 | 35W / 45 W | Kommunikation/Storage |

| Xeon D | 6 | 45 W | Microserver |

| Xeon D | 6 | 35 W | Kommunikation/Storage |

| Xeon D | 4 | 45 W | Microserver |

| Xeon D | 4 | 25 W / 35W | Kommunikation/Storage |

| Xeon D | 2 | 25 W | Kommunikation/Storage |

| Pentium | 2 | <20 W | Kommunikation/Storage |