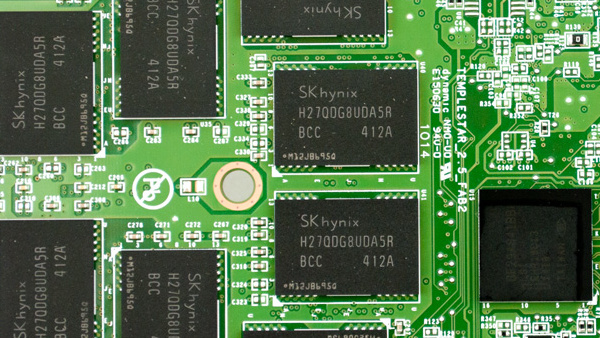

SK Hynix: 3D-NAND-Produktion in Serie – 256 Gbit folgt Q1 2016

Noch in diesem Jahr wird SK-Hynix mit der Serienfertigung von 3D-NAND beginnen. Den Anfang machen 128-Gigabit-Chips des Typs 2-Bit-MLC, die über 36 übereinander liegende Zellschichten verfügen. Im ersten Quartal 2016 soll eine TLC-Version mit 3 Bit pro Zelle, 48 Ebenen und der doppelten Kapazität von 256 Gbit folgen.

In Kleinauflage hatte SK Hynix den 128-Gbit-3D-NAND bereits im dritten Quartal produziert. Im heimischen Südkorea hat Firmenchef Park Sung-wook auf einer Industriemesse nun offiziell angekündigt, dass die Massenfertigung in diesem Jahr erfolgt. Auch im aktuellen Produktfahrplan ist die Verfügbarkeit der ersten 3D-NAND-Chips (3D-V2) für das vierte Quartal 2015 vorgemerkt. Mit dem Einsatz in Endprodukten ist aber in der Regel erst Monate später, also voraussichtlich ab dem kommenden Jahr zu rechnen.

Für die TLC-Variante mit 48 Lagen und 256 Gigabit nannte der CEO grob das kommende Jahr. Im Databook (PDF-Datei) tauchen die 256-Gbit-Chips aber bereits als „3D-V3“ auf und sind demnach ab dem ersten Quartal 2016 zu erwarten.

| 3D-NAND | Ebenen | Kapazität | Produktion/Verfügbarkeit |

|---|---|---|---|

| SK Hynix 3D NAND | 36 | 128 Gbit (MLC mit 2 Bit/Zelle) | Q4 2015 / 2016 |

| SK Hynix 3D NAND | 48 | 256 Gbit (TLC mit 3 Bit/Zelle) | Q1 2016 / ? |

| Samsung V-NAND Gen 3 | 48 | 256 Gbit (TLC mit 3 Bit/Zelle) | August 2015 / ? |

| Samsung V-NAND Gen 2 | 32 | 86/128 Gbit (MLC mit 2 Bit/Zelle) 128 Gbit (TLC mit 3 Bit/Zelle) |

Mai 2014 / H2 2014 |

| Samsung V-NAND Gen 1 | 24 | 128 Gbit (MLC mit 2 Bit/Zelle) | August 2013 / H2 2013 |

| Toshiba/SanDisk BiCS | 48 | 128 Gbit (MLC mit 2 Bit/Zelle) | H2 2015 / 2016 |

| Toshiba/SanDisk BiCS | 48 | 256 Gbit (TLC mit 3 Bit/Zelle) | H1 2016 / 2016 |

| Intel/Micron 3D NAND | 32 | 256 Gbit (MLC mit 2 Bit/Zelle) 384 Gbit (TLC mit 3 Bit pro Zelle) |

Q4 2015 / 2016 |

3D-NAND ist anders als herkömmlicher NAND-Flash mit nur einer Zellebene in mehreren übereinander liegenden Schichten aufgebaut. Diese Layer sind vertikal mittels TSV-Technik verbunden, ähnlich wie es bei Stacked-DRAM der Fall ist. Während bei planarem „2D“-NAND-Flash immer kleinere Strukturbreiten zur Steigerung der Kapazität pro Chip eingesetzt werden, können bei 3D-NAND größere Strukturen beibehalten werden. Die größeren Zellabstände begünstigen eine höhere Haltbarkeit. Der 3D-NAND bietet zudem auch Vorteile bei Leistung und Effizienz.

Samsung ist der Konkurrenz bei 3D-NAND um Jahre voraus und produziert den 3D-Speicher bereits seit 2013 in Serie. Im August hatte Samsung schon mit der Fertigung der dritten Generation mit 256 Gigabit (TLC) auf 48 Ebenen begonnen. Neben SK Hynix stehen auch Intel und Micron sowie SanDisk und Toshiba vor der Markteinführung ihrer ersten kommerziellen 3D-NAND-Generation.

Abseits von NAND-Flash will SK Hynix nach Informationen von ZDNet.co.kr zudem die Produktion von DRAM im neuen 20-nm-Verfahren ausbauen. Nach anfänglichen Problemen habe sich die Produktionsrate inzwischen „stabilisiert“, Muster-Chips seien bereits auf dem Weg zu Kunden. Die Herstellung der 20-nm-Chips erfolgt in der neuen Fabrikanlage M14 in Südkorea, bei der es sich laut SK Hynix um die größte DRAM-Fabrik der Welt handele. Für die kommenden Jahre plant SK Hynix Ausgaben in Höhe von rund 26 Milliarden US-Dollar für den Ausbau und die Errichtung neuer Fertigungsanlagen. Bei DRAM ist SK Hynix der zweitgrößte Hersteller hinter Speichermarktführer Samsung.