Chipfertigung: Fortschritte und Innovationen in der Fertigung I

2/3In der Vergangenheit wurden zahlreiche Einzelschritte als Verbesserungen in die Fertigung eingeführt, die mal die verwendeten Materialien und mal die Form des Transistors betrafen. Die Erklärung der Hintergründe der einzelnen Schritte endet schnell in jeder Menge Text, allerdings lassen sich fast alle Verbesserungen auf eine einzige Formel zurückführen, die deswegen hier vorgestellt wird.

Diese fundamentale Formel beschreibt die Dichte der elektrischen Ladungsträger ΔN, die sich am Gate ansammeln müssen, damit der Transistor schaltet:

ΔN = ε0/e*V/d²*ϰ

Die Permittivität des Vakuums ε0 sowie die Elektronenladung e sind Naturkonstanten, die hier nicht weiter behandelt werden müssen. Wichtiger sind V, die Transistorspannung, die ans Gate angelegt wird, und d, die Dicke der Oxidschicht unter dem Gate. ϰ (Kappa) ist die Dielektrizitätszahl des Isolators, die den Einfluss des Oxidmaterials auf die Ladungsträgerdichte angibt.

Die Dicke der isolierenden Oxidschicht

V/d² beschreibt also das Verhältnis aus der Transistorspannung am Gate im Verhältnis zur quadratischen Dicke der Oxidschicht unter dem Gate. Es fällt auf, dass ΔN größer wird, je kleiner d ist. Andersherum formuliert: Wenn immer die gleiche Ladungsträgerdichte zum Schalten benötigt wird, kann mit sinkender Oxidschichtdicke auch die Transistorspannung geringer ausfallen. Dies ist einer der Beiträge, warum verbesserte Fertigungen, die die Oxidschichtdicke verringern, weniger Leistungsaufnahme haben. Besonders auffällig ist das bei der Entwicklung der Spannung für SDRAM-Module. Da die Leistungsaufnahme quadratisch von der Spannung abhängt, machen sich selbst kleine Veränderungen bemerkbar.

Defektdichte und Abscheidungsverfahren

Die Schwierigkeit bei der Verringerung der Oxidschichtdicke ist allerdings nicht nur die wiederholbare Herstellung geringer Schichtdicken, sondern auch eine geringe Anzahl von Defekten. Defekte in einer Oxidschicht entstehen entweder durch Verunreinigungen oder Fehlstellen und können dazu führen, dass die Schicht nicht mehr ausreichend isoliert und ein Kurzschluss entsteht. Dadurch wird der Transistor unbrauchbar und der Chip muss beschnitten werden, um die restlichen Transistoren verwenden zu können. Je dünner die Oxidschicht, desto wahrscheinlicher ist es, dass ein Defekt groß genug ist, um einen Kurzschluss zu verursachen. Zusätzlich steigen mit sinkender Dicke die Leckströme.

Die Defektdichte aktueller Prozesse gibt TSMC mit Werten um 0,09 Defekten pro cm² an, wobei hiermit der gesamte Wafer mit allen Prozessen gemeint ist. Dies ist nur in hochreinen Räumen möglich, die nicht von Menschen betreten werden. Ein defekter Transistor kann einen defekten Chip bedeuten, der eventuell durch das Abschalten der betroffenen Einheiten als nicht voll aktiver Chip trotzdem noch verwendet werden kann. Wie viele der auf einem Wafer belichteten Chips funktionsfähig sind, wird mit der so genannten Yield-Rate (Ausbeute) ausgedrückt.

Einen Einfluss auf die Defektfreiheit der Oxidschicht hat auch das verwendete Abscheidungsverfahren. Der Industriestandard war lange Zeit die plasmaunterstützte chemische Gasphasenabscheidung (Plasma-enhanced chemical vapour deposition, PECVD). Dabei wird ein Grundstoff wie Silan (SiH4) mit einem Sauerstoff-Plasma (O2) gemischt, um Quartz (SiO2) zu erhalten. Wird anstelle des Sauerstoffs ein Stickstoff-Plasma (N2) verwendet, entsteht Siliziumnitrid (Si3N4). Der energiereiche Plasmazustand sorgt dabei für eine besonders saubere und schnelle Reaktion. Die Abscheidung erfolgt dabei sehr gerichtet von oben, so dass Seitenwände nicht oder nur wenig bedeckt werden.

Deutlich moderner ist die Atomlagenabscheidung (Atomic Layer Deposition, ALD). Hierbei wird ein Material kontrolliert Atomlage für Atomlage aufgebaut, wodurch hochpräzise sehr dünne Schichten erzeugt werden können. Durch die feine Kontrolle ist die Wahrscheinlichkeit von Fehlstellen stark verringert. Außerdem wächst das Material auch an Seitenwänden atomgenau auf, was die Erstellung von 3D-Strukturen ermöglicht. ALD hat jedoch den Nachteil, dass nur für eine begrenzte Anzahl von Materialien entsprechende Ausgangsstoffe existieren, die eine kontrollierte Reaktion zulassen. Außerdem ist das Verfahren ausgesprochen langsam. So kann der Autor aus eigener Erfahrung sagen, dass eine Schicht aus 100 nm SiO2 mit PECVD innerhalb von 1–2 Minuten erstellt ist, während die gleiche Dicke Hafniumoxid (HfO2) mit ALD mehrerer Stunden bedarf.

Die verwendeten Materialien

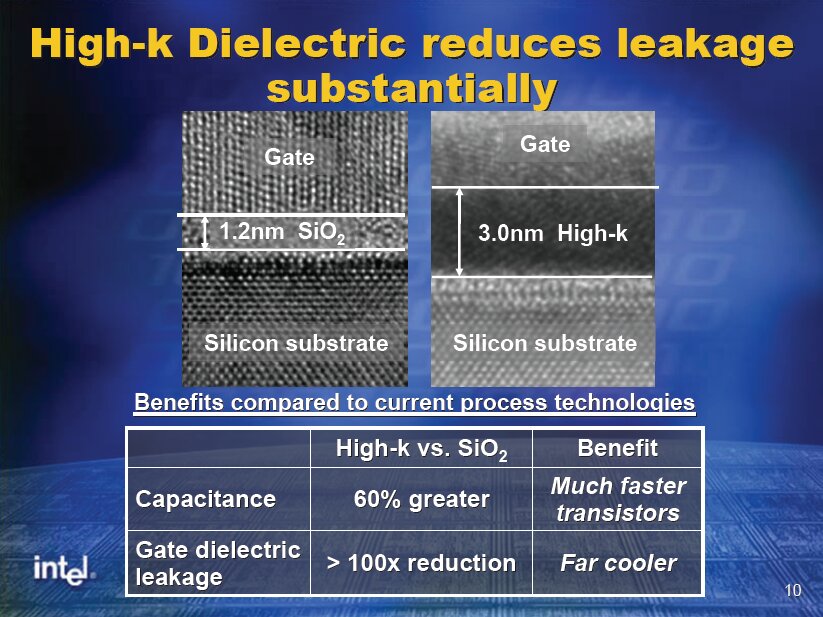

Eine weitere Variable in der oben aufgeführten Formel ist Kappa ϰ. Die Spannung, die auf das Gate unseres Transistors einwirkt, bewegt nicht immer gleich viele Ladungsträger, sondern es hängt davon ab, welches Oxid als Isolator verwendet wird. So hat Quartz eine Dielektrizitätszahl von 3.9, während sie bei Siliziumnitrid 7 ist. Materialien, deren Dielektrizitätszahl hoch ist, werden als High-k-Dielektrikum bezeichnet, da das griechische ϰ oft zu einem k vereinfacht wird. HfO2 besitzt die außerordentlich hohe Dielektrizitätszahl von 25, wodurch sich gegenüber Quartz ein Faktor von 6,4 ergibt. Beim Wechsel von Quartz zu HfO2 kann sich also die Transistorspannung auf ein Sechstel verringern oder die Dicke der Oxidschicht auf ein Sechsfaches erhöhen, was wie oben erwähnt die Sicherheit gegen Defekte erhöht. In der Praxis werden beide Faktoren kombiniert.

Beim 45-nm-Prozess gelang Intel im Jahr 2007 ein großer Sprung durch die Verwendung von ALD mit HfO2 . Außerdem gab Intel an, erfolgreich Metallkontakte für das Gate verwendet zu haben. Dies wurde notwendig, da die zuvor genutzten polykristallinen Silizium-Leiterbahnen nicht auf HfO2 haften. Dass Metallkontakte überhaupt als Problem galten, liegt daran, dass Metalle nicht CMOS-kompatibel sind, sie reagieren also aggressiv auf Halbleiterverbindungen und diffundieren in diese hinein. Würde man Goldkontakte nutzen, wären die Eigenschaften des Transistors nach kurzer Zeit verändert.

Welches Material Intel tatsächlich für die Gatekontakte nutzt, wurde nicht veröffentlicht. Zur gleichen Zeit erlangte allerdings Titannitrid (TiN) als CMOS-kompatibles und hoch leitfähiges Material Bekanntheit, weshalb es sehr wahrscheinlich ist, dass es der aktuelle Standard für Gatekontakte ist. TiN ist chemisch gesehen eine Keramik, allerdings gilt es durch die hohe Leitfähigkeit bei elektrischer Betrachtung als Metall.

Jahre später versuchte Intel beim 10-nm-Prozess erneut durch die Einführung eines neuen Materials für die Interconnects, nämlich Kobalt, den Vorsprung gegenüber der Konkurrenz auszubauen. Wie mittlerweile nur allzu gut bekannt ist, verhob sich der Konzern damit allerdings erheblich. Der Prozess wurde erst in den letzten Jahren marktreif.