Intel stellt neue „Silvermont“-CPU-Architektur vor

AMDs „Jaguar“ pirscht bereits durch den Vorgarten, ARMs Produkte sind überall in Stellung – kein Platz mehr für Intels immer noch aktuelle aber bereits überholte Atom-Generation. Diese Gefahr hat auch Intel erkannt und stellt heute mit der „Silvermont“-Architektur die firmeneigene Antwort darauf vor.

Der Termin ist dabei strategisch gut gewählt, soll doch unter anderem AMDs Neuling bereits in den nächsten paar Wochen offiziell im Handel verfügbar sein. Bei Intels neuen Atom-Modellen sieht das etwas anders aus, denn diese werden laut Hersteller erst Ende 2013 in Tablets, Notebooks und Desktops verfügbar, Anfang 2014 folgen dann Smartphone-Varianten. Als erstes könnten eventuell Server-Ableger in Erscheinung treten, hier spricht Intel vom zweiten Halbjahr 2013. Dies hindert den Chipriesen jedoch nicht, zumindest auf dem Papier bereits einmal den Neuling ausführlich vorzustellen.

Im kalifornischen Santa Clara hat Intel in der letzte Woche erste Pressevertreter von der neuen „Silvermont“-Architektur in Kenntnis gesetzt. Wie die Gerüchteküche vorab bereits zu berichten wusste, steht dabei ein Bruch mit den Vorgängern an, da Intel von einem In-Order- zu einem fortschrittlichen Out-of-Order-Design wechselt, wie es die in diesem Marktsegment starken „Brazos“ und dessen Nachfolger „Jaguar“ aus dem Hause AMD ebenfalls nutzen.

Die Architektur im Überblick

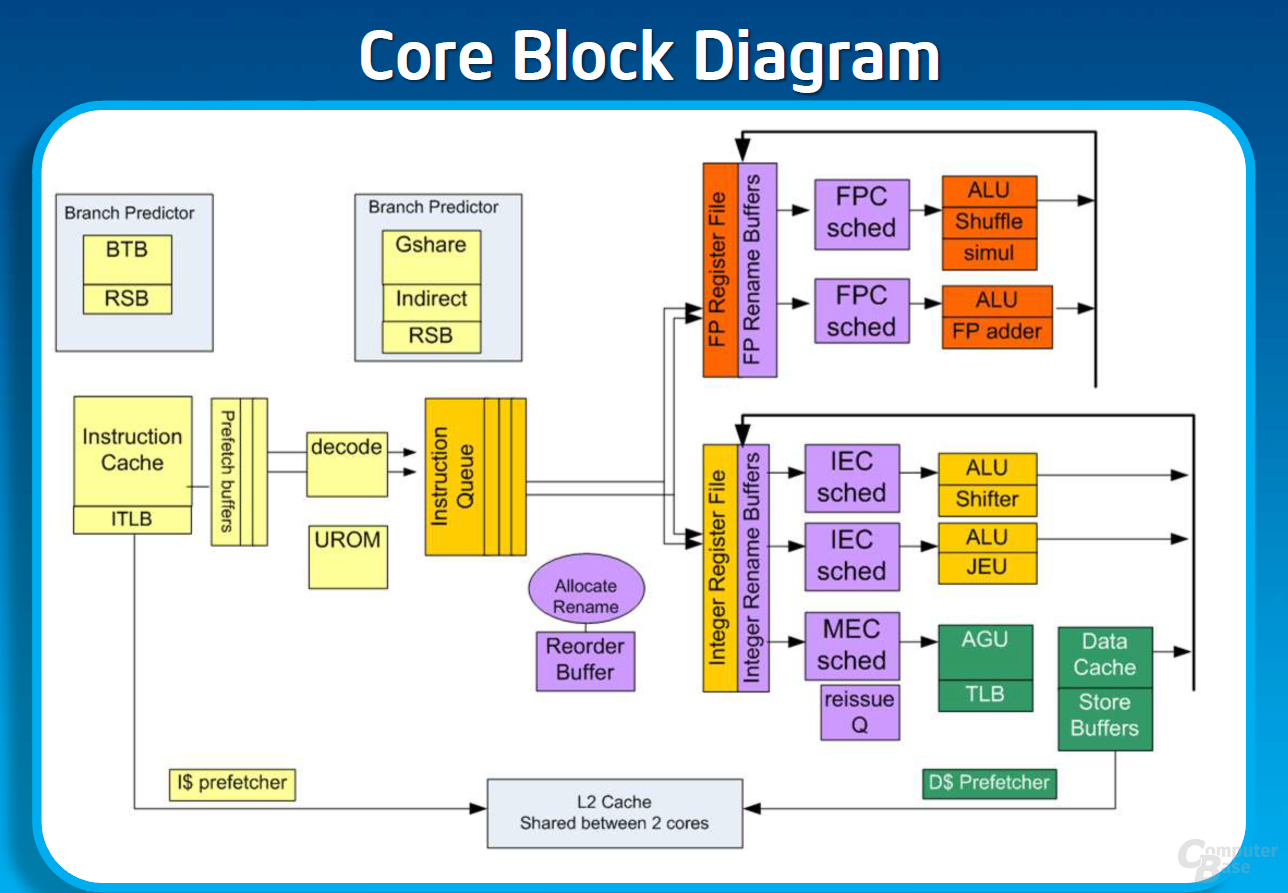

Wie üblich steht und fällt ein Prozessor bereits mit der Sprungvorhersage. Dort bieten sich für Architekten große Spielräume für Optimierungen an, denn immer wenn ein Sprung (engl. Branch, d.h. eine Berechnung) falsch vorher gesagt wird, muss die gesamte Pipeline geleert werden. Dies reduziert nicht nur die Performance, auch bereits investierte Energie geht verloren. Beim „Silvermont“ wurden im sogenannten „Front End“ nun unter anderem die Decoder optimiert sowie die Vorhersagen für indirekte Sprünge völlig überarbeitet. Zusammen mit der insgesamt umfangreicher ausfallenden Sprungvorhersage soll das „Back End“ jederzeit ausreichend Befehle (Ops) erhalten, denn je reibungsloser und besser der Datenstrom funktioniert, desto effektiver und schneller wird ein Prozessor. Dazu zählen auch ein 32 KByte großer L1-Instruction-Cache sowie die beiden Decoder, die aus x86-Befehlen die Macro-Ops machen, zwei Instruktionen pro Zyklus weiterleiten und die Instruction Queue als maximal 32 Macro-Ops großen Loop Stream Buffer ausführen. Befinden sind im Loop Stream Buffer die Befehle, die weiterhin gebraucht werden, kann die Fetch- und Decoder-Einheit abgeschaltet werden um Strom zu sparen.

Auf der Seite des „Back End“ wurden die Ausführungseinheiten komplett überarbeitet. Hier kommt jetzt das neue Out-of-Order-Design mit dem Renaming der Register und dem Reorder Buffer zum Zuge. Neben der beiden Gleitkommaeinheiten (FPU) arbeiten die zwei Integer-Ausführungseinheiten (IEC) parallel zu der des Speichers (MEC). Darüber hinaus wurde neben einem größeren TLB auch das sogenannte store to load forwarding, das langsame Hauptspeicherzugriffe minimieren soll, überarbeitet. Load/Store-Operationen können parallel ausgeführt werden.

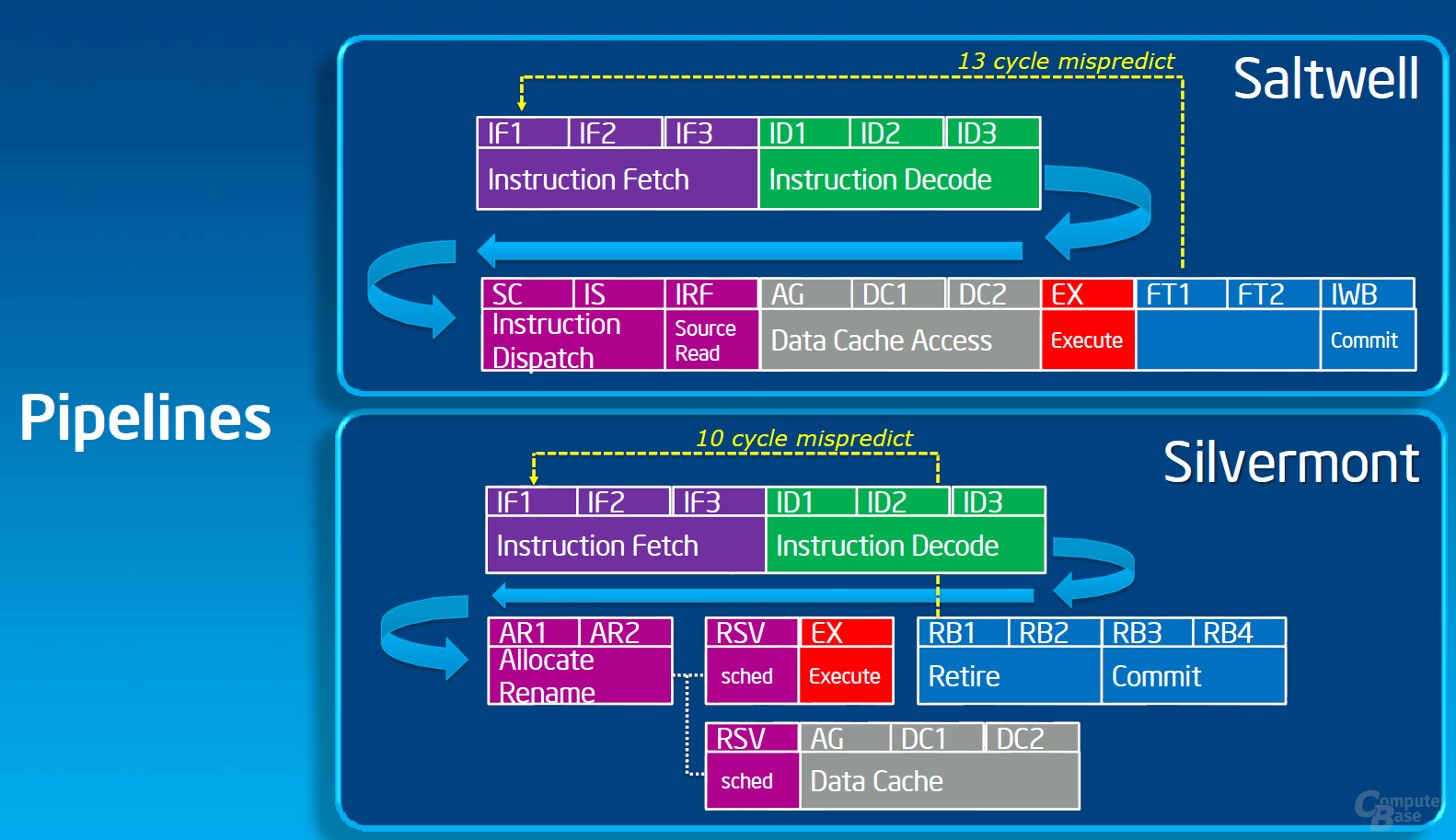

Die gesamte Integer-Pipeline verkürzt sich bei den „Silvermont“ gegenüber den „Saltwell“ von 13 auf 10 Zyklen, wobei die Zugriffe auf den Daten-Cache nicht einbezogen sind. Besagter L1-Daten-Cache ist in diesem Bereich 24 KByte groß, was keine Änderungen zum Vorgänger bedeutet. Da dieser jedoch ebenfalls mit optimiert wurde, ist nur die Menge noch identisch.

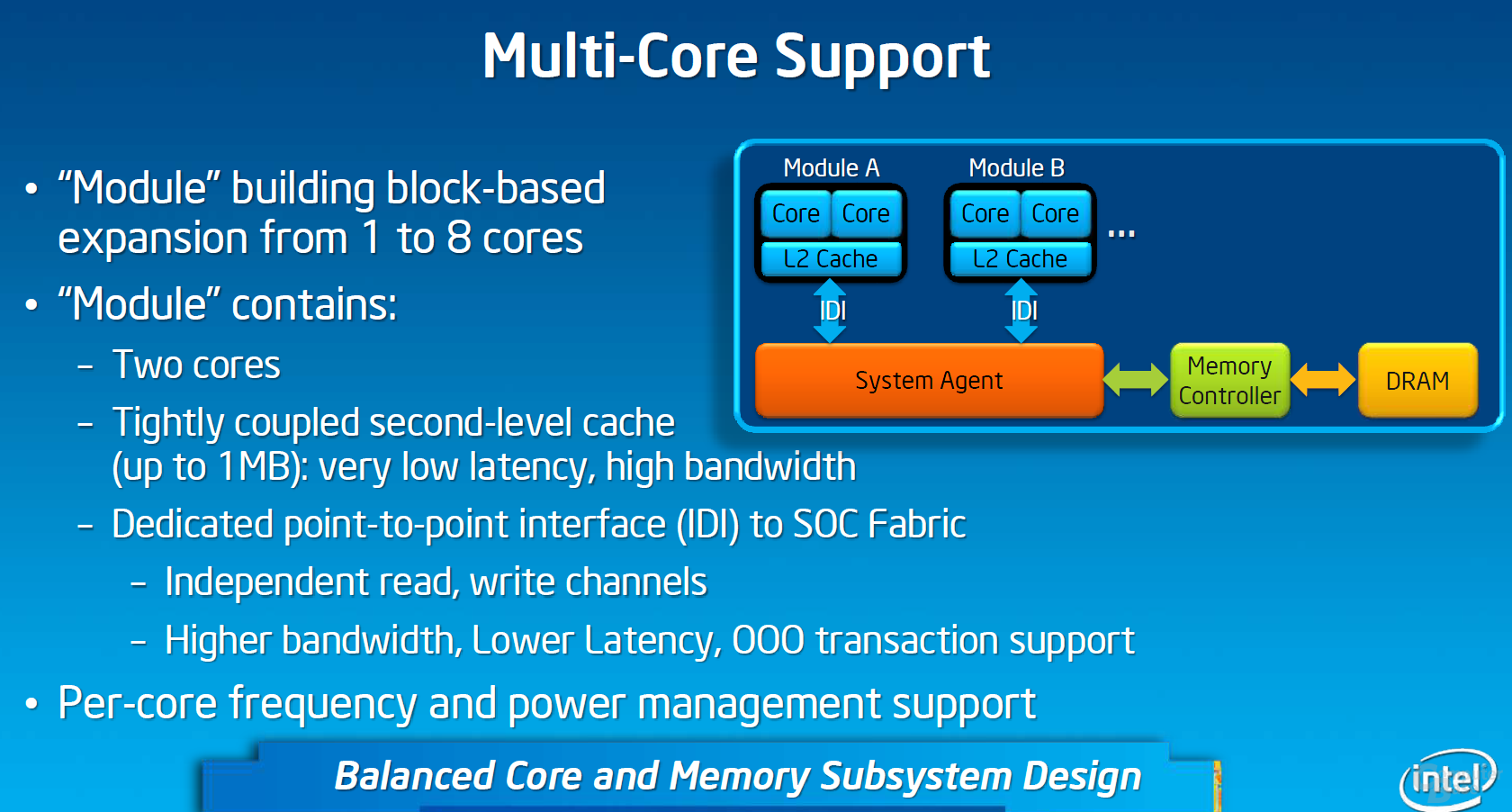

Abgerundet wird das Paket der neuen Kern-Architektur von einem L2-Cache, den sich zwei Kerne teilen; alle drei bilden ein „Modul“. Dieser L2-Cache ist 1 MByte groß und soll laut Intel zu den schnellsten SRAM-Chips gehören, die der Hersteller bisher in dieser Größe gefertigt hat. Beispielsweise wurden die Latenzen um 2 ns verringert, die Durchsatzrate je nach Anwendung mitunter drastisch gesteigert. Unterm Strich soll die IPC der neuen „Silvermont“ gegenüber „Saltwell“ um satte 50 Prozent zulegen, was man anhand einiger erster Leistungseinschätzungen darlegt.

Nicht inbegriffen ist in den Ausführungen von Intel der Speichercontroller. Hier wird der Hersteller je nach Bedarf ein bis vier Module zusammenschalten und über einen Point-to-Point-Interface mit dem System Agent an ein 64-Bit Dual-Channel-Speicherinterface koppeln. Beim Speicher selbst setzt Intel weiterhin auf DDR3-SDRAM.

Die weiteren Bausteine

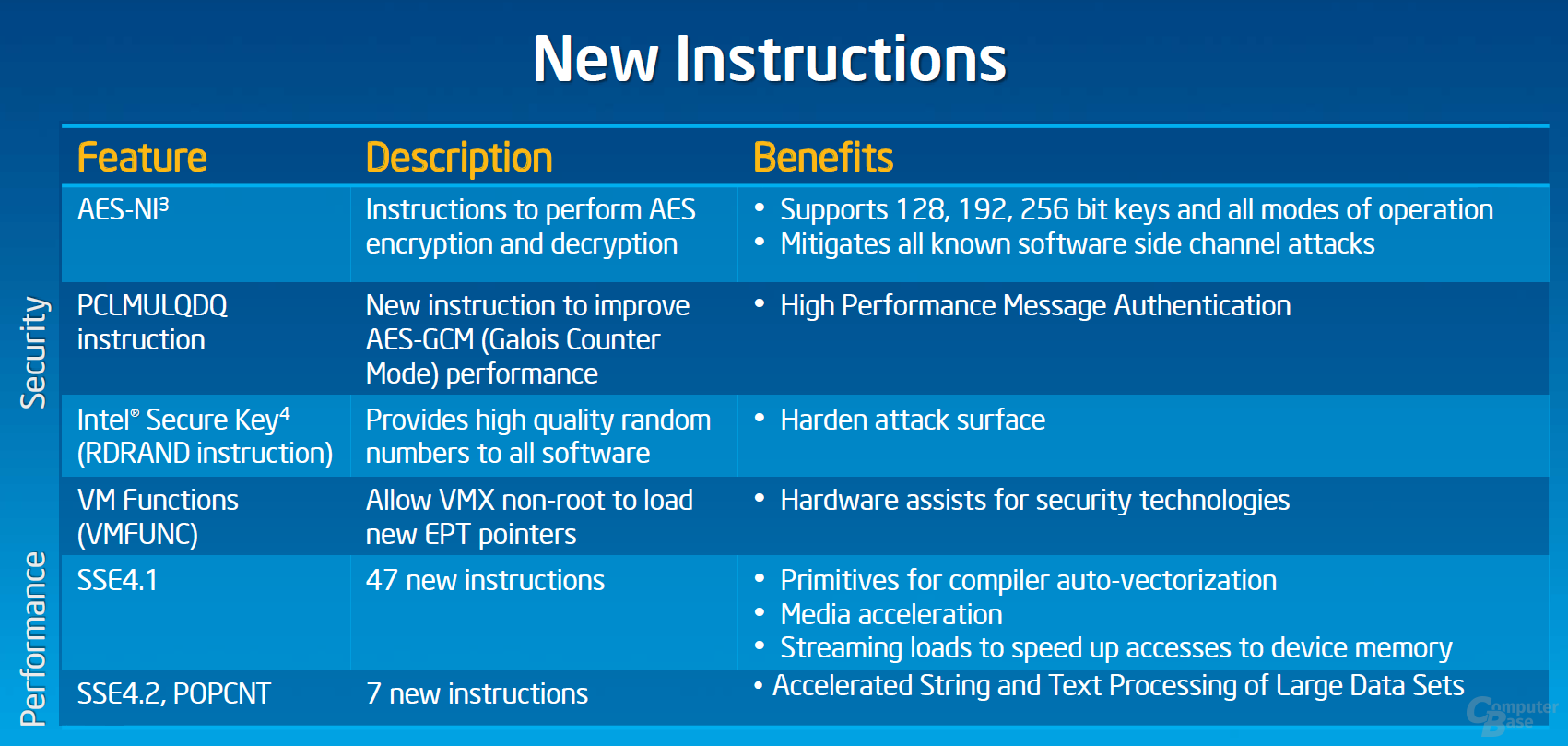

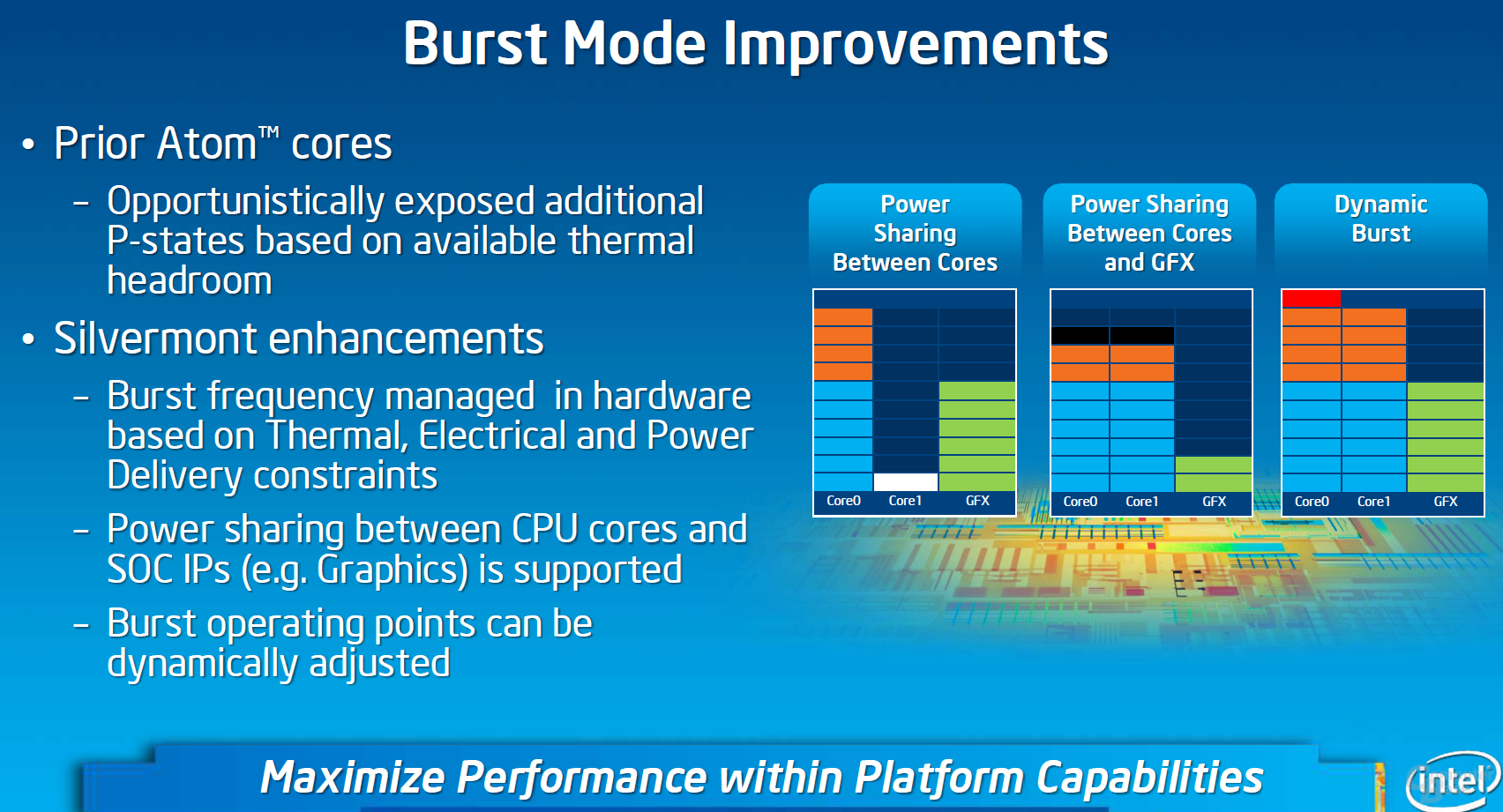

Bei den Zusatzinstruktionen sowie neuen Befehlen hebt Intel die neue „Silvermont“-Architektur auf das Niveau der „Westmere“, Intels ersten 32-nm-Prozessor. Dies heißt Unterstützung für VT-x2, SSE 4.1/4.2 und auch AES-NI sowie Real Time Instruction Tracing, nicht jedoch moderne Befehlssatzerweiterungen wie AVX. Ebenfalls auf der Habenseite verbucht die neue Architektur eine Turbo-Funktionalität, die recht nah an die der aktuellen Core-Prozessoren angesiedelt ist. Das thermische Budget ist zwischen Prozessor und der Grafikeinheit aufgeteilt, je nach Bedarf kann dynamisch aber auch der Turbo oberhalb der eigentlichen Vorgaben agieren.

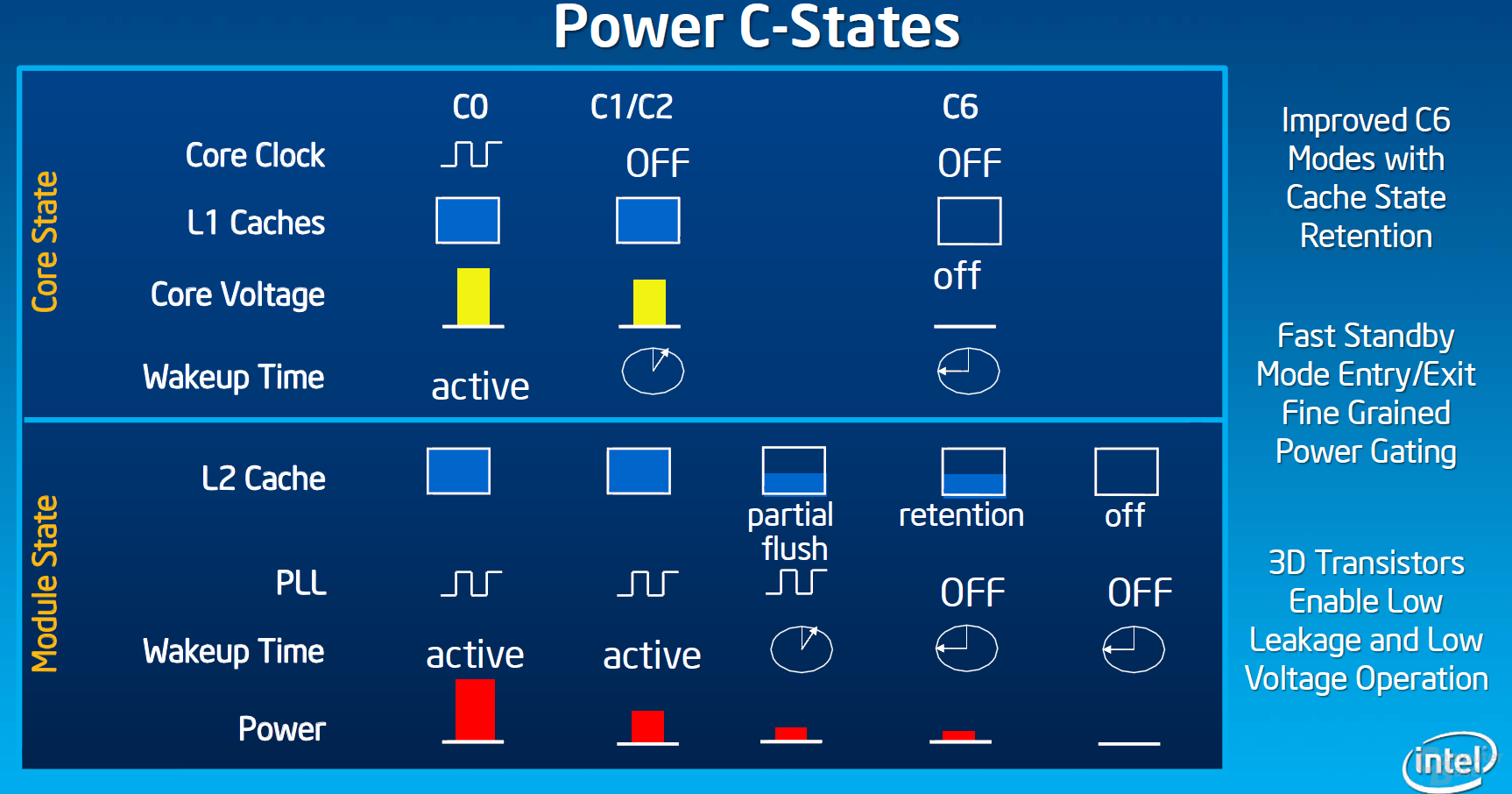

Ohne moderne Stromsparmechanismen kommt auch die neue Architektur nicht aus. Hierbei unterscheidet Intel zwischen zwei Leveln, einmal bei den Prozessorkernen selbst und zum zweiten im Modul, was vorwiegend auf den L2-Cache abzielt. So können einzelne Prozessorkerne mit ihrer eigenen Spannung arbeiten, separat takten und in den Schlaf versetzt werden, auf Modul-Ebene wird der L2-Cache je nach Bedarf aber weiterhin mit der maximal notwendigen Spannung versorgt, um den zweiten Kern mit Daten zu füttern. Erst wenn dieser wenig bis nichts mehr macht, wird das Modul schrittweise bis komplett heruntergefahren.

Fast fünf Jahre hat Intel an der neuen „Silvermont“-Architektur gearbeitet und das daraus resultierende SoC-Design so angepasst, dass es für die 22-nm-Fertigung prädestiniert ist. Keine Worte verlor Intel in der letzten Woche jedoch über die weiteren Elemente der SoCs wie die Grafikeinheit. Hier wurde in der Gerüchteküche vorab bereits von einer Lösung auf Basis der siebten Generation, die aktuell in den „Ivy Bridge“ zum Einsatz kommt, berichtet. Details zu dieser Thematik will Intel in den kommenden Wochen offenbaren.