AMD Analyst Day: Details zur neuen Architektur

AMD hat im Rahmen seines Analyst Day 2006 weitere Details zum 2007 erscheinenden Architektur-Update bekanntgegeben, das in der Gerüchteküche unter der Bezeichnung K8L seit geraumer Zeit diskutiert wird. Konkrete Informationen wurden erstmals im Rahmen des Spring Processor Forum im Mai 2006 von Chuck Moore präsentiert.

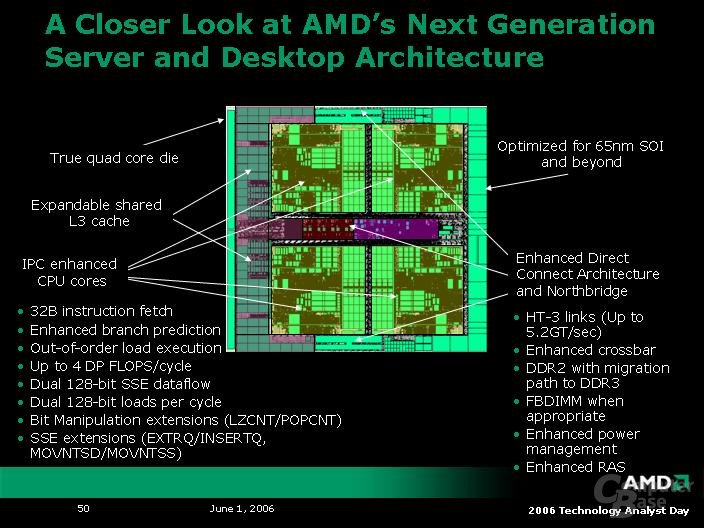

Die neuen Informationen bauen auf die Präsentation von Chuck Moore auf, gehen jedoch weiter ins Detail. Zu den grundlegenden Neuerungen des K8L-Designs, das wahrscheinlich in den Prozessoren mit den Codenamen Zamora (Server), Cadiz (Workstations) und Greyhound (Desktop) eingesetzt wird, gehören native Quad-Core-Unterstützung auf einem Silizium-Chip. Darüber hinaus wird die Plattform im Falle der Server-Prozessoren um einen mindestens 2 MB großen L3-Cache erweitert. Außerdem wurden Optimierungen an der Sprungvorhersage und den Ausführungseinheiten vorgenommen. Pro Takt sind nun bis zu vier Double Precision (128 Bit) Gleitkommaoperationen möglich.

Neue Befehle für die Bit-Manipulation (LZCNT/POPCNT) wurden hinzugefügt und auch der SSE-Befehlssatz wurde aufgestockt. Die HyperTransport-Anbindung wird auf Version 3 angehoben, das im Vergleich zum aktuellen 1 GHz schnellen HyperTransport 1 mit 16 Bit Datenbreite je Richtung die Bandbreite von 8 GB/s auf 20,8 GB/s bei 2,6 GHz steigern kann, sofern weiterhin 16 Bit breite Interfaces eingesetzt werden. Support für DDR3 und FB-DIMM ist ebenfalls vorgesehen, letzteres jedoch nur bei Bedarf. Verbesserungen beim im Unternehmen wichtigen RAS-Bereich (Reliability, Availability, Security) wird es ebenfalls geben.

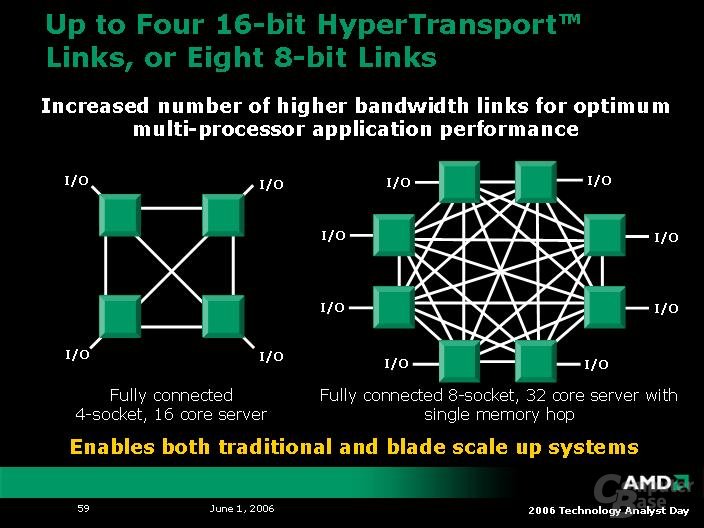

Für Server von besonderer Bedeutung dürften die angepassten (kohärenten) HyperTransport-Verbindungen im K8L-Design sein. Das aktuelle Design bietet bis zu drei 16 Bit breite kohärente HyperTransport-Links, die mit anderen Prozessoren verbunden werden können. Mit dem K8L steht darüber hinaus ein normaler 16 Bit breiter Link für den Anschluss von Peripherie zur Verfügung. Neben der um einen Link aufgestockten Anzahl an HyperTransport-Anbindungen steht auch eine neue Konfiguration zur Verfügung: Alternativ stehen nun insgesamt acht 8 Bit breite Interfaces zur Verfügung. Neben einem 8 Bit breiten I/O-Anschluss können 8-Sockel-Systeme mit Hilfe von 7 kohärenten Links realisiert werden. Auf Basis des Quad-Core-K8L sind damit Systeme mit 32 Prozessoren einfach möglich. Bisher war dies nur mit komplizierten Horus-Implementierungen machbar.

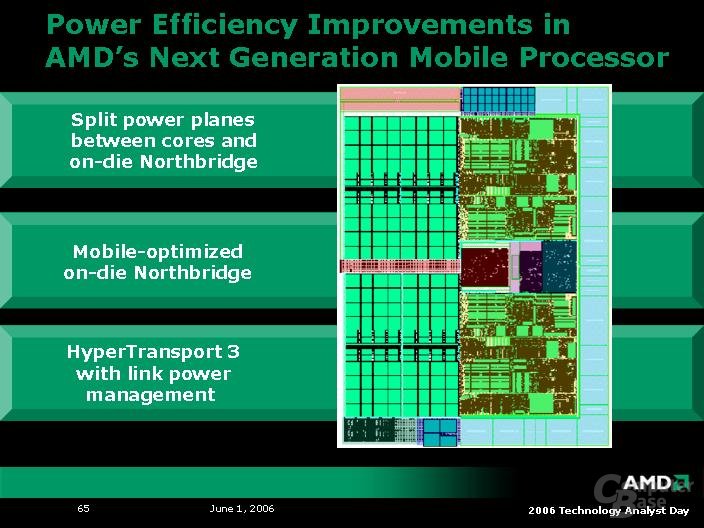

Mit dem neuen Core ist AMD in der Lage, den Takt der insgesamt vier Prozessorkerne unabhängig voneinander zu verändern, um so Energie zu sparen. Bisher teilen sich alle Prozessoren (auch bei Intel) einen Takt und Spannung.

Speziell für Notebooks wird es eine Variante des K8L-Designs geben, bei der auf den zusätzlichen L3-Cache verzichtet wird. Außerdem wird es sich hierbei nur um eine Dual-Core-Lösung handeln, die speziell auf den Einsatz im Notebook optimiert wurde. Beide Prozessorkerne werden dabei unabhängig voneinander mit Strom versorgt, so dass ein ggf. nicht genutzer Kern tatsächlich ruht.

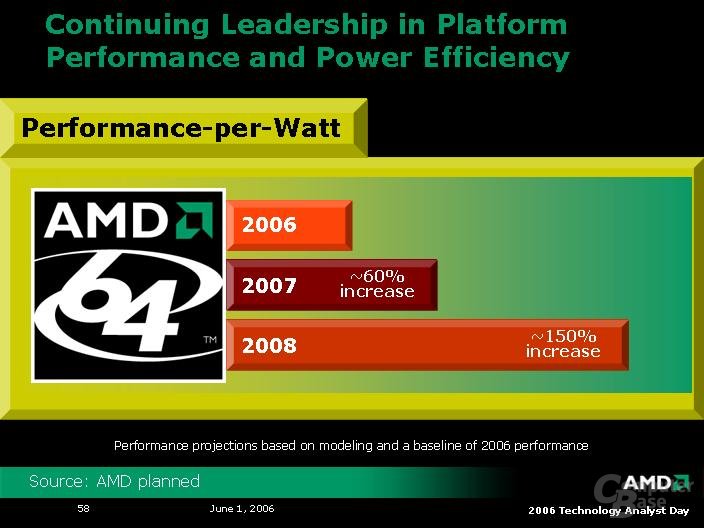

Das Ergebnis der Optimierung ist eine um 60 Prozent gestiegene Power-Effizienz, die im Jahr 2008 durch weitere Verbesserungen (z.B. 45 nm Herstellungsprozess) im Vergleich zur aktuellen Athlon 64-Implementierung (K8) um 150 Prozent (basierend auf Simulationsmodellen) gesteigert werden soll.

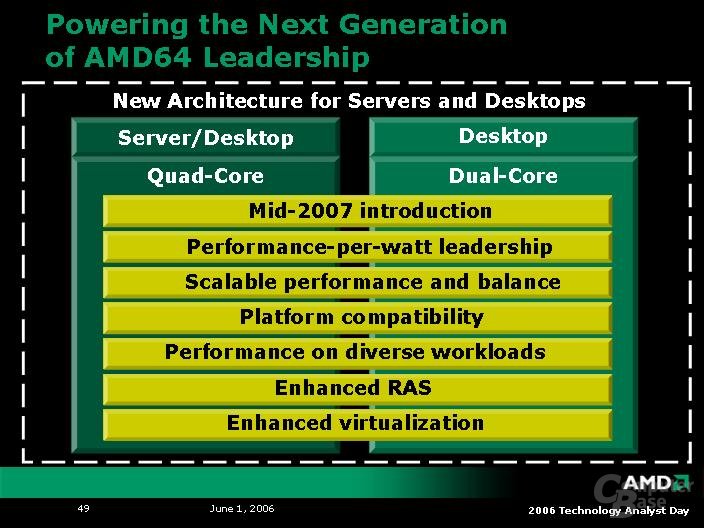

Die neue Architektur soll Mitte 2007 vorgestellt werden und wird unterm Strich folgende Verbesserungen bieten:

Weitere News zum AMDs Ankündigungen auf dem Analyst Day:

Neue Roadmap bis 2008