IDF: Intel zeigt den ersten 32-nm-Wafer

Intel CEO Paul Otellini präsentiert auf dem derzeit in San Francisco Intel Developer Forum den ersten 300 mm Wafer der mit in 32 nm (Nanometer) Testchips bestückt ist. Jeder einzelne dieser Chips bringt es auf insgesamt 1,9 Milliarden Transistoren.

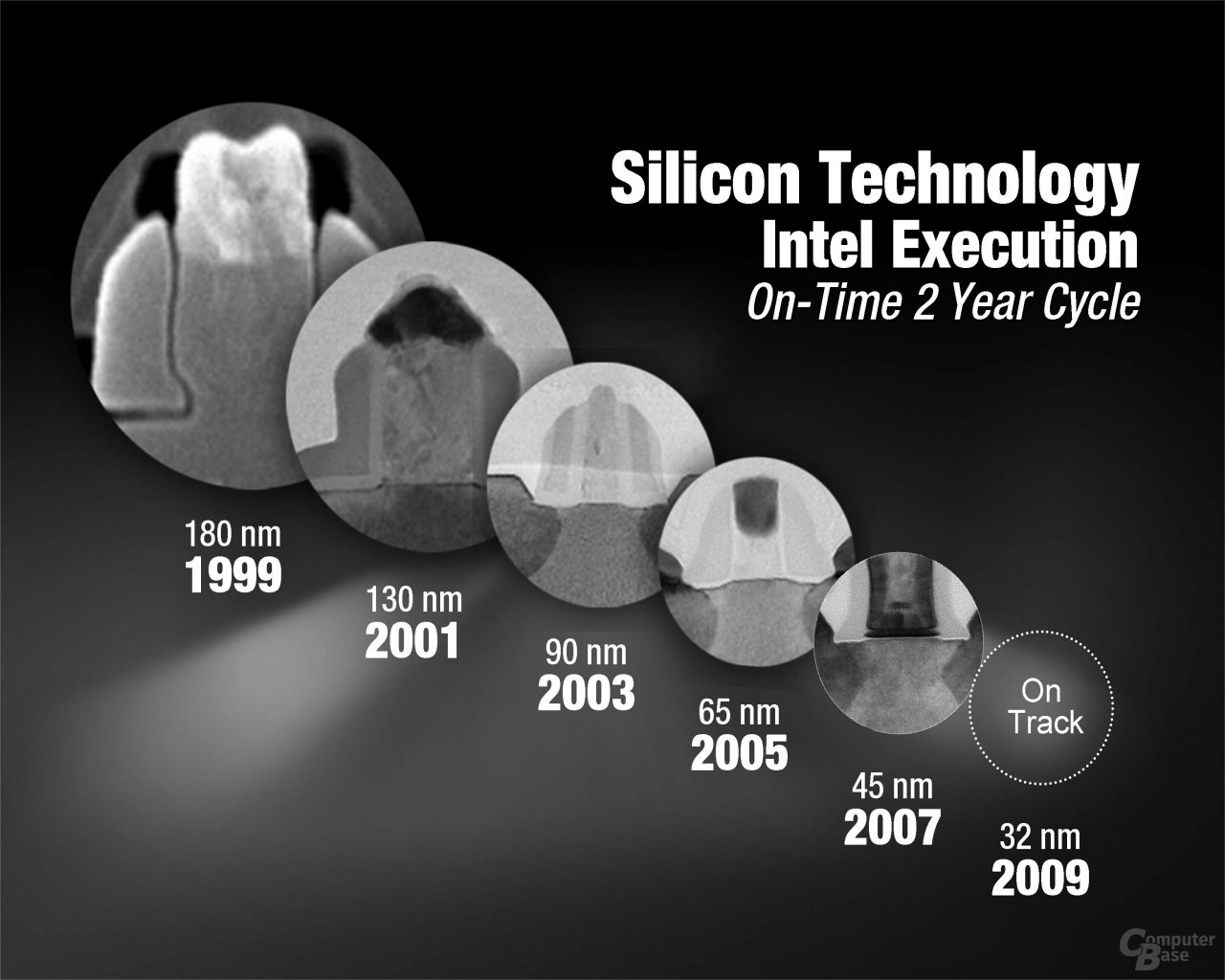

Intel will seine Prozessoren mit dem Codenamen „Westmere“ (ehemals Nehalem-C) ab 2009 in diesem neuen Verfahren herstellen und verwendet dazu die zweite Generation der High-K- und Metal-Gate-Transistor-Technologie, deren erste Generation beim 45 nm Herstellungsprozess P1266 bei den für November 2007 erwarteten Penryn-Prozessoren zum Einsatz kommt. Die 32-nm-Fertigungstechnologie geht dabei erstmals bei Intel auf die nasse Lithographie zurück. Bei der sogenannten Immersion Lithografie setzt Intel zwar weiterhin auf 193 nm Lichtquellen, jedoch wird zwischen Wafer und Linse nun Wasser statt bisher hochreine Luft eingesetzt, um das Verhalten der Lichtbrechung zum Positiven zu verändern. AMD wird die Immersion Lithografie, wie der Großteil der Industrie (IBM, UMC, Toshiba, und TI), bereits beim 45-nm-Herstellungsprozess einsetzen.

Intels Test-Chip mit dem Synonym „X8“, der in P1268 gefertigt wurde – so die genaue Bezeichnung Herstellungsverfahrens mit 32 nm Strukturbreite – enthält verschiedenste Testschaltungen, darunter auch 291 Megabit großer SRAM-Speicher, Register Files, I/O-Schaltkreise, PLLs und vereinen insgesamt mehr als 1,9 Milliarden Transistoren auf einem Stück Silizium, die unter anderem auch dazu genutzt werden, um z.B. die Spice-Parameter zu bestimmen. Zum Vergleich: Intels erster 45-nm-Test-Chip hatte seinerzeit „nur“ 1 Mrd. Transistoren.

Details der 32-nm-Transistoren, die Anzahl der Interconnect-Layers oder die Größe einer 6T-SRAM-Zelle hat Intel im Rahmen der heutigen Vorstellung im Rahmen des IDF noch nicht Preis gegeben. Hier darf im Laufe der Zeit mit weiteren Informationen gerechnet werden.

Intel hat bekannt gegeben, dass eine in 32 nm gefertigte SRAM-Zelle eine Größe von 0,182 µm² habe. Die in 45 nm (P1266) gefertigte Zelle hat eine Größe von 0,346 µm². In 65 nm-Technologie (P1264) waren es noch 0,570 µm². Während der Schrumpfungsfaktor von 65 auf 45 nm noch bei 0,6 gelegen hat, fällt dieser beim Schrumpfen auf 32 nm mit 0,52 nun nahezu ideal aus (ideal wären 0,5).

In die Newsmeldung wurde Bildmaterial hinzugefügt