TSMC: Erster Netzwerk-SoC in 16-nm-FinFET-Prozess gefertigt

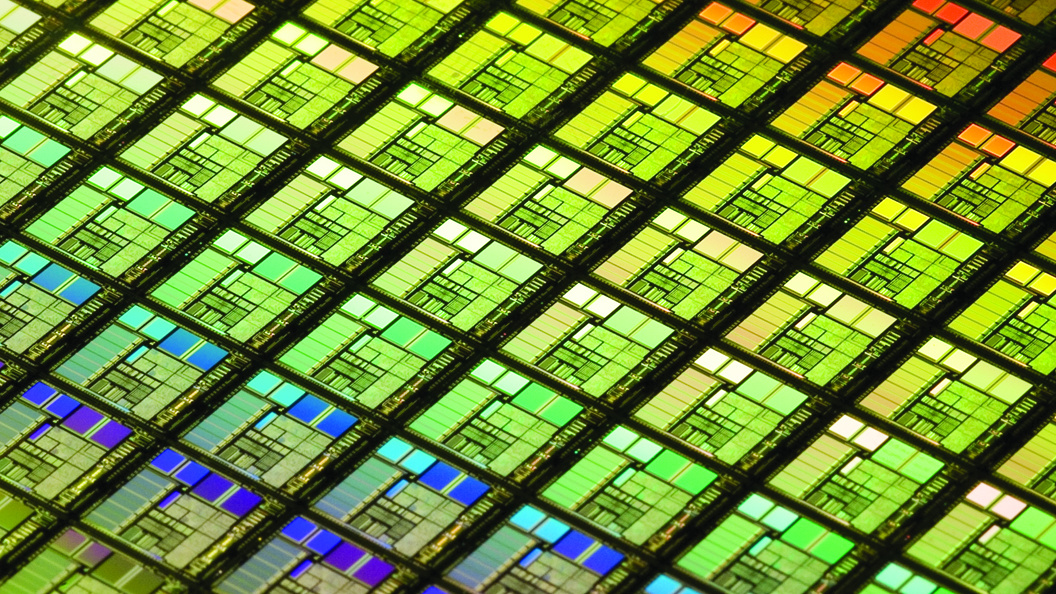

TSMC hat gemeinsam mit HiSilicon, der Halbleitersparte von Huawei, einen ersten voll funktionsfähigen Netzwerkprozessor im neuen 16FinFET-Prozess (16 nm Strukturbreite, FinFET-MOSFETs) hergestellt, der Anfang des Jahres das Stadium der sogenannten risk production erreicht hat und bereits eine sehr gute Ausbeute bieten soll.

Der für Basisstationen, Router und andere Netzwerkausrüstung vorgesehene ARM-SoC verfügt über 32 Cortex-A57-Kerne mit bis zu 2,6 GHz und soll laut den beteiligten Herstellern rund dreimal so leistungsfähig wie die vorherige Produktgeneration sein. Im neuen 16-nm-Verfahren wird allerdings nur der Logikchip des SoCs gefertigt. Der I/O-Chip wird noch im 28-nm-Verfahren hergestellt und mit Hilfe von TSMCs CoWoS-Packagingprozess (Chip-on-Wafer-on-Substrate) mit dem Logikchip zu einem SoC vereint.

Verglichen mit dem aktuellen 28HPM-Prozess von TSMC bietet der 16FinFET-Prozess die doppelte Gate-Dichte und ist wahlweise bei gleicher Leistungsaufnahme mehr als 40 Prozent schneller oder erlaubt bei gleicher Geschwindigkeit eine um mehr als 60 Prozent verringerte Leistungsaufnahme.

Vorreiter bei der industriellen Fertigung sogenannter „3D-Transistoren“ ist jedoch Intel. Das Unternehmen wechselte bereits vor über drei Jahren bei der Einführung des 22-nm-Prozesses von planaren Transistor-Designs zu Tri-Gate-Transistoren und setzt diese seitdem erfolgreich ein.