STT-MRAM: Toshiba arbeitet an überlegener Alternative zu SRAM

Toshibas Forschungsabteilung arbeitet am Einsatz von STT-MRAM als Cache-Speicher für Prozessoren und SoCs. Es soll das derzeit übliche SRAM ersetzen, das zwar extrem schnell ist, aufgrund des Platzbedarfs und der relativ hohen Leistungsaufnahme aber insbesondere im Mobil-Bereich als Schwachpunkt gilt.

Die hohe Leistungsaufnahme hängt unter anderem damit zusammen, dass SRAM viel Platz benötigt und mit Leckströmen zu kämpfen hat. Zudem ist SRAM ein flüchtiger Speicher, der eine ständige Stromversorgung benötigt, damit die Daten im Cache erhalten bleiben. Bei zunehmenden Cache-Größen steigt folglich auch der Energiebedarf.

STT-MRAM (Spin-Transfer Torque Magnetic Random Access Memory) ist im Gegensatz dazu ein nichtflüchtiger Speicher, der Daten auch im ausgeschalteten Zustand über lange Zeit speichert. In Kombination mit der relativ hohen Leistung wird STT-MRAM daher schon länger auch als eine mögliche Nachfolgetechnologie für sowohl DRAM als auch NAND-Flash genannt.

Zum Schreiben und Speichern der Daten werden bei STT-MRAM magnetische Eigenschaften genutzt, genauer gesagt der Magnetische Tunnelwiderstand (TMR), der in magnetischen Tunnelkontakten (MTJ) auftritt. Will man Daten schreiben, wird die magnetische Orientierung einer dünnen magnetischen Schicht im MTJ-Element mit Hilfe eines spinpolarisierten Stroms verändert. Zum Lesen der Daten wird der Widerstand des Elements gemessen, der von der Magnetisierung des MTJ abhängig ist.

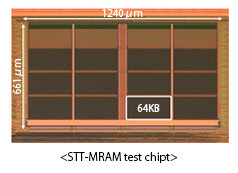

Die Schaltkreise des Testchips von Toshiba erlauben Zugriffszeiten von 3,3 Nanosekunden. Das reicht zwar nicht an die Performance von herkömmlichem SRAM heran, dafür benötigt das STT-MRAM aber rund 80 Prozent weniger Energie.

Um dies zu erreichen, mussten neben anderen Optimierungen beim Lesen und Schreiben auch die peripheren Kontrollschaltkreise des Speichers überarbeitet werden, die normalerweise ständig mit Strom versorgt werden. Ziel war es, sie möglichst schnell an- und wieder ausschalten zu können, um nicht zu viel Leistung zu verlieren. Insbesondere die zum Wiederherstellen der Stromversorgung benötigte Zeit ist kritisch, da sie sich auf die Zugriffslatenzen auswirkt. Hierzu wurde der Speicherbereich in sieben Regionen mit eigenem Lastschalter unterteilt, die unabhängig voneinander deaktiviert werden können.

Die kürzeste gemessene Zeitspanne für die Wiederherstellung der Stromversorgung nach dem Abschalten wird mit 22 ns angegeben, was kürzer ist als die durchschnittliche Wartezeit für den Cache-Zugriff, die Toshiba mit 30 ns angibt.

Als Ziel des bis zum Ende des Fiskaljahres 2015 laufenden Projektes gibt Toshiba die weitere Verbesserung der Technologie an, um die Gesamtleistungsaufnahme von Prozessoren im Vergleich zu herkömmlichen Schaltkreisen auf weniger als ein Zehntel reduzieren.