TSMC-Ausbaupläne: Packaging-Nachfrage massiv, neue Fab eröffnet

Nicht nur Nvidia rennt bei TSMC die Türen ein, auch andere wollen fortschrittlich verpackte Chips. Doch das Angebot des sogenannten Advanced Packaging ist viel zu klein, TSMC allein kann es nicht befriedigen, sodass Mitbewerber wie ASE in die Bresche springen sollen. Die freuen sich über hochbezahlte Aufträge.

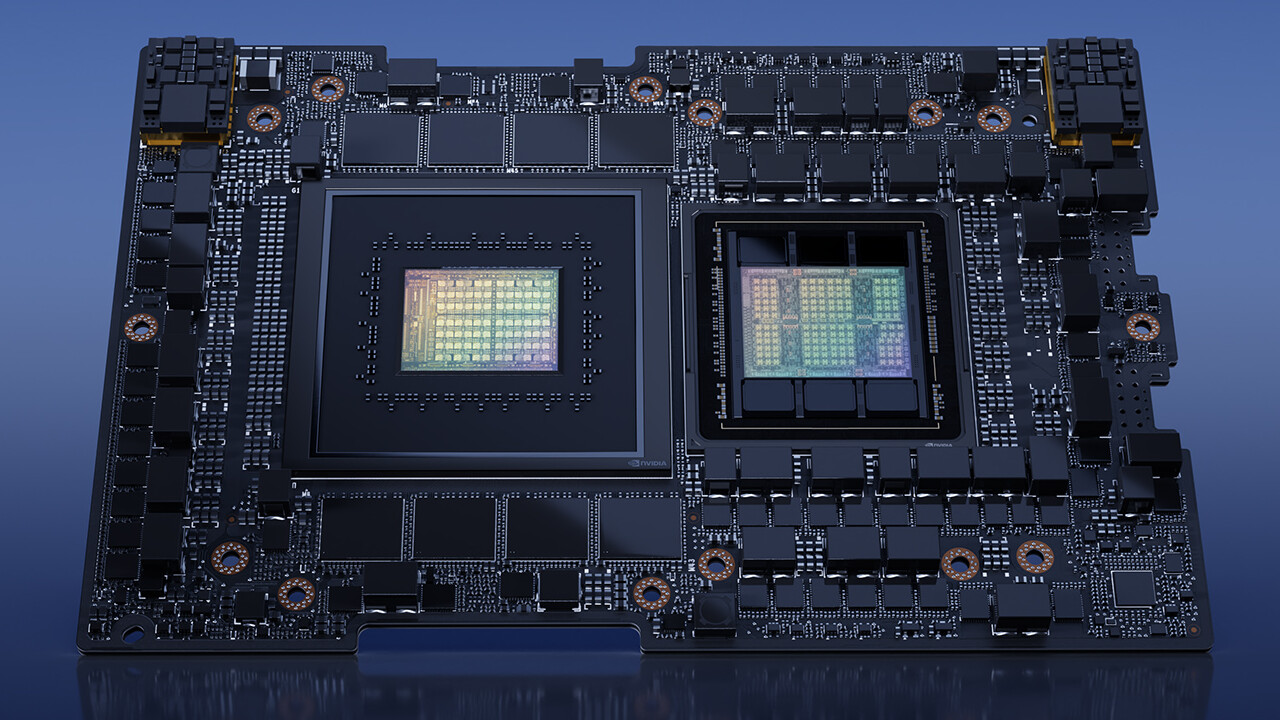

Nvidias Ankündigung zur Umsatzexplosion in den nächsten Monaten stellt die Lieferkette vor einige Probleme. Denn so viel, wie Nvidia nun gern abnehmen möchte, kann derzeit kein Unternehmen allein stemmen. Nvidia könnte deshalb weniger absetzen als eigentlich möglich wäre. Dabei hapert es nicht direkt an der Produktion der Chips, sondern dem Zusammenfügen. Denn gerade Nvidias nun gefragtesten Profi-Lösungen, seien es die älteren A100 oder die neuen H100, benötigen viel Aufwand beim Verpacken. Ironischerweise hat Nvidia selbst erst zur Computex 2023 ein Video gezeigt, das aber nicht alle Schritte darstellt, vor allem die ersten bezüglich des Chips überspringt.

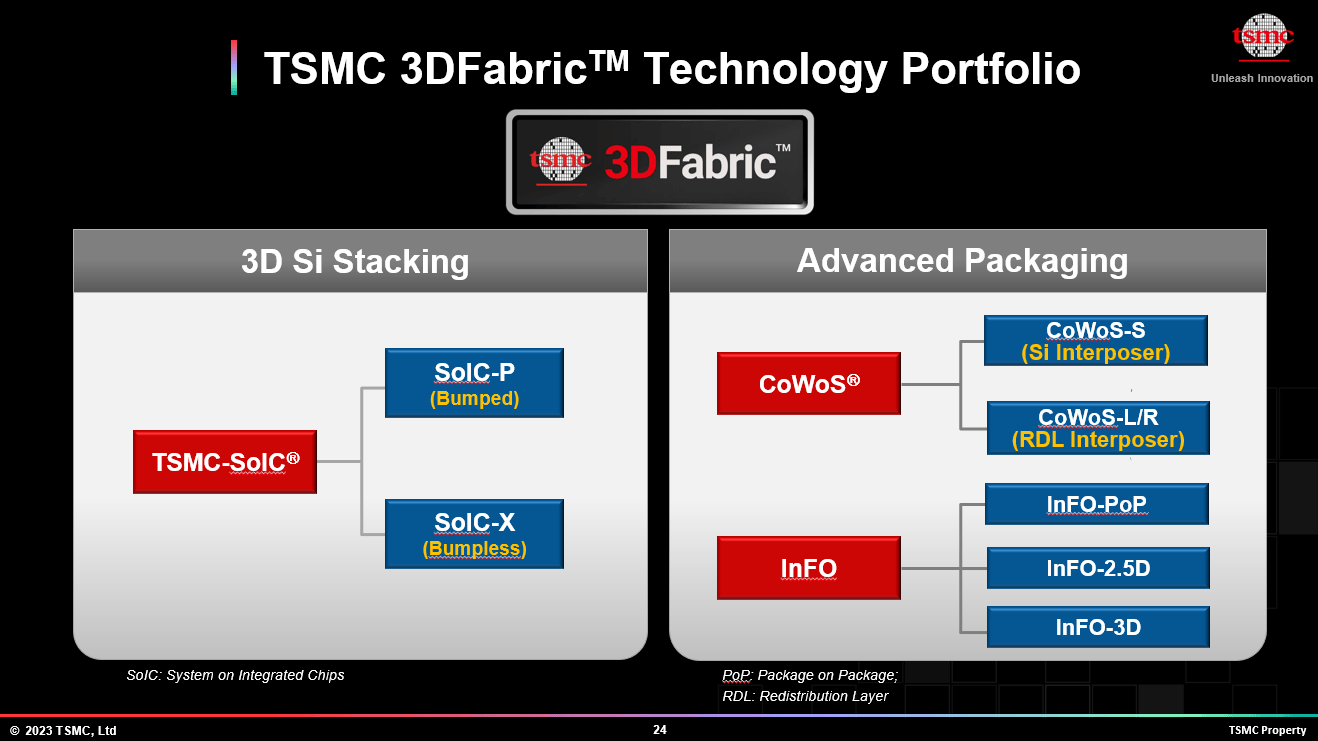

Die Großkundschaft bei TSMC braucht auch das Packaging. Und das ist nicht nur die PC-Kundschaft, allen voran nämlich der größte Kunde: Apple. Seit der Einführung der M-SoC-Familie setzte Apple noch stärker auf TSMCs Packaging-Fertigkeiten, was zu einem regelrechten Bau-Boom dieser Anlagen bei TSMC geführt hat. Vor allem InFO kommt hier zum Einsatz, belegt aber wegen gewisser Gemeinsamkeiten auch Kapazitäten für CoWoS in unterschiedlichen Ausführungen – gerade darum buhlen Kunden für PCs und Server.

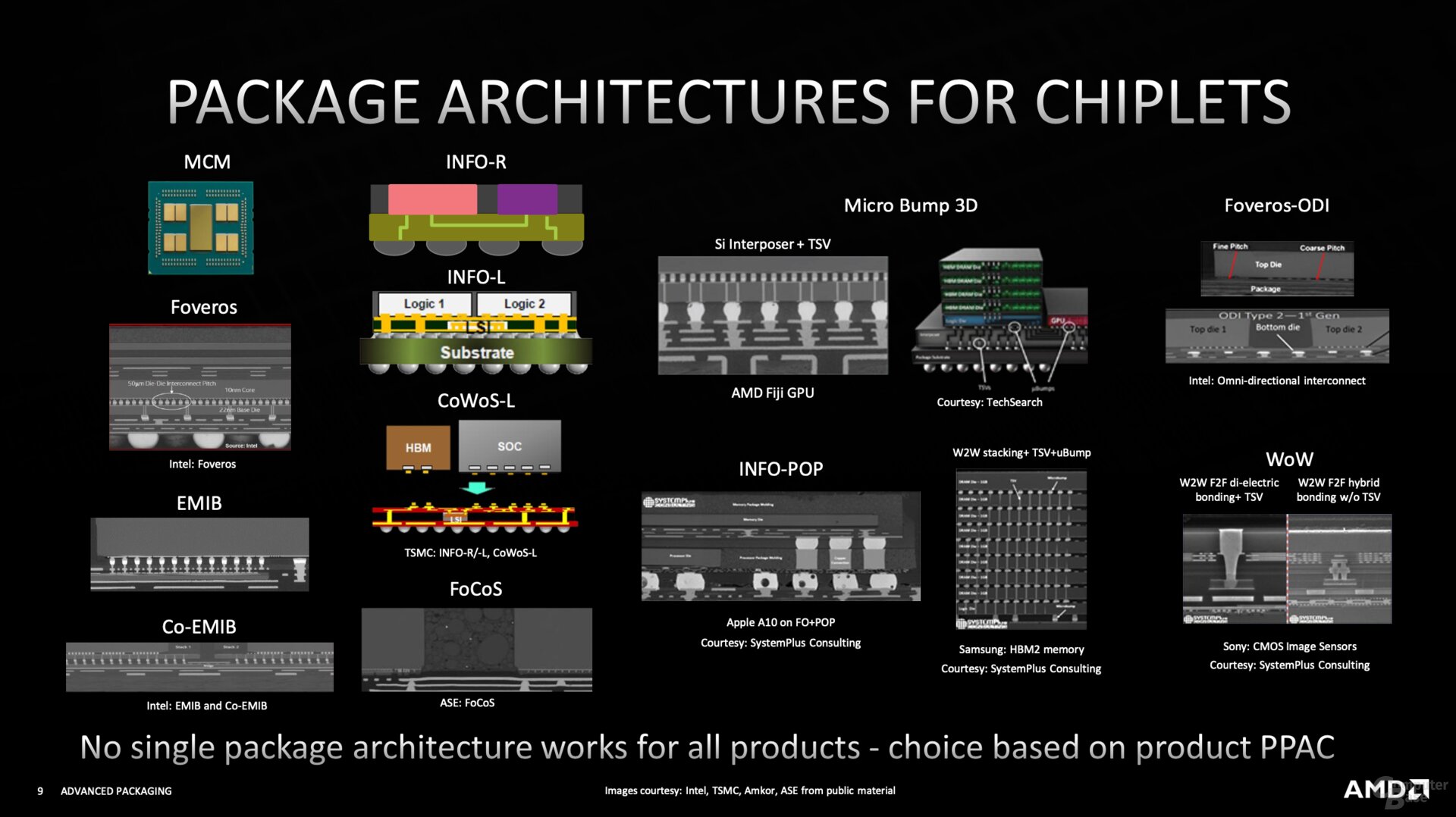

Und genau hier kann und soll nun ASE helfen, denn die Schnittmenge ist in diesen Bereichen ziemlich groß. ASE gehört zur Weltspitze mit eigenen 2,5D- und 3D-Packaging-Lösungen und bietet diese bereits lange für weltweite Kunden an, AMD gehört beispielsweise seit Jahrzehnten dazu, Fiji als Auftaktlösung für ein 2,5D-Produkt ist weltbekannt geworden. An den Nachfolgern und Weiterentwicklungen dieser Möglichkeiten arbeitet ASE wie andere Unternehmen seit Jahren, viele Ähnlichkeiten ermöglichen nun eine teilweise Zusammenarbeit, um die riesige Nachfrage zumindest teilweise bedienen zu können.

Das wird viel Geld kosten, aber gerade bei den High-End-Chips und der extremen Nachfrage spielt Geld aktuell fast keine Rolle. Zur Computex 2023 schwirrten nach der Keynote von Nvidia Zahlen über den Flur, die von einem Stückpreis für eine H100 weit jenseits der 20.000-US-Dollar Marke sprachen, andere nennen gar bis zu 40.000 US-Dollar, die sich dabei auf Listungen in Auktionsplattformen beziehen oder auf fertige Systeme wie von Lambda Labs mit acht H100 für über 350.000 US-Dollar. Da sind die rund 10.000 US-Dollar für den Vorgänger A100 fast ein Schnäppchen.

Verdienen werden aber auch alle Zwischenschritte bis hinauf zu Nvidia, deren Umsatzprognose mit einem Plus von 50 Prozent mit jedem Tag fast zu niedrig erscheint. Doch dafür müssen sie an die Chips kommen, und hier scheint je nach Quelle bis Jahresende ein Problem zu bestehen. Wer jetzt nicht bereits bestellt hat, bekommt dieses Jahr quasi nichts mehr – außer über Umwege und dann vermutlich noch teurer. Entspannung kommt frühestens im Jahr 2024 heißt es, da dann neue Kapazitäten zur Verfügung stehen sollen.

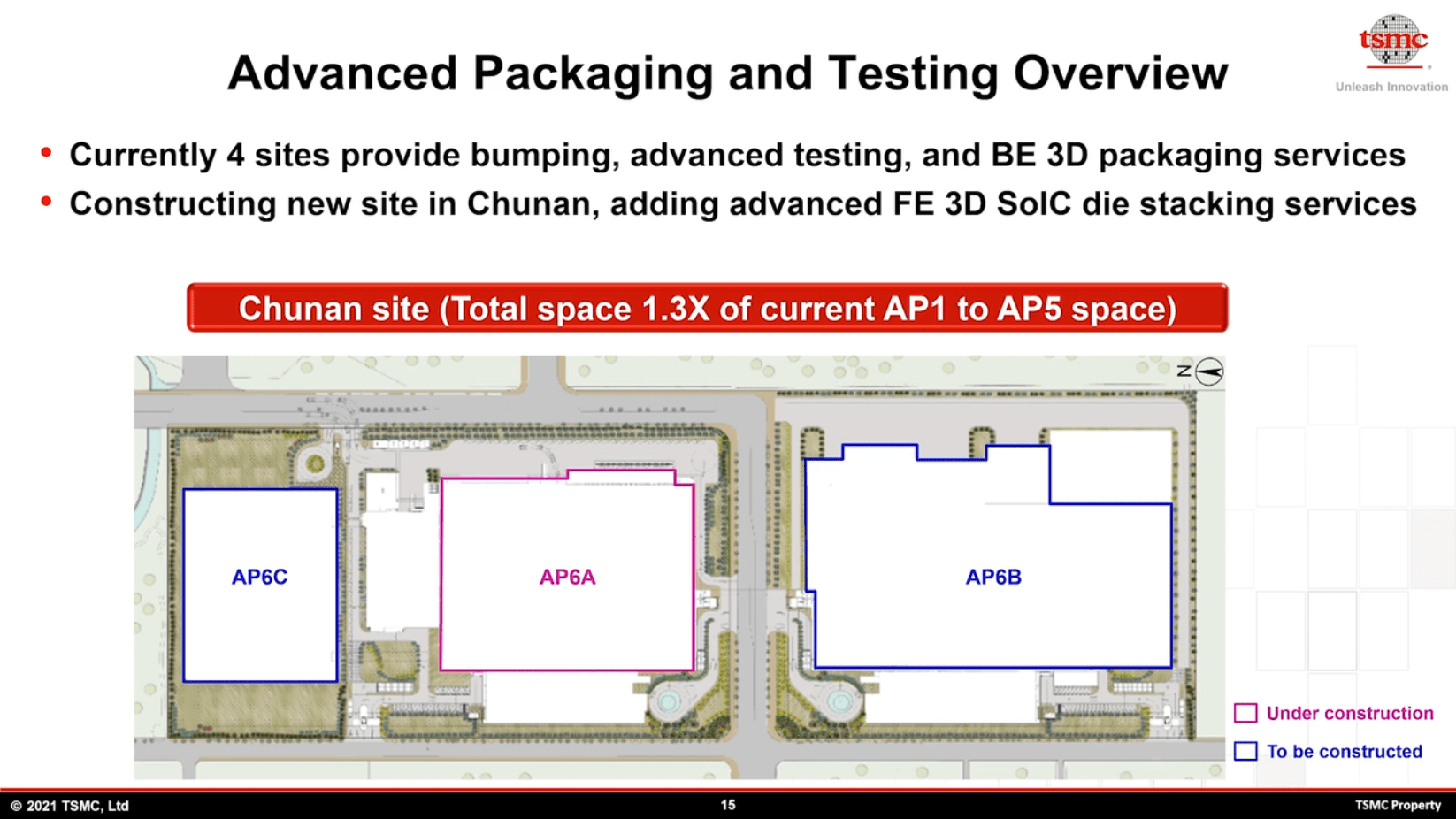

Passender könnte der Termin kaum sein: Heute hat TSMC die Eröffnung der neuen Advanced Packaging Fab 6 bekannt gegeben. Seit dem Jahr 2020 im Bau wird sie die Möglichkeiten massiv ausbauen, damals hieß es, wenn sie fertiggestellt werde, würde sie die bestehenden Kapazität aller anderen Packaging Fabs kombiniert mehr als verdoppeln. Heute erklärt TSMC, dass pro Jahr hier 1 Million 300-mm-Wafer verarbeitet werden können und so die Nachfrage nach modernem Testen und dem Stacking wie SoIC, InFO und CoWoS bedienen sollen.