Sony PlayStation 3 im Test: Nur heiße Mitochondrien um neuen Cell-Kern?

6/25Cell-Prozessor

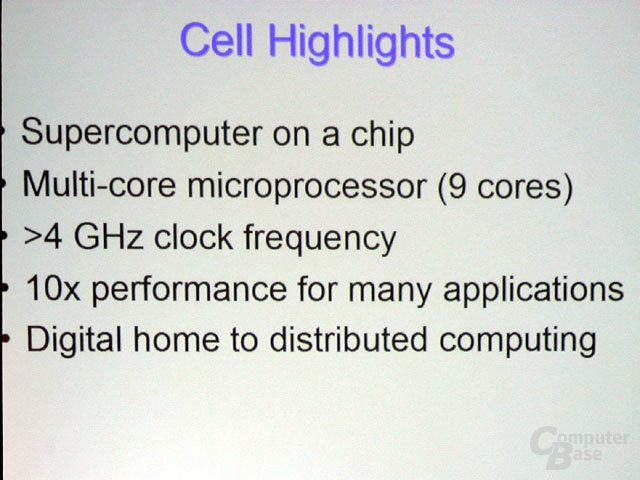

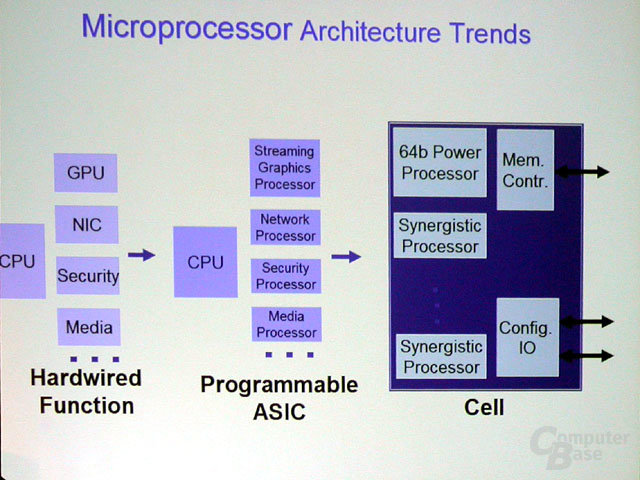

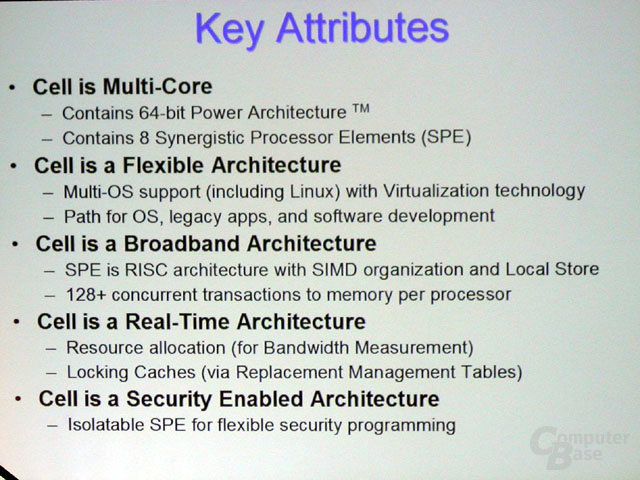

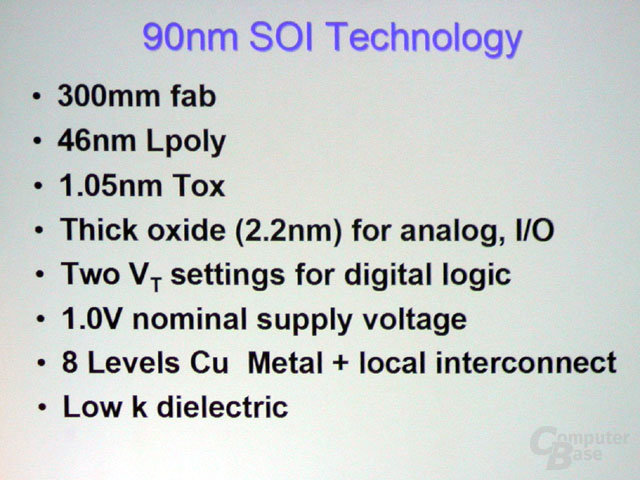

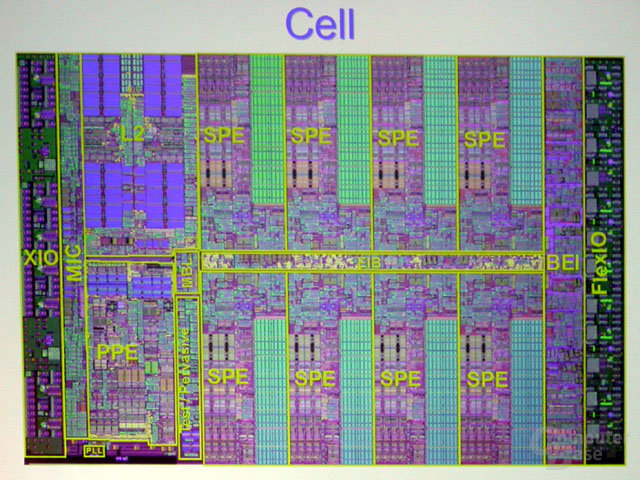

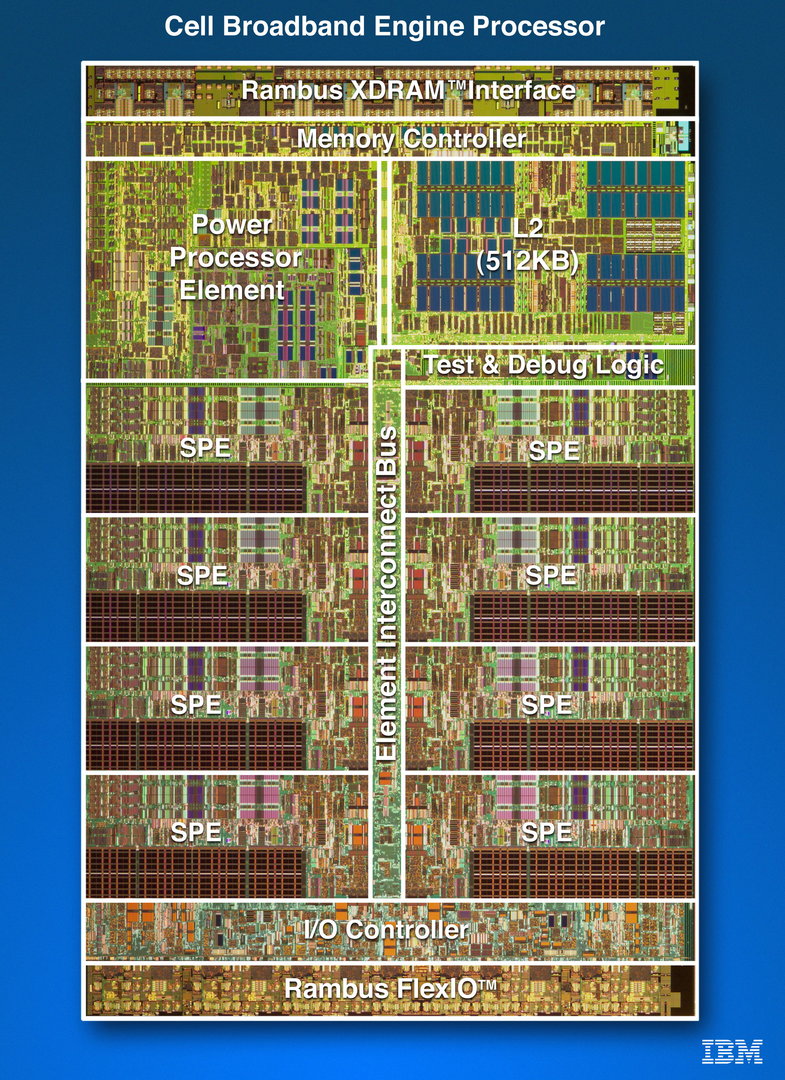

Als Hauptprozessor der PlayStation 3 dient der Cell-Prozessor, welchen Sony zusammen mit Toshiba und IBM entwickelt hat. Der Cell wird in 90 nm feinen Strukturen gefertigt, wobei IBM bereits die Umstellung auf den 65-nm-Prozess angekündigt hat, so dass auch der Cell-Prozessor der PlayStation 3 früher oder später auf diese Strukturbreite umgestellt werden wird, wodurch Sony Kosten senken kann. Beim Cell handelt es sich um einen 64-Bit-PowerPC, dem auch Simultaneous Multithreading (SMT) und eine Pipeline-Architektur nicht fremd sind.

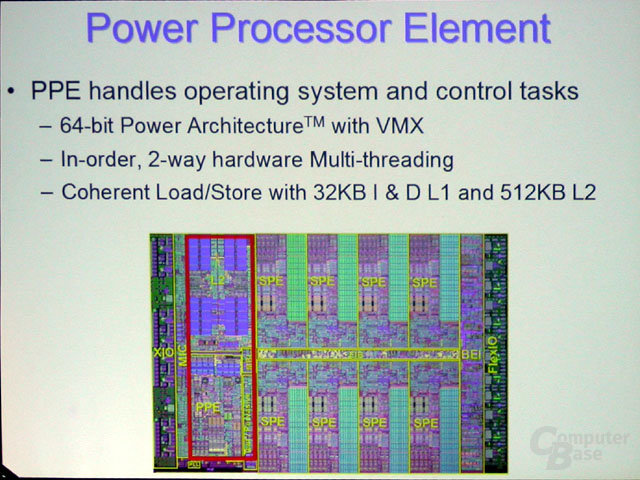

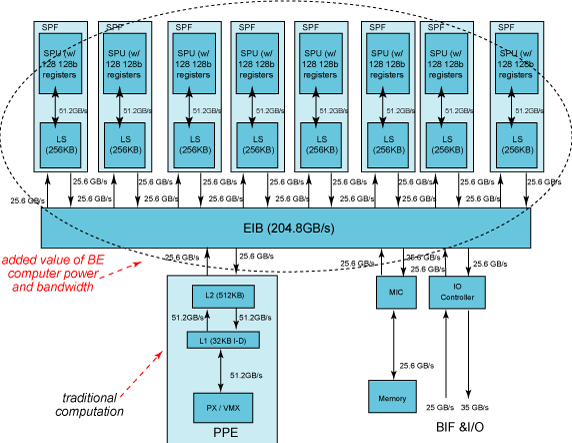

Ebenso wie der Prozessor der Xbox 360 taktet er mit 3,2 GHz, setzt allerdings anders als die Xbox 360 nicht auf drei vollwertige 64-Bit-PowerPC-Kerne, sondern verfügt über eine asymmetrische Multi-Core-Architektur. Einer PowerPC-Steuereinheit, dem PowerPC Processing Element (PPE), stehen beim Cell-Prozessor sieben Synergistic Processing Elements (SPE) zur Seite. Eigentlich verfügt der Cell über acht SPEs, welche bei der PlayStation 3 jedoch auf sieben reduziert wurden, um die Ausbeute bei der Fertigung erhöhen zu können. Unter Linux und für Spiele stehen der PlayStation 3 gar nur sechs SPEs zur Verfügung, da eine SPE in einem speziellen Modus unter Kontrolle des Hypervisors läuft. Das PPE bietet Simultaneous Multithreading (SMT) und kann so zwei Aufgaben parallel abarbeiten. Statt auf Instruction-Level-Parallelism (ILP) zu setzen und damit die Komplexität und Kosten der Chips in die Höhe zu treiben, setzt IBM mit dem Cell massiv auf Thread-Level-Parallelism (TLP).

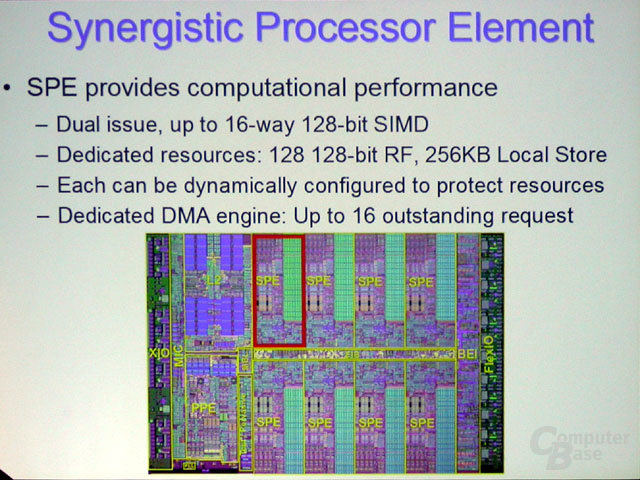

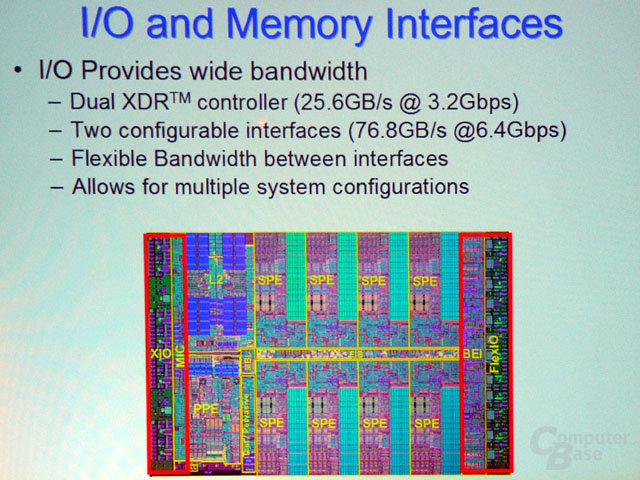

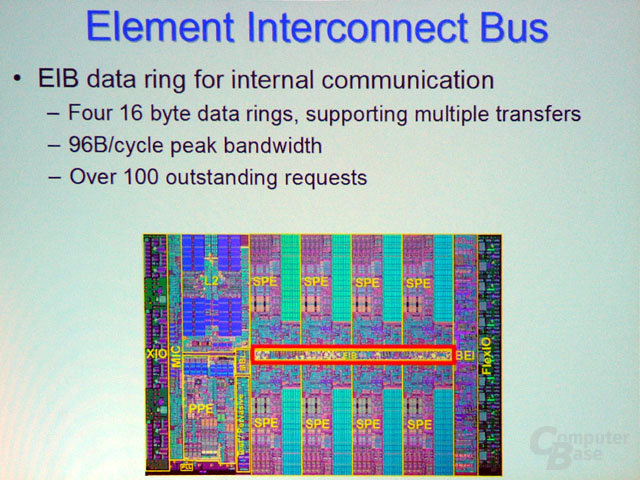

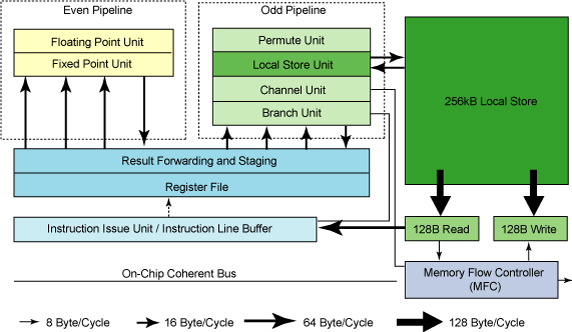

Jedes der sieben bei der PlayStation 3 zum Einsatz kommenden Synergistic Processing Elements (SPEs) besteht aus einer ALU mit vierfach SIMD (Single Instruction, Multiple Data). Diesen Kern bezeichnet man im Gegensatz zum Element (SPE) als Synergistic Processing Unit (SPU). Der Registersatz einer jeden SPU besteht aus 128 SIMD-Registern, die jeweils 128 Bit breit sind. Hier hat auch Intels SSE mit lediglich acht Registern unter 32 Bit und 16 Registern unter 64 Bit das Nachsehen, während der Prozessor der Xbox 360 mit ebenfalls 128 Registern kann mithalten. Eine SPE kennt fünf native Datentypen (16 x 8-Bit-Integer, 8 x 16-Bit-Integer, 4 x 32-Bit-Integer, 4 x 32-Bit-Gleitkomma und 2 x 64-Bit-Gleitkomma). Ein zu jeder SPE gehörender „Memory Flow Controller“ (MFC) steuert über den 96 Byte pro Takt breiten „Element Interconnect Bus“ (EIB) die DMA-Übertragungen zu anderen SPEs, dem PPE, dem „Memory Interface Controller“ (MIC), welcher über zwei 32 Bit breite Kanäle mit dem XDR-RAM verbunden ist, und den beiden „Bus Interface Controllern“, welche die Verbindung zum Bus-Interface „FlexIO“ von Rambus herstellen, worüber beispielsweise mit dem RSX-Grafikchip von nVidia kommuniziert wird. Der Cell erreicht dabei Dank zwölf 8-bittige Lanes, welche aus acht Signalpaaren bestehen, über das FlexIO-Interface eine maximale I/O-Bandbreite von 76,8 GByte pro Sekunde. Die Bandbreiten zum RSX-Grafikchip betragen 20 GByte/s beim Schreiben und 15 GByte/s beim Lesen, womit man das bei Grafikkarten aktuell eingesetzte PCIe x16, welches je Lane 250 MB/s in jede Richtung oder zusammengenommen 500 MB/s an Daten übertragen kann – 4 GB/s können somit hin- und zurückgeschubst werde – deutlich übertrifft.

Sowohl das FlexIO-Interface als auch der XDR-Hauptspeicher von Rambus verfügen über eine so genannte „FlexPhase“-Technologie, welche es Signalen erlaubt, zu unterschiedlichen Zeiten einzutreffen, so dass Signalleitungen nicht mehr exakt gleich lang sein müssen, was das Leben der Board-Entwickler vereinfacht. Beim „Element Interconnect Bus“ (EIB) haben sich IBM, Sony und Toshiba für einen Ringbus (4x128 Bit) entschieden, der mit halbem CPU-Takt arbeitet. Des Weiteren verfügt jede SPE über einen 256 KByte großen lokalen Speicher, der jedoch ohne Cache auskommen muss.

Dem PPE, welcher aus einer Integer Einheit XU, einer Gleitkomma-Einheit FPU (je 32 Register) und einer VMX-Einheit, wobei es sich um eine AltiVec-kompatible Recheneinheit handelt, besteht, stehen neben 512 KByte L2-Chache auch 2 x 32 KByte L1-Cache zur Seite. Insgesamt verfügt der ausgewachsene Cell-Prozessor, wenn man von einer PPE und acht SPEs ausgeht, über 2,5 MB Speicher, welcher sich in 512 kB L2-Cache für die Steuer-CPU und 8x256 kB für die 2,5 x 5,81 mm großen Synergistic Processor Units aufteilt.

| PlayStation 3 (Cell-CPU) |

Xbox 360 (CPU) |

Pentium 4 (500-Series) |

Pentium 4 (600-Series) |

Pentium D (800-Series) |

Core 2 Duo (Quad-Core) |

|

|---|---|---|---|---|---|---|

| Entwicklung | IBM, Sony, Toshiba | IBM | Intel | Intel | Intel | Intel |

| Fertigung | 90 nm (SOI) | 90 nm (SOI) | 90 nm | 90 nm | 90 nm | 65 nm |

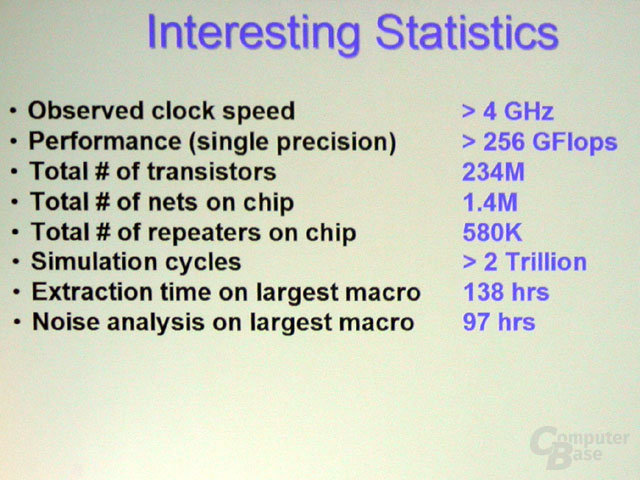

| Transistoren | 234 Mio. | 165 Mio. | 125 Mio. | 169 Mio. | 230 Mio. | 2 x 291 Mio. |

| Fläche | 221 mm² | 168 mm² | 112 mm² | 135 mm² | 206 mm² | 2 x 143 mm² |

| Prozessortakt | 3,2 GHz | 3,2 GHz | 2,8-3,8 GHz | 3,0-3,8 GHz | 2,8-3,2 GHz | 2,4-2,93 GHz |

| Kerne (Threads) | 1 PPE (2), 7 SPE | 3 (6) | 1 (2) | 1 (2) | 2 (2-4) | 4 (4) |

Die in der Tabelle genannte Fläche und die Transistorzahlen beziehen

sich auf den ausgewachsenen Cell-Prozessor mit vollen acht SPEs.

Die hohe Taktrate verdankt der Prozessor seiner Pipeline, welche IBM auch schon bei der Xbox 360 zum Einsatz kommen ließ. Statt der sonst üblichen dreifach-superskalaren und mittlerweile gar 4fach skalaren Out-Of-Order-Pipeline besitzt der Cell eine „nur“ zweifach-skalare In-Order-Pipeline, die einen wesentlich geringeren Grad an Komplexität aufweist, mit weniger Transistoren auskommt und bedeutend höher getaktet werden kann. Obwohl die Ausführungsreihenfolge von Befehlen somit nicht dynamisch angepasst werden kann, verfügt er über eine 23-stufige Pipeline. Zwölf Stufen (Frontend) dienen zum Holen, Dekodieren und Speichern der Instruktionen, während weitere vier bis elf Stufen (Backend) für das Ausführen und Speichern zuständig sind. Dies kann zwar zu höheren Wartezeiten führen – 18 Takte, bei falsch vorhergesagter Verzweigung – , aber nur so lässt sich die hohe Taktrate erreichen, wie man bereits beim Pentium 4 mit Prescott-Kern mit seiner 31-stufigen Pipeline gesehen hat. Da das PPE jedoch zwei Threads gleichzeitig abarbeiten kann, relativiert sich dieser Nachteil der In-Order-Pipeline, sofern Programme auf diese Multi-Threaded-Architektur ausgelegt wurden. Das Opfer ist jedoch eine geringere Performance bei Single-Threaded-Anwendungen. Die Idee der Out-of-Order-Execution ist simpel, die Umsetzung in Hardware jedoch kompliziert. Bei Out-of-Order (OoO) wird eine Abfolge von Instruktionen nicht wie bei In-Order stur hintereinander ausgeführt, sondern es wird durch komplizierte Hardware-Algorithmen versucht, voneinander weitgehend unabhängige Instruktionen auf die verschiedenen Verarbeitungseinheiten des Prozessors zu verteilen und so parallel – unabhängig von der eigenen Instruktionsreihenfolge – zu verarbeiten. Nach der Verarbeitung werden sie am Ende der Pipeline wieder in die richtige Reihenfolge gebracht. Dies trägt zur effektiven Ausnutzung der Hardware-Ressourcen bei und beschleunigt Programmcode, der nicht speziell für den Einsatz auf mehreren Prozessorkernen geschrieben wurde.

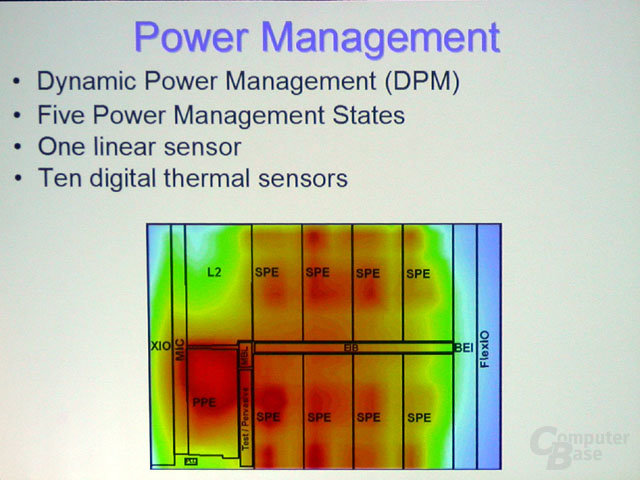

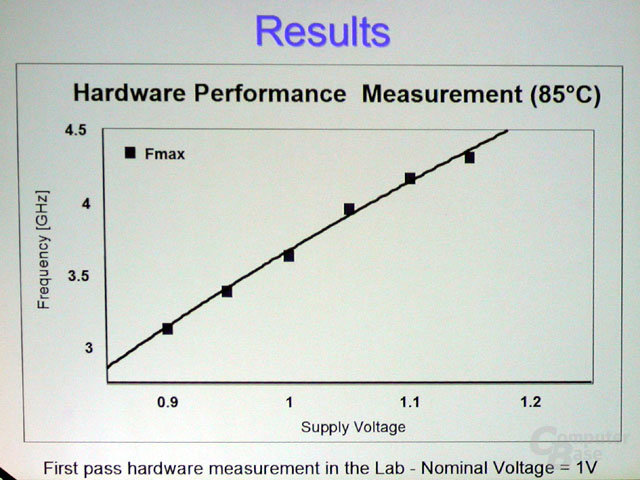

Dank dieser Architektur kann der Cell Berechnungen mit einfacher Genauigkeit, welche vor allem bei Spielen relevant sind, deutlich schneller verarbeiten als aktuelle Dual-Core-Prozessoren. So soll es der Cell bei 4 GHz und einfacher Genauigkeit auf über 256 Milliarden Gleitkommaoperationen pro Sekunde bringen. Wird mit doppelter Genauigkeit gerechnet, sollen hiervon noch 25 GFlop/s erreicht werden.