- Registriert

- Juli 2010

- Beiträge

- 12.926

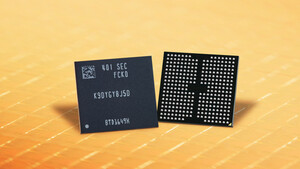

Auch in der Legend-Produktfamilie für Kreative erhöht Adata auf bis zu 7.400 MB/s beim Lesen. Die Legend 960 SSD als neue Speerspitze im M.2-Format soll überdies Daten mit bis zu 6.800 MB/s im SLC-Modus schreiben. Ende August kommt ein für das Format eher seltenes 4-TB-Modell. Noch seltener ist aber der Controller.

Zur News: Adata Legend 960: Schnelle M.2-SSD mit PCIe 4.0 ist vom Controller her ein Exot

Zur News: Adata Legend 960: Schnelle M.2-SSD mit PCIe 4.0 ist vom Controller her ein Exot