IDF 2012: Die CPU-Architektur „Haswell“ im Detail

Nachdem wir bereits die Neuerungen in Intels kommender CPU-Architektur „Haswell“ am Dienstag grob angerissen hatten, folgt an dieser Stelle nun eine etwas detailliertere Betrachtung, in der wir auch entsprechende Informationsfolien des Halbleitergiganten nachreichen.

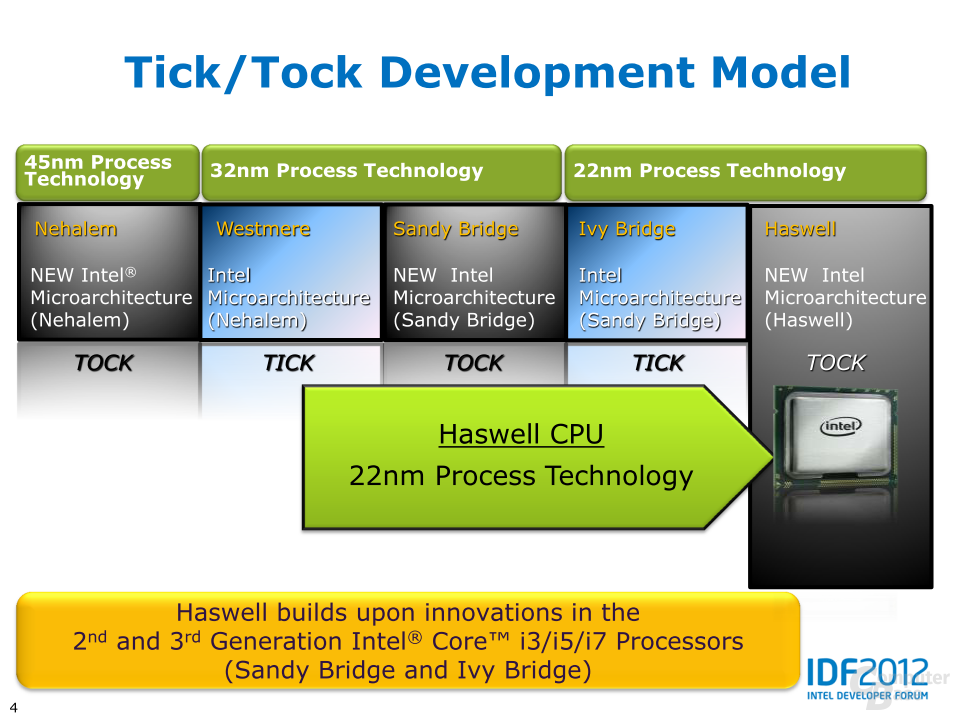

„Haswell“ stellt das nächste „Tock“ in Intels Prozessorfahrplan mit grundlegenden Änderungen an der Mikroarchitektur dar, während es sich beim Vorgänger „Ivy Bridge“ um eine optimierte Version der „Sandy Bridge“-Architektur mit feinerer Strukturbreite von 22 nm handelt, was Intel stets als „Tick“ bezeichnet. Erstmals hält mit „Haswell“ somit eine neue Architektur im 22-nm-Prozess von Intel Einzug.

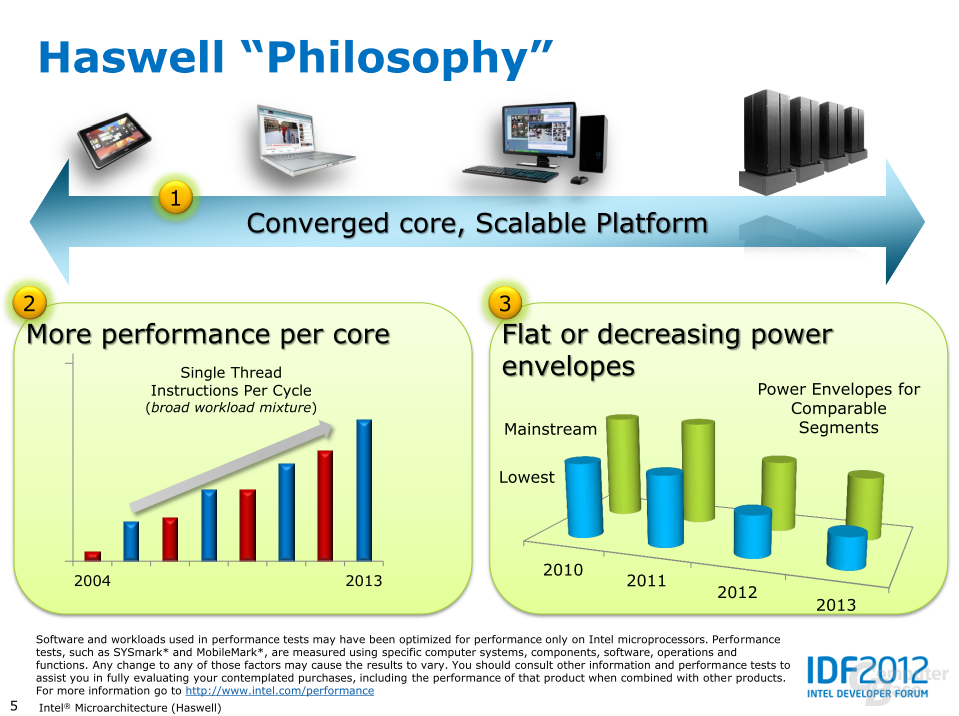

Bei der Entwicklung von „Haswell“ richtete Intel den Fokus generell auf eine höhere Leistung pro Kern, eine weiterhin verringerte Leistungsaufnahme sowie eine weitreichende Skalierbarkeit der Plattform – Stichwort: „von Tablet bis Server“. Darüber hinaus soll insbesondere die Leistung der integrierten Grafikeinheit deutlich zulegen, hierzu später mehr.

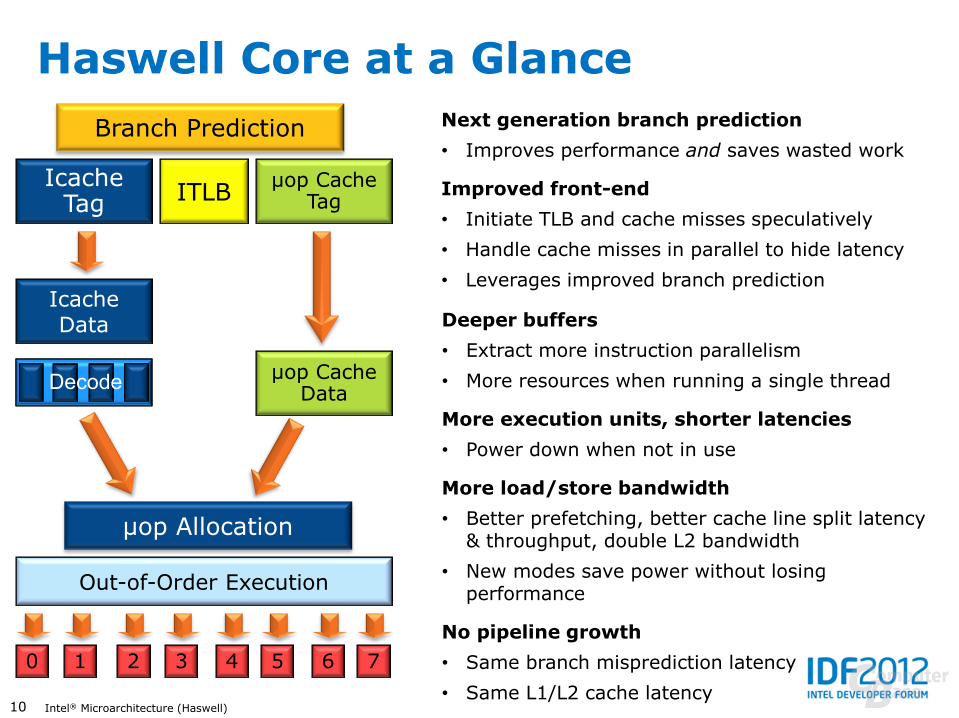

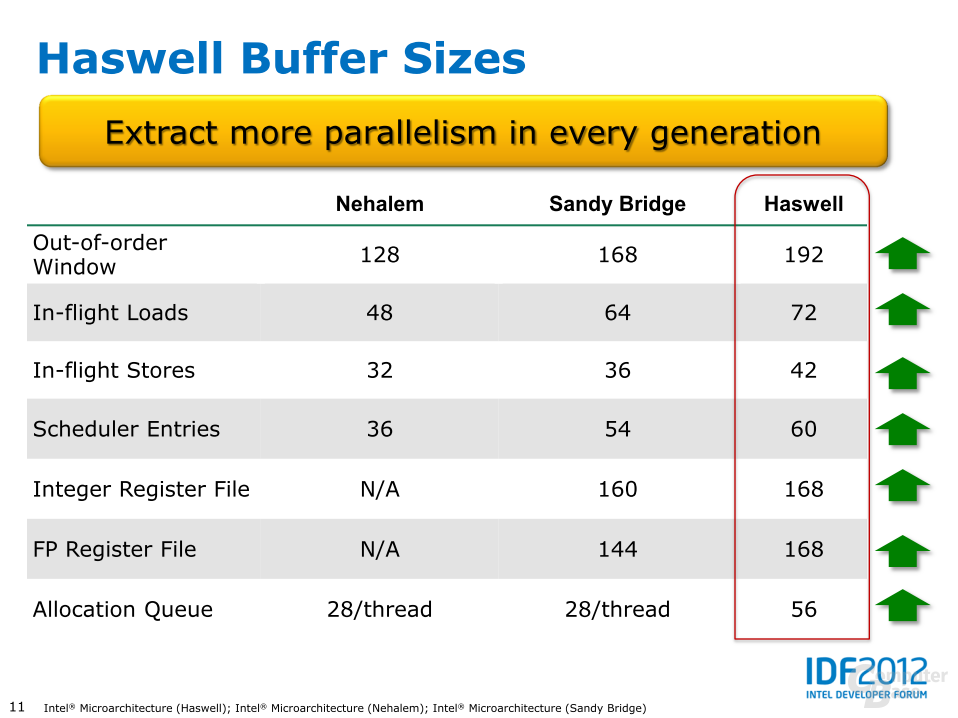

Für eine höhere Leistung sollen weitreichende Änderungen am Frontend sorgen. Hier ist insbesondere eine erneut verbesserte Sprungvorhersage (Branch Prediction) zu nennen, welche eine höhere Leistung durch reduzierte Fehlvorhersagen liefern soll. Cache- und TLB-Misses im L1-Instruktions-Zwischenspeicher werden nun spekulativ eingeleitet und können parallel abgearbeitet werden, wodurch die verbesserte Sprungvorhersage erst wirksam umgesetzt werden kann. Weiterhin wurden die Puffer (Buffer) vergrößert, um mehr Befehle parallel bearbeiten und für einzelne Threads mehr Ressourcen bereitstellen zu können. Wie die rechte der folgenden Abbildungen verdeutlicht, setzt Intel bei „Haswell“ in nahezu allen Bereichen größere Puffer als bei den Vorgängern ein.

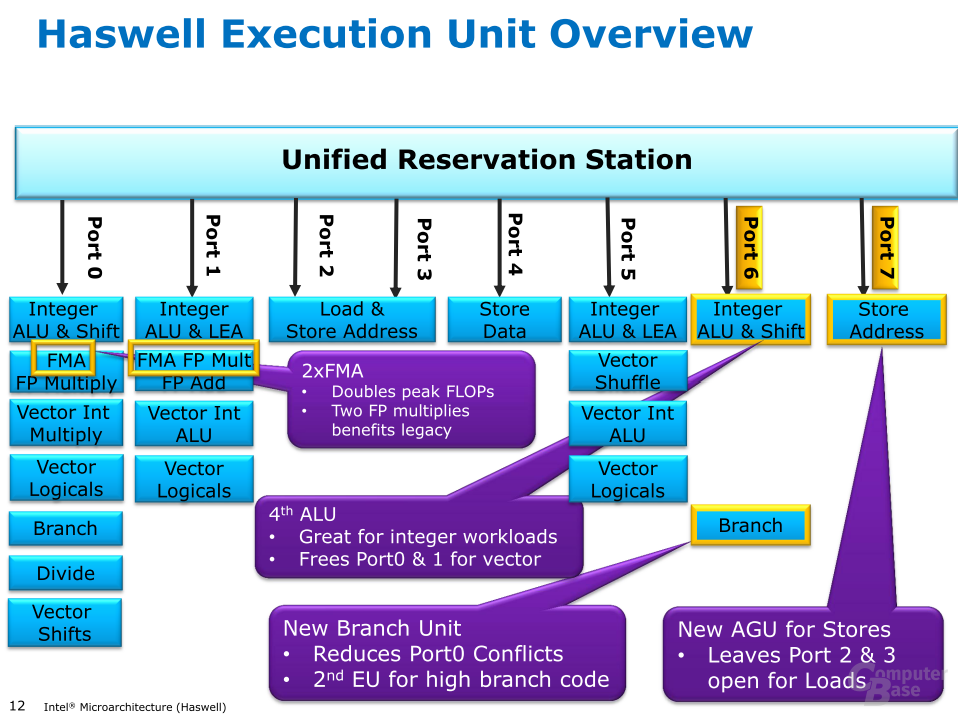

Damit die oben genannten Verbesserungen auch effektiv umgesetzt werden können, hat Intel zudem die Ausführungseinheiten (Execution Units) erhöht. Die Unified Reservation Station verfügt nun über acht statt sechs Dispatch-Ports. Dabei kommt eine vierte ALU sowie eine neue AGU hinzu. Erstere dürfte insbesondere Integer-lastige Workloads beschleunigen. Im Gegenzug werden andere Einheiten durch die Neulinge entlastet oder sind je nach Auslastung frei für andere Aufgaben. Zusätzlich kommt eine zweite Sprungeinheit (Branch Unit) zum Einsatz.

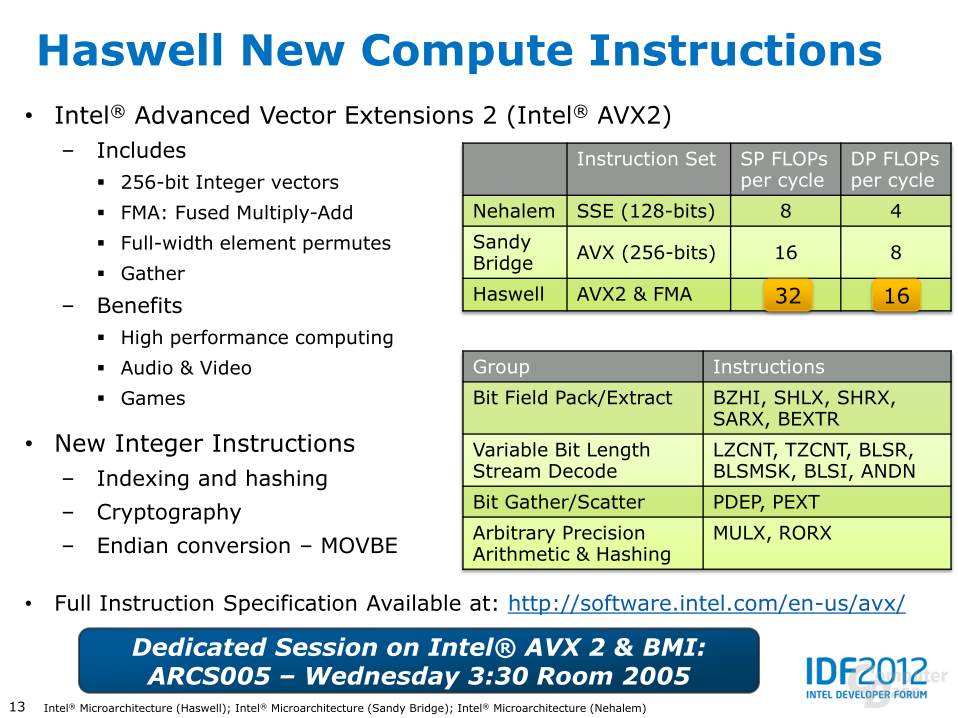

Im Bereich der Befehlssatzerweiterungen kann „Haswell“ ebenfalls mit umfangreichen Neuerungen aufwarten. So halten die Advanced Vector Extensions 2 (Intel AVX2) Einzug; zudem unterstützt Intel erstmals Fused Multiply-Add (FMA), das AMD bereits mit der „Bulldozer“-Architektur einführte. Die entsprechend optimierte Gleitkommaeinheit soll nun in der Spitze doppelt so viele FLOPs pro Taktzyklus erreichen wie „Sandy Bridge“. Entsprechend programmierte Anwendungen dürften spürbar beschleunigt werden. Darüber hinaus wurden auch neue Integer-Befehle hinzugefügt.

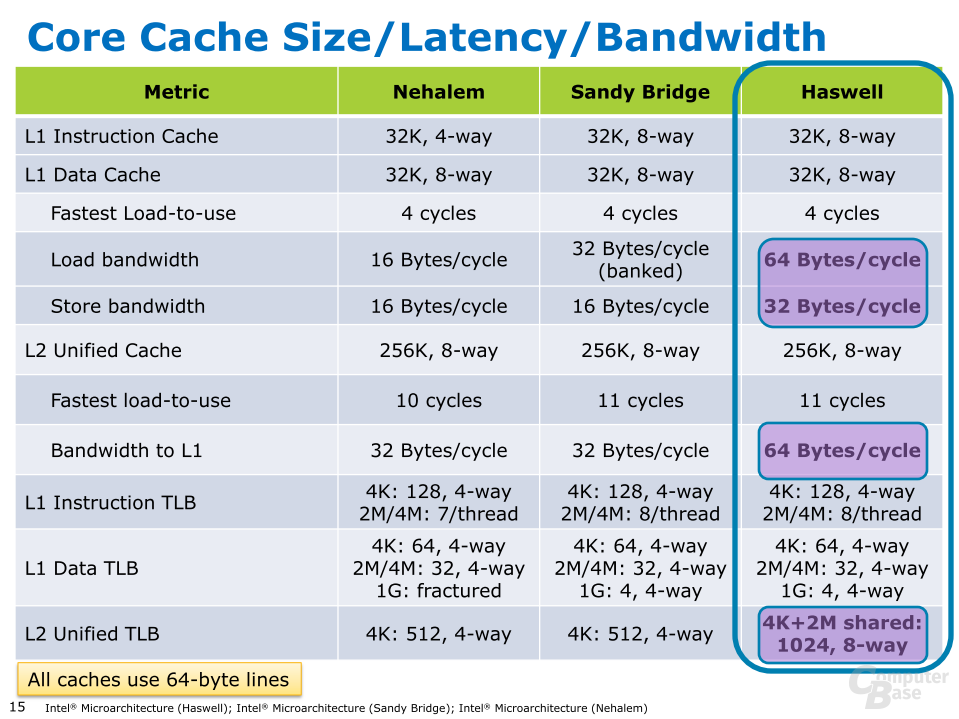

Damit all' diese Verbesserungen nicht durch womögliche Engpässe im Zwischenspeicher der Kerne verpuffen, hat Intel auch beim L1- und L2-Cache Hand angelegt. Während Cache-Größen und Assoziativitäten gegenüber „Sandy Bridge“ nicht verändert wurden, hat Intel deutlich an der Bandbreite geschraubt: Load und Store im L1-Daten-Cache (32 KB) wurden mit 64 respektive 32 Bytes pro Taktzyklus verdoppelt, gleiches gilt für die Bandbreite bei der Verbindung zwischen L1- und L2-Cache (256 KB), die nun bei 64 Bytes/Zyklus liegt. Zusätzlich wurde der L2-Unified-TLB durch geteilten Speicher erweitert und auf 1.024 Einträge gesteigert.

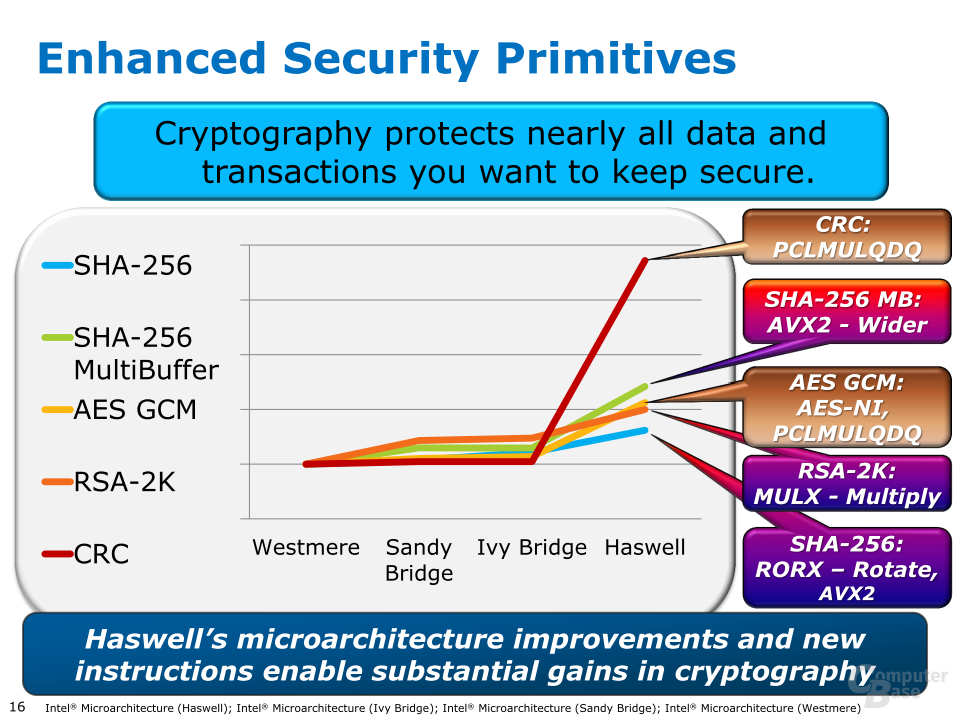

Durch die verbesserte Mikroarchitektur und neue Befehle sollen zudem deutliche Leistungssteigerungen im Bereich der unterstützten Verschlüsselungstechniken erreicht werden. Dies betrifft laut einer Grafik vor allem CRC. Nähere Details werden dabei jedoch nicht genannt.

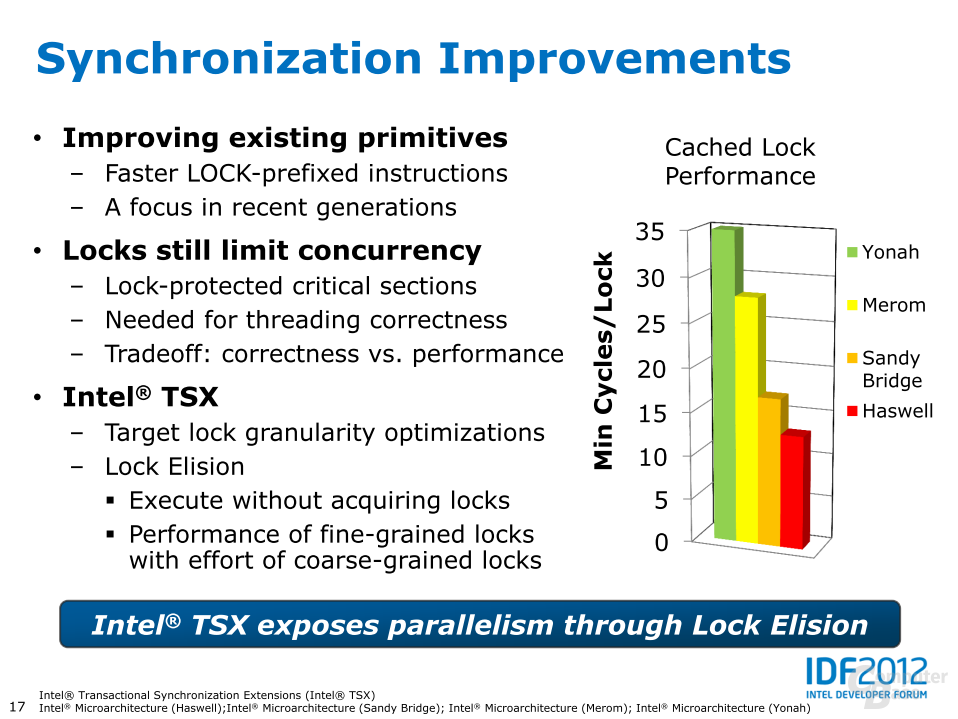

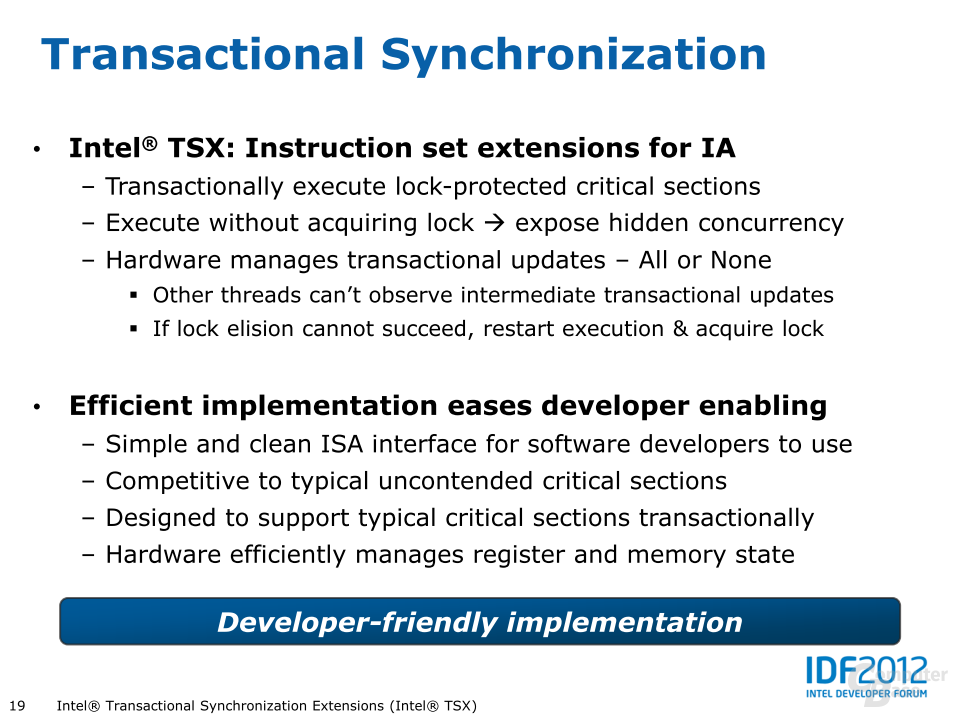

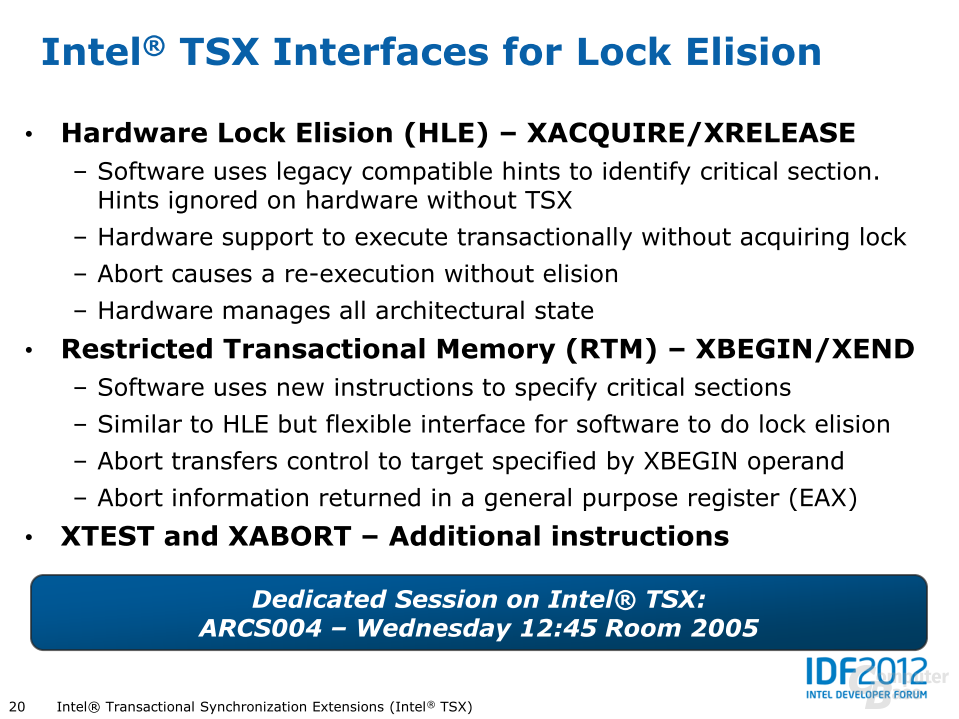

Die Unterstützung von Transaktionalem Speicher (Transactional Memory) feiert ebenfalls Premiere bei „Haswell“. Die Synchronisation von parallelen Threads, die auf Daten im gleichen Adressbereich zugreifen, kostet Zeit, welche bei „Haswell“ durch die Unterstützung der neuen Transactional Synchronization Extensions (TSX) reduziert werden soll, was allerdings einen entsprechenden Software-Support voraussetzt. Schließlich soll auch Intels Virtualisierungstechnik Intel VT Verbesserungen erfahren, wobei unter anderem schnellere Umschaltzeiten zwischen Host und Guest in Aussicht gestellt werden.

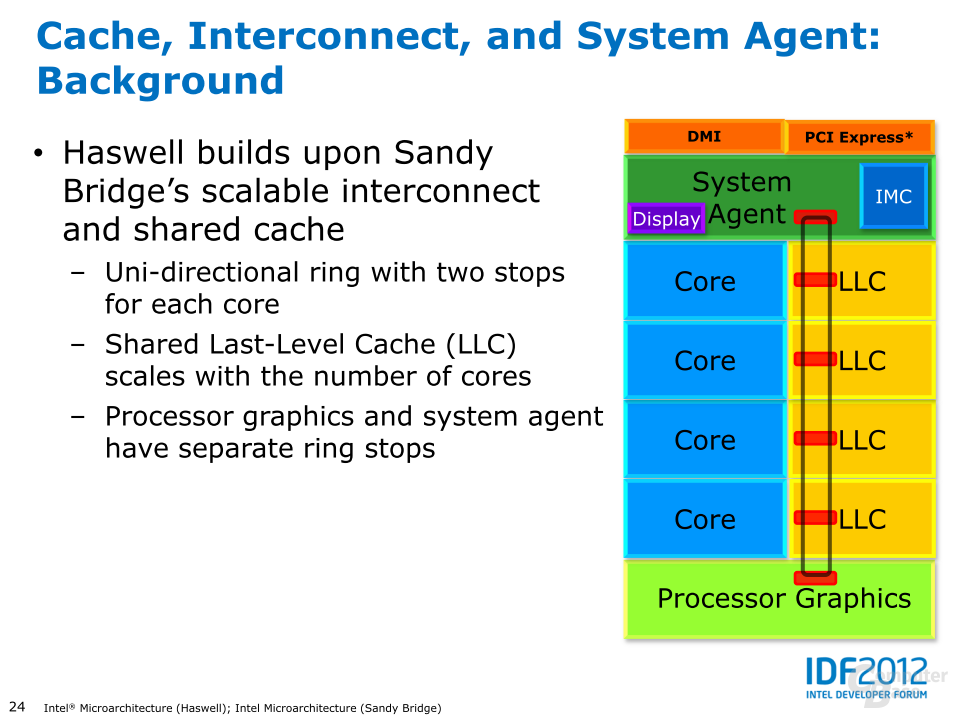

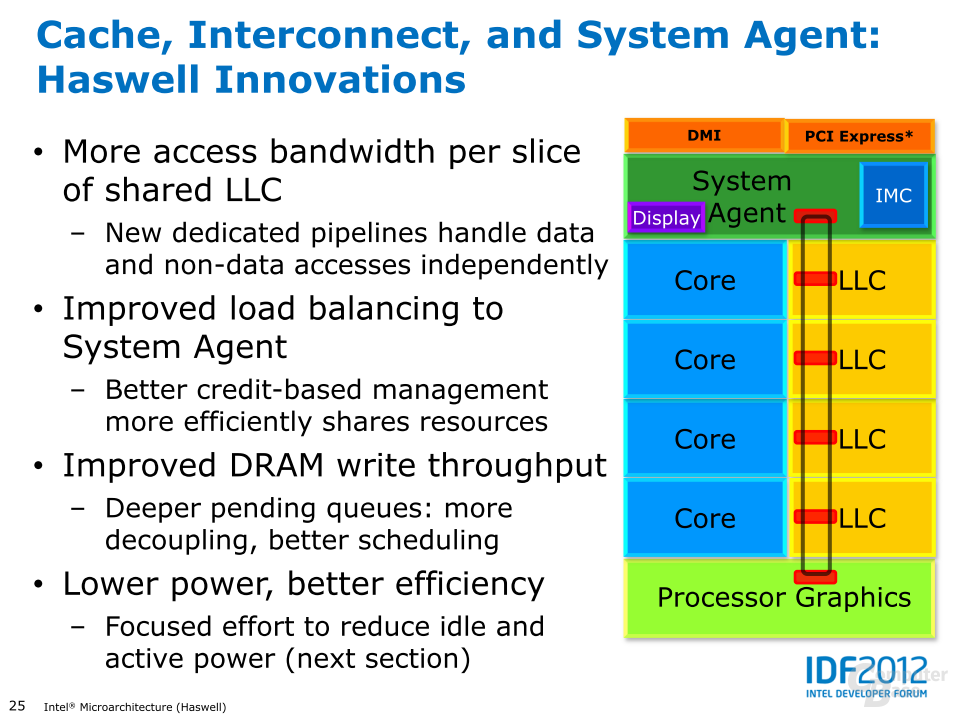

Während die Mikroarchitektur der Kerne offensichtlich grundlegend überarbeitet wurde, ändert sich an der Anordnung der Hauptkomponenten wenig. Den Kernen wird eine bisher nicht offiziell genannte Menge an geteiltem Last-Level-Cache (LLC) zur Seite gestellt, die entsprechend mit Anzahl der Kerne zunimmt. Über einen Ringbus ist der LLC mit dem System Agent und der integrierten Grafikeinheit verbunden. Die Bandbreite bei Zugriffen auf einzelne LLC-Abschnitte (Slices) soll dabei gesteigert worden sein. Weitere Verbesserungen werden im Load-Balancing des System Agent angeführt. Der integrierte Speichercontroller soll zudem höhere DRAM-Schreibraten erlauben.

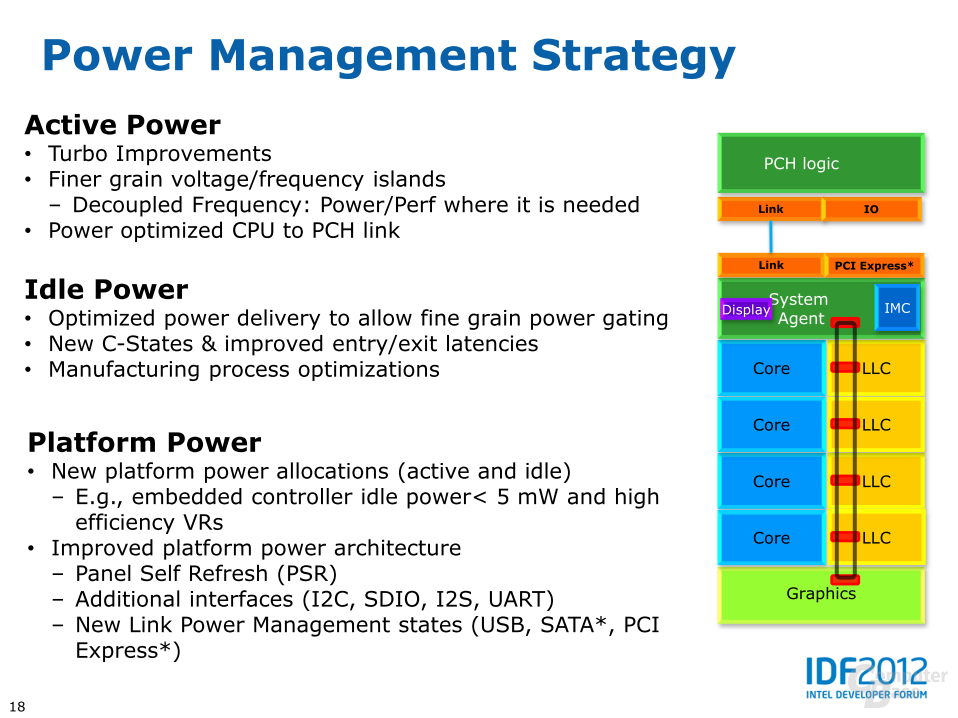

Um die Effizienz seiner Prozessoren weiter zu erhöhen führt Intel neben allgemeinen Optimierungen der Schaltkreise und des Herstellungsverfahrens eine ganze Reihe neuer Stromsparmechanismen ein. Der Last-Level-Cache erhält nun wie auch CPU-Kerne und GPU eine eigene Taktdomäne, wodurch unterschiedliche Frequenzen möglich sind. Den größten Sprung macht man bei der Leistungsaufnahme im Leerlauf, womit man insbesondere auf höhere Akkulaufzeiten in Mobilgeräten abzielt. Hierbei soll ein verbessertes Power Gating, neue C-States sowie verringerte Umschaltzeiten zwischen den Zuständen ihren Beitrag leisten.

Zu den Maßnahmen zählt der Energiestatus (Power State) C7, bei welchem nicht benötigte Blöcke des Prozessors praktisch komplett abgeschaltet werden. Der C7-Status soll sogar möglich sein, wenn auf dem Bildschirm ein Bild dargestellt wird. Mit dem neuen S0ix-State will Intel „Haswell“ Tablet-tauglich machen, indem dieser den Idle-Verbrauch weiter reduziert, wobei von einer Reduktion um den Faktor 20 gegenüber dem Vorgänger die Rede ist. Dabei soll das als „Active Idle“ bezeichnete S0ix ebenso wenig Strom benötigen wie der Schlafmodus S3/S4, dafür aber umso schnellere „Aufweckzeiten“ besitzen.

Dem Grafikteil von „Haswell“ widmen wir uns in einer separaten News.