Wafer-Level SSD: Kioxia erwägt Wafer als direkten Massenspeicher

Auf dem in diesem Jahr online ausgetragenen VLSI Symposium 2020 hat Shigeo „Jeff“ Oshima, der Chef-Ingenieur vom NAND-Flash-Hersteller Kioxia, über die Zukunft von Flash-Speicher gesprochen. Neben bereits bekannten technischen Ansätzen kam eine kurios anmutende Idee zur Sprache: die sogenannte Wafer-Level SSD.

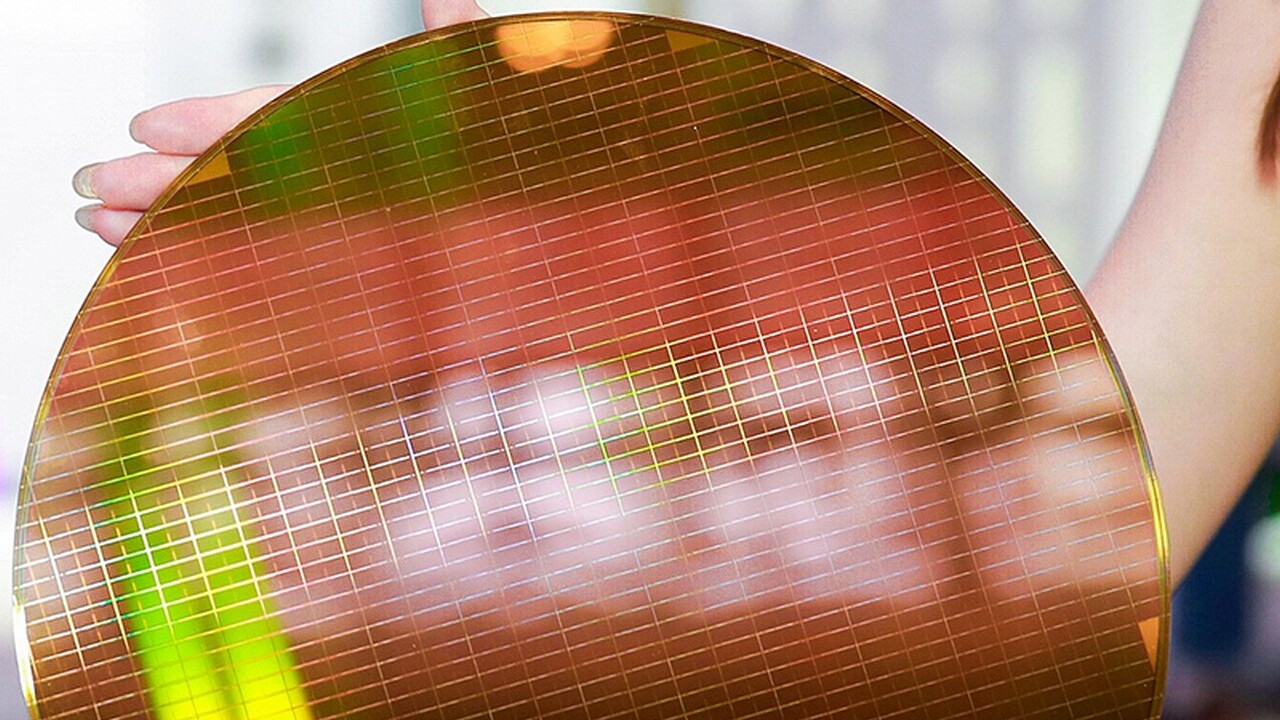

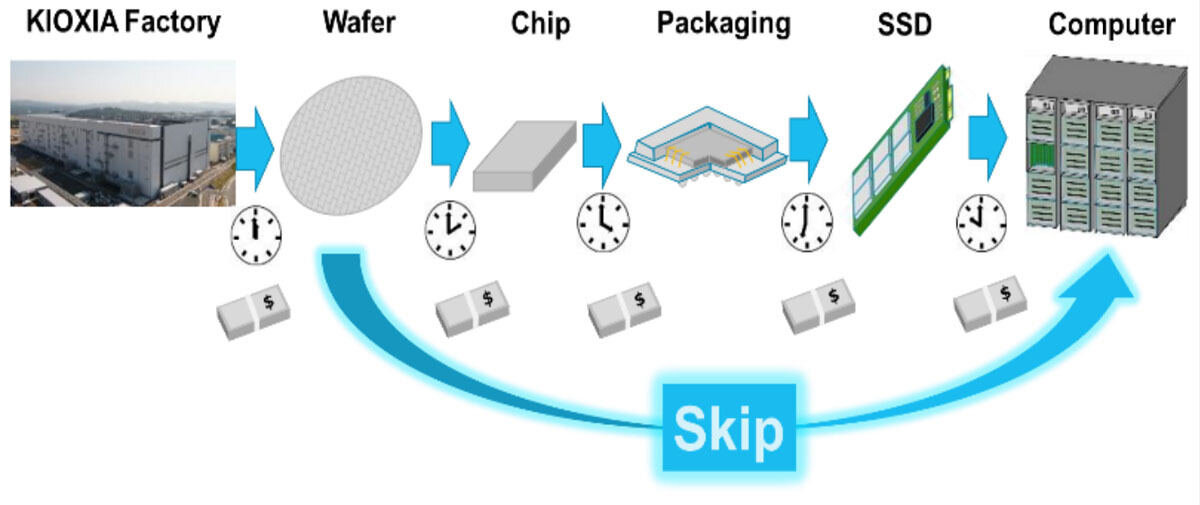

Abseits von bekannten Ideen wie mehreren hundert Zellebenen bei 3D-NAND oder 5 Bit pro Speicherzelle (PLC-NAND) zur weiteren Steigerung der Speicherkapazitäten erwägt Kioxia offenbar auch einen völlig neuen Ansatz zum Einsatz der Speicherchips. Bisher wird NAND-Flash in Form zahlreicher Dies aus einem Silizium-Wafer geschnitten, wie es bei Halbleiterchips nun einmal üblich ist. Die einzelnen Dies respektive Chips werden anschließend in Chip-Gehäuse verpackt (Packaging) und dann auf Platinen von SSDs oder anderen Speicherprodukten untergebracht. Vom Wafer bis zum Endprodukt sind also diverse Schritte nötig.

Der Wafer wird selbst zur SSD

Die neue und durchaus radikal anzusehende Idee umgeht diesen Prozess und macht praktisch den Wafer selbst zur SSD. Der Wafer samt den darauf enthaltenen Speicherchips soll direkt in einem Computersystem als Massenspeicher eingesetzt werden. Mithilfe einer „super multi-probing technology“ sollen die Chips direkt auf dem Wafer angesprochen werden. Sogenannte Wafer-Prober dienen derzeit als Testgeräte zur Überprüfung fehlerhafter Schaltungen im Rahmen eines Wafer-Test. Das Konzept von Kioxia wird als Wafer-Level SSD beschrieben und soll durch das Wegfallen der beschriebenen Arbeitsschritte die Kosten reduzieren und durch den parallelen Zugriff auf hunderte von Speicherchips für hohe Leistung sorgen.

Der Bericht aus Japan geht allerdings nicht konkret auf die dafür nötige Technik und die damit verbundenen Kosten ein. Zudem ist das Konzept nur für Rechenzentren geeignet, denn die Kombination aus Wafern mit heutzutage üblichen 30 cm Durchmesser und zugehöriger Technik zum Lesen und Beschreiben der einzelnen Speicherchips würde neue Formfaktoren mit großem Platzbedarf erfordern. Durch die Vielzahl der Speicherchips wären aber auch riesige Speicherkapazitäten denkbar, die zahlreiche SSDs der üblichen Formate ersetzen könnten.