DigiTimes: YMTC überspringt 192L und geht direkt auf 232L-3D-NAND

Bisher ist es nur ein Gerücht: Laut Quellen von DigiTimes wird der chinesische NAND-Flash-Hersteller YMTC die 192-Layer-Generation überspringen und direkt auf die nächste Generation mit 232 Zellebenen wechseln. In puncto Layer-Anzahl des 3D-NAND würde YMTC damit zu Micron aufschließen.

DigiTimes beruft sich im Bericht (Paywall) auf Branchenquellen aus China. Eine Bestätigung der angeblichen Pläne gibt es bisher aber nicht.

Lässt YMTC 192 Layer aus?

Erst vor einem Monat hatte DigiTimes über erste Muster-Chips (Samples) der 192-Layer-Generation von YMTC berichtet. Sollten die Informationen stimmen, wird dieses Chip-Design aber nicht den Markt erreichen. Ob dies Probleme mit dem 192-Layer-NAND bedeutet, darüber lässt sich nur spekulieren. Im Gegenzug könnte die Entwicklung des 232-Layer-NAND schneller fertig werden als gedacht und daher den Vorzug erhalten. Wann der 232-Layer-NAND von YMTC den Markt erreichen soll, wird allerdings nicht genannt.

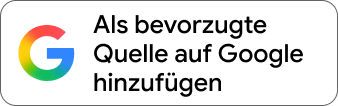

Micron ist schon bei 232 Layern angekommen

In puncto Anzahl der Ebenen mit Speicherzellen bei 3D-NAND ist aktuell Micron führend. Der US-Hersteller hat erst letzten Monat seinen 232-Layer-NAND vorgestellt, der gegen Ende des Jahres in die Serienfertigung gehen soll. Die Speicherkapazität von 1 Terabit pro Die in der TLC-Variante mit 3 Bit pro Zelle ist doppelt so hoch wie bei bisherigem TLC-NAND im Markt.

Samsung und SK Hynix, die beiden großen NAND-Flash-Hersteller aus Südkorea, werden voraussichtlich erst im kommenden Jahr die Marke von 200 Layern in der Massenfertigung überschreiten.

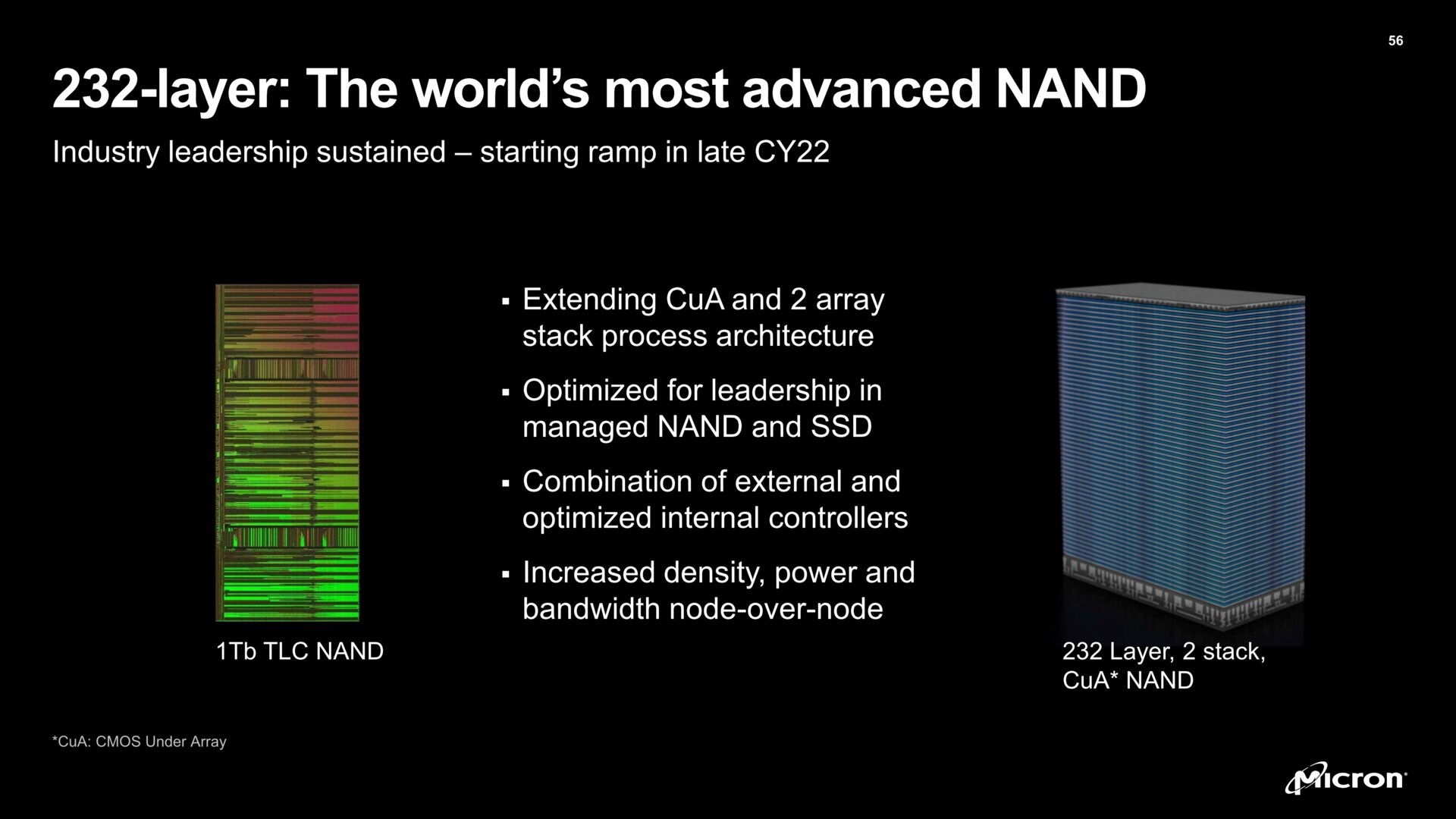

Im Layer-Wettrennen sind die Partner Kioxia (Japan) und Western Digital (USA) ins Hintertreffen geraten und wollen erst bei der für Ende 2023 geplanten Generation „BiCS+“ mehr als 200 Layer bieten.

Layer-Anzahl allein wenig aussagekräftig

Zu Recht haben beide aber jüngst betont, dass die Anzahl der Zellschichten allein wenig über den 3D-NAND aussagt, denn viele weitere Faktoren wie die Größe der Zellen und deren Abstand bestimmen die Eigenschaften des NAND-Flash. So soll die neue Generation BiCS6 trotz nur 162 Layern eine größere Bit-Dichte als die 176-Layer-Chips der Konkurrenz bieten.

YMTC wurde unterschätzt

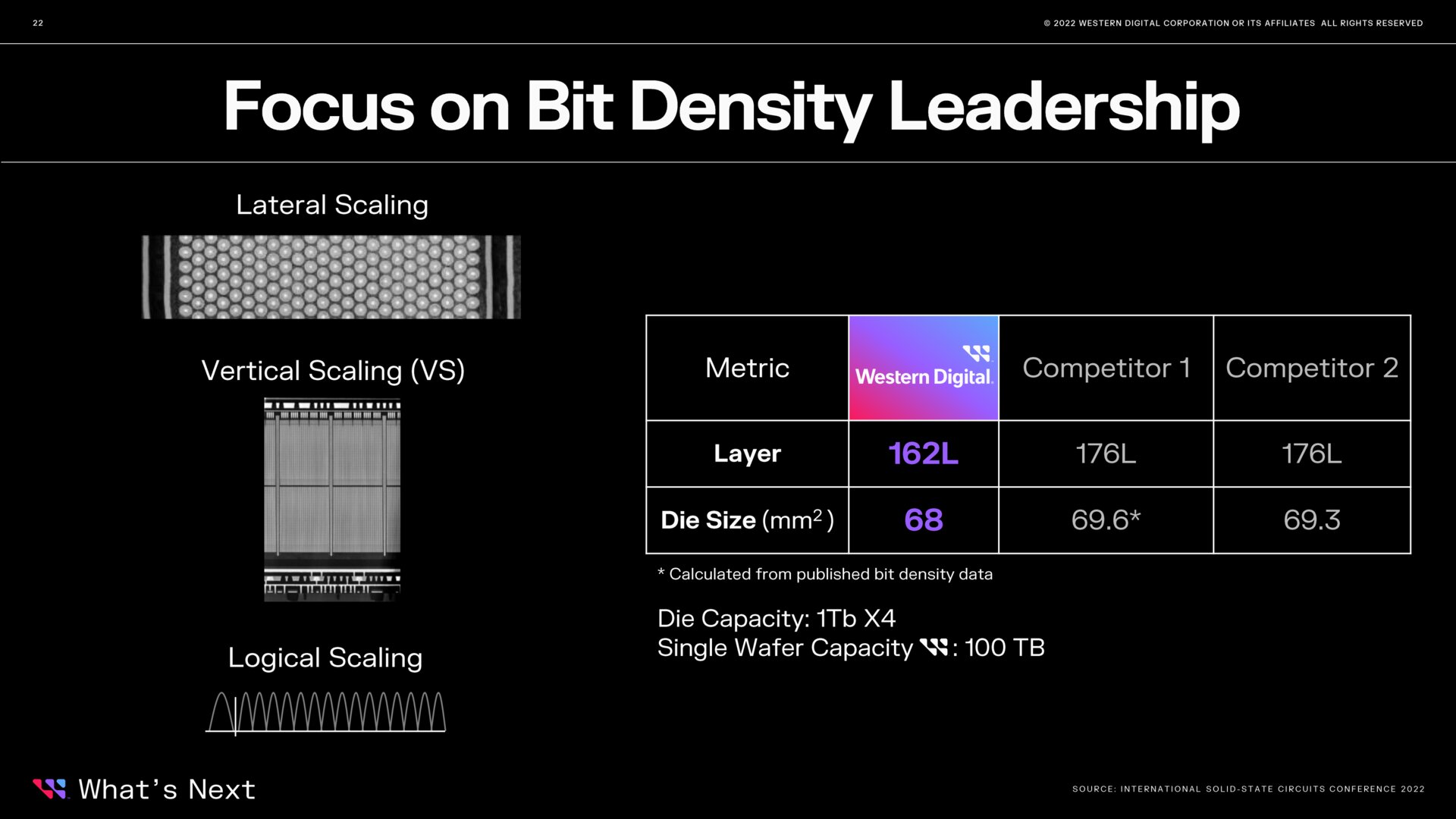

Ob nun 192 Layer oder direkt 232 Layer: Der Newcomer Yangtze Memory Technologies Co. (YMTC) aus China wurde von vielen unterschätzt. Der 128-Layer-NAND von YMTC erhielt in einer Analyse der Experten von TechInsights Anerkennung. Diese konstatierten YMTC, zur etablierten Konkurrenz aus Südkorea, Japan und den USA ordentlich aufgeholt zu haben. In puncto Flächendichte und Durchsatz sei die sogenannte Xtacking-Architektur von YMTC besonders stark. Dabei wird der Bereich mit Speicherzellen und jener mit der Peripherie (I/O) auf jeweils unterschiedlichen Wafern produziert und dann zu einem 3D-NAND-Chip vereint.

Nach anfänglichen Schwierigkeiten mit einer geringen Ausbeute funktionsfähiger Speicherchips sollen sich die „Yields“ inzwischen auf einem zufriedenstellenden Niveau bewegen, sodass der Ausstoß auf 100.000 Wafer angehoben worden sei, berichtete im Mai abermals DigiTimes. Laut unbestätigten Berichten wird Apple bereits als potenzieller Großkunde gehandelt.