Packaging-Verfahren: UMC startet eigene Wafer-auf-Wafer-Stapellösung

UMC will ein Stück vom großen Kuchen des Advanced Packaging. 2024 soll eine Wafer-auf-Wafer-Stapellösung für Kunden bereitstehen. Um einen Zugang für Kunden möglichst einfach zu gewährleisten, holt man sich mit Cadence, Winbond, Faraday und ASE namhafte Partner aus der Industrie ins Boot.

Packaging-Arten gibt es viele, der Markt entsprechend groß, um die Chips von einem Wafer auf ihr Substrat zu setzen und letztlich an die Kunden zu verkaufen. Die Ansprüche der Kundschaft sind in den letzten Jahren aber gestiegen, das Packaging ermöglicht in verbesserter Form zusätzliche Möglichkeiten. Von diesem Advanced Packaging will UMC nun auch ein größeres Stück vom Kuchen bekommen. Marktführer ist bekanntlich TSMC mit vielen Varianten, deren Problem ist jedoch aktuell die viel zu große Nachfrage, die noch mindestens bis Ende 2024 nicht befriedigt werden kann. Deshalb baut auch TSMC die Kapazitäten fleißig aus.

UMC spricht davon, im kommenden Jahr das Stacking von Wafer zu Wafer (W2W) anzubieten. Dabei bezieht sich der taiwanische Auftragsfertiger aber nicht auf SoCs, sondern in erster Linie auf eine SoC-DRAM-Kombination, was zum Teil auch erklärt, warum Winbond mit im Boot ist, denn diese haben Erfahrung mit DRAM, NAND und sonstigen Speicherchips. Cadence wiederum bringt die benötigte IP und die Zertifizierungen mit in das Geschäft, Faraday hilft bei den kommenden passenden Produktlösungen, während ASE die Behandlung der Chips vom Zersägen der Wafer bis zum eigentlichen Packaging am Ende übernimmt.

Zielgruppe sind „AI-Chips“ im Massenmarkt

Die Zielgruppe sind keine absoluten High-End-Chips, auf der AI-Welle (Künstliche Intelligenz) wollen alle Beteiligten dennoch mitschwimmen. Als Chips sind deshalb Lösungen für den IoT-Bereich sowohl daheim als auch in der Industrie geplant, hinzu kommen Produkte für den Sicherheitsbereich und die smarte Infrastruktur. Unterm Strich sind es laut den Beteiligten Firmen Chips mit „mid-to-high range computing power, extensive and customizable memory modules, and relatively low power consumption“.

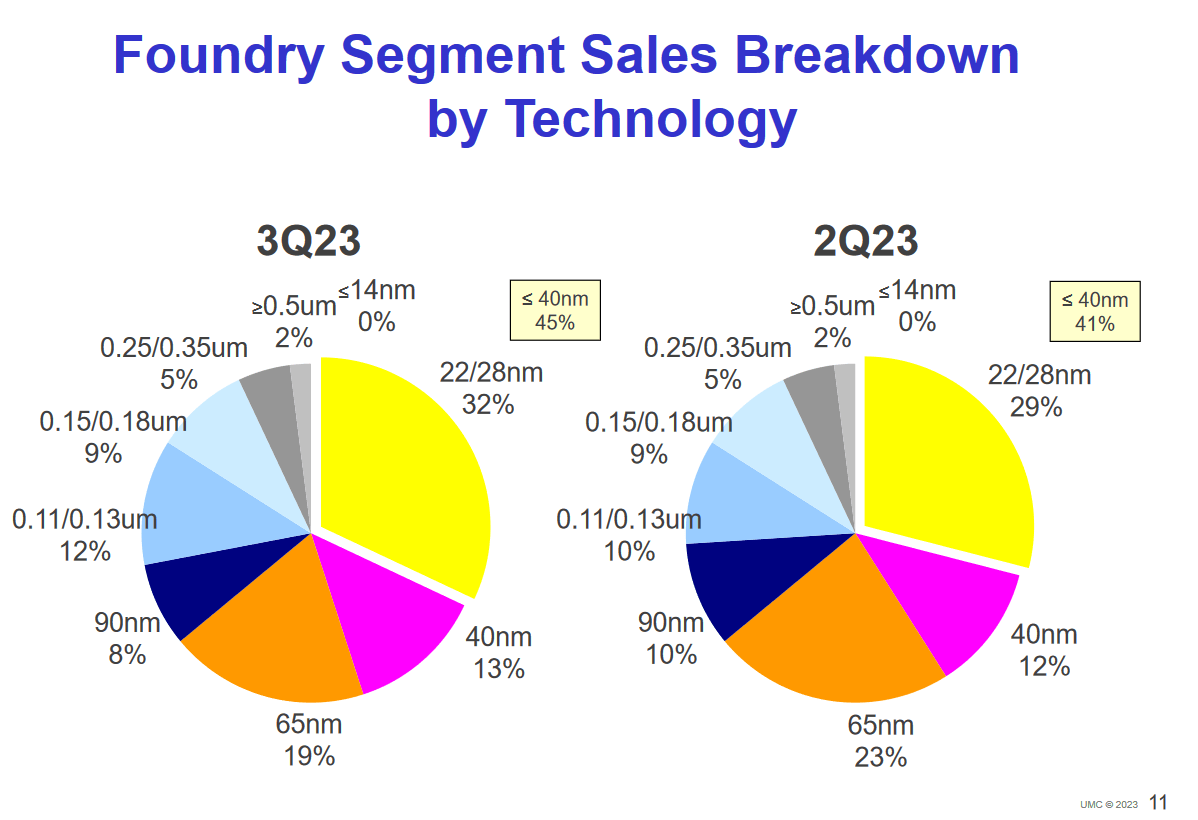

Diese wiederum passen zum Portfolio von UMC. Denn die beste Fertigung, die es in dieser Foundry gibt, ist 14 nm, die wiederum aber zuletzt nicht in Anspruch genommen wurde. Stattdessen liegen 22/28 nm und 65 nm nach wie vor hoch im Kurs, flankiert von 40 nm und auch noch 90 nm und größeren Strukturen, die vor allem in der Industrie nach wie vor genutzt werden.