Complication

Banned

- Registriert

- Okt. 2009

- Beiträge

- 4.277

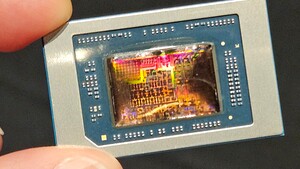

Du solltest dich mal eingehender mit der APU Architektur beschäftigen.y33H@ schrieb:Natürlich müssen sich in einer APU die CPU und die GPU die Bandbreite teilen

Und warum sollte der Transferaufwand geringer sein, nur weil CPU und GPU in den gleichen Speicherbereich schreiben können?

Bei deinem nicht vorhandenem Kenntnisstand macht eine technische Diskussion kaum einen Sinn.

http://sites.amd.com/de/Documents/48423B_fusion_whitepaper_WEB.pdf

http://de.wikipedia.org/wiki/AMD_Fusion#cite_note-amd1-3

Das bedeutet dass ein grosser Teil der Daten nicht wie bisher transferiert wird und dementsprechend der Hinweis auf geteilte Speicherbandbreite nur von ahnungslosen kommt - es ist nicht relevant. Es ist nur bei Intel Systemen relevant die keine APU haben.Obwohl die skalaren x86er-Kerne und SIMD-Engines der APUs einen gemeinsamen Pfad zum Systemspeicher teilen, soll die erste Generation der AMD APUs den Speicher noch in verschiedene Speicherregionen teilen. Zum einen in einen Speicherbereich, der vom Betriebssystem verwaltet wird, welches auf den x86er-Kernen läuft, zum anderen in Speicherregionen, die von der Software verwaltet werden, welche auf den SIMD-Engines ausgeführt wird. Für den Datentransfer zwischen den beiden Speicherregionen hat AMD High-Speed-Block-Transfer-Engines eingerichtet. Im Gegensatz zu Datentransfers zwischen externen Framebuffern und dem Systemspeicher sollen diese Transfers nie den externen Systembus belegen