M-O-R-P-H

Ensign

- Registriert

- Mai 2006

- Beiträge

- 180

Servus,

Es wird immer wieder gern gefragt, wie schnell denn eigentlich der Arbeitsspeicher in nem flotten

System sein sollte. Meist heißt es, das was der FSB packt, reicht völlig ...

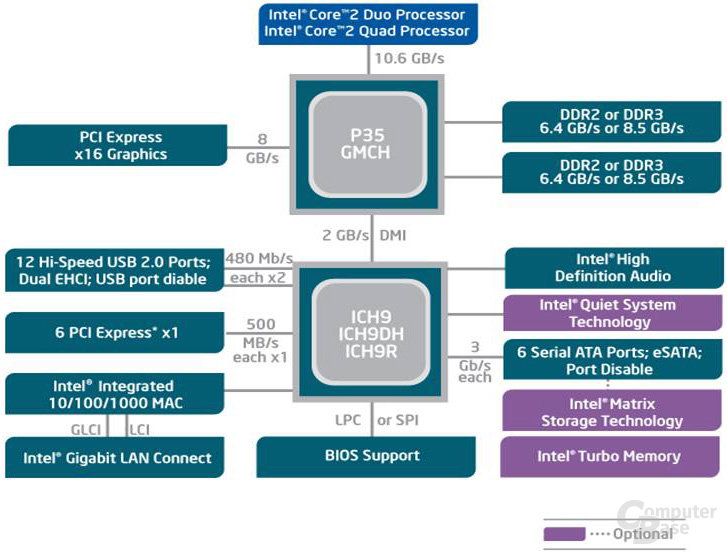

Aber wie is das eigentlich wenn neben der CPU andere Komponenten per DMA (Festplatte, PCI(-E) Geräte)

selbst auf den Ram zugreifen, sprich ohne/kaum CPU Last? Kann der Ram dann nicht seine überschüssigen Kapazitäten

nutzen, während der FSB am Limit arbeitet?

Z.B. bei vielen Anwendungen und vielen Datentransfers durch S-ATA / P-ATA / USB / LAN Schnittstellen ...

Is wohl nur Theorie, aber vllt finden sich fundierte Tests ..

Es wird immer wieder gern gefragt, wie schnell denn eigentlich der Arbeitsspeicher in nem flotten

System sein sollte. Meist heißt es, das was der FSB packt, reicht völlig ...

Aber wie is das eigentlich wenn neben der CPU andere Komponenten per DMA (Festplatte, PCI(-E) Geräte)

selbst auf den Ram zugreifen, sprich ohne/kaum CPU Last? Kann der Ram dann nicht seine überschüssigen Kapazitäten

nutzen, während der FSB am Limit arbeitet?

Z.B. bei vielen Anwendungen und vielen Datentransfers durch S-ATA / P-ATA / USB / LAN Schnittstellen ...

Is wohl nur Theorie, aber vllt finden sich fundierte Tests ..