Intel Nova Lake aus N2P-Fertigung: 8P+16E-Kerne samt 144 MB L3-Cache werden ~150 mm² groß

Die Topmodelle von Intel Nova Lake werden wie zuletzt bereits vermutet CPU-Tiles von TSMC nutzen. Diese werden bis zu 154 mm² groß sein – und können, wie ebenfalls bereits bekannt, dann auch zwei Mal pro Prozessor verbaut sein. So entsteht zusammen mit den anderen Chips dann ein durchaus großes Gesamtkonstrukt.

Top-Ausbau von Nova Lake wird viel Die-Fläche nutzen

Schon seit einigen Tagen sind mal 150 mm² oder auch 154 mm² im Gespräch, die der größte Ausbau des CPU-Tiles von Intel Nova Lake als Platz nutzen wird. Das ist die Variante mit dem sogenannten bLLC, das steht für „big Last Level Cache“, also ein großer gemeinsamer L3-Cache mit einer Kapazität von 144 MByte. Anders als bei AMDs Ansatz wird dieser aber nicht gestapelt, sondern der CPU-Tile dafür vergrößert. Er wächst so auf rund 150/154 mm². Die reguläre Version für den Massenmarkt, die ohne den bLLC auskommt, wird mit nach wie vor maximal 36 MByte L3-Cache für 8P+16E-Kerne auf rund 110 mm² CPU-Die-Fläche kommen, zuvor wurden aber auch schonmal nur 94 mm² genannt.

Dass Intel dafür auf TSMC zurückgreift, hat sich über die letzten Monate manifestiert. Intel wird allem Anschein nach kleinere Dies später in Intel 18A selbst fertigen, Nova Lake soll schließlich auch im mobilen Segment im Jahr 2027 angesiedelt werden. Die High-End-Chips für den Desktop mit maximal möglichem Takt (und Verbrauch) kommen aus der Ende 2026 wohl besten Fertigung: TSMC N2P. Dieser Node wurde in den Berichten der letzten Tage noch einmal genau genannt.

N2P für High-End-Chips bei Intel zu nutzen überrascht nicht, auch AMD setzt bei den Zen-6-CCDs für Epyc wohl direkt auf TSMC N2P. Ein 12-Kern-CCD mit 48 MByte L3-Cache ist dort ungefähr 76 mm² groß, wurde in der vorletzten Woche berichtet. 24 Kerne (plus SMT) und knapp 100 MByte L3 belegen hier zusammen also rund 150 mm², ausgelagert ist bei AMD jedoch der Speichercontroller, auch vieles weitere steckt in einem anderen Die.

NVL 8+16 Die TSMC N2 ~110+mm2

— HXL (@9550pro) February 11, 2026

NVL 8+16 bLLC Die TSMC N2 ~150+mm2 https://t.co/beHNikpl1O

Der Vollausbau von Nova Lake könnte teuer werden

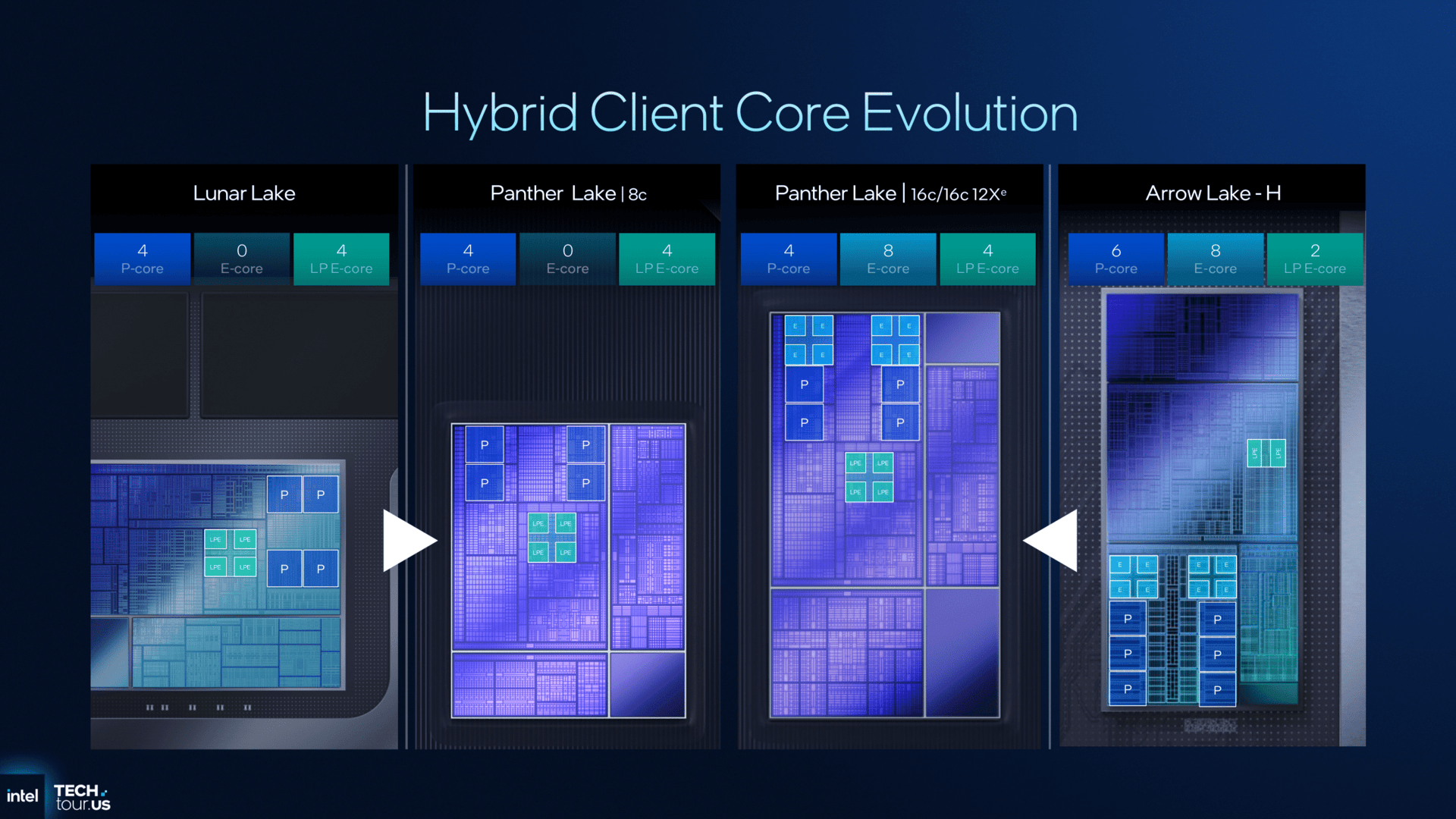

Diese CPU-Dies im Doppelpack, zusätzlich dazu mindestens ein GPU-Tile und der stets benötigte I/O-Tile dürften im Gesamtpaket einen Chip entstehen lassen, der eine Die-Fläche von 400+ mm² aufweist. Kleinere Chip-Varianten mit anderen Dies werden entsprechend viel weniger Fläche nutzen und so die Wirtschaftlichkeit in diesen Märkten sicherstellen. Intel dürfte auch hier eine Mischung aus TSMC-Fertigungsstufen und eigenen Lösungen nutzen – so wie zuletzt bei Intel Panther Lake. Die größten Chips dürften dadurch aber auch das bisherige Preisgefüge übertreffen.

Zusammenfassung der bisherigen Gerüchte

An der Spitze stehen bei Nova Lake-S für den Desktop Gerüchten zufolge pro Die 8P + 16E (+LPE?) Kerne, was zusammen über zwei Dies kombinierte 52 Kerne ergibt. Darunter sollen Varianten mit 42, 28 und 24 Kernen angesiedelt sein. Aktuell ist bei 8+16 (24) Kernen Schluss. Zusätzlich soll es vier Modelle mit großem Zusatz-Cache wie bei den X3D-CPUs von AMD geben. Bis zu 288 MByte sind dann in doppelter Form im Core Ultra 9 4xx im Gespräch:

- Core Ultra 9 4xxK, 52 Kerne (16P+32E+4LPE), 288 MB bLLC

- Core Ultra 9 4xxK, 42 Kerne (14P+24E+4LPE), 288 MB bLLC

- Core Ultra 7 4xxK, 28 Kerne (8P+16E+4LPE(?)), 144 MB bLLC

- Core Ultra 7 4xxK, 24 Kerne (8P+12E+4LPE(?)), 144 MB bLLC

Darunter werden viele weitere CPUs ohne den Zusatzcache erwartet. Geht es nach den letzten Gerüchten, könnte Intel aber den Fokus in diesem Jahr ganz klar zuerst auf die bLLC-Lösungen setzen. Alles was echter Mainstream ist, wird erst 2027 folgen.