Open Memory Interface: Speichercontroller gegen DRAM-Limit bei Server-CPUs

Microchip stellt mit dem SMC1000 8X25G einen seriellen Speichercontroller für DRAM vor, der das von OpenCAPI abgeleitete Open Memory Interface (OMI) nutzt. Der Hochgeschwindigkeitslink zum Host-Prozessor mit 25 GT/s pro Lane benötigt deutlich weniger Pins als das DIMM-Interface, was größere Mengen RAM ermöglicht.

Speichercontroller nutzt das Open Memory Interface

Das Herzstück des SMC 1000 ist ein sogenannter Serialisierer/Deserialisierer, der es einer kompatiblen CPU erlaubt anstelle einer 288-poligen DIMM-Schnittstelle eine 84-polige serielle Verbindung zu verwenden, ohne dabei an Bandbreite einzubüßen.

Der Zweck hinter dem seriellen DRAM-Controller besteht darin, insbesondere Servern die Skalierung auf viel höhere Speicherkapazitäten zu ermöglichen, indem DRAM über serielle Verbindungen mit viel geringeren Pin-Zahlen als bei herkömmlichen parallelen DDR-Schnittstellen angeschlossen werden kann. Hierbei kommt das von OpenCAPI (PDF) abgeleitete Open Memory Interface (OMI) zum Einsatz.

OpenCAPI ist einer von mehreren konkurrierenden Hochgeschwindigkeits-Verbindungsstandards, die über die Leistung und den Funktionsumfang von PCI Express hinausgehen möchten. Die ersten beiden OpenCAPI-Standards basieren auf PCIe 3.0 (8 GT/s) und 4.0 (16 GT/s). OpenCAPI 3.0 hat die PCIe-Grundlagen zugunsten einer neuen, schnelleren 25-GT/s-Verbindung aufgegeben. Das Open Memory Interface (OMI) ist ein Bestandteil von OpenCapi und bietet ein medienunabhängiges Protokoll mit geringen Latenzen beim Speicherzugriff.

Das Open Memory Interface nutzt bis zu acht Lanes mit je 25,6 Gigatransfers pro Sekunde (GT/s) , was eine Bruttodatenrate von 204,8 Gigabit pro Sekunde bedeutet. Das entspricht der Transferrate von DDR4-3200 mit 3,2 GT/s über 64 Leitungen, also rund 25,6 Gigabyte pro Sekunde.

OMI-DDIMM-Module mit DDR4-3200 und ECC-Fehlerkorrektur

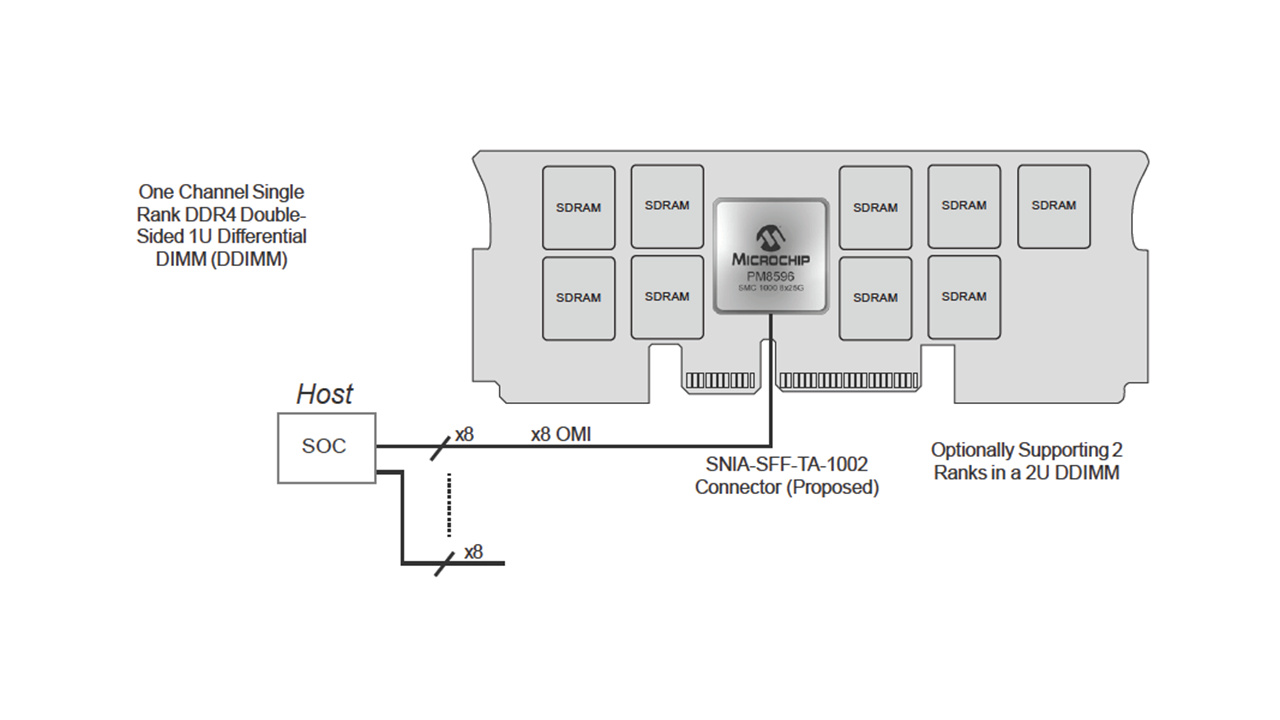

Um die Menge an RAM noch höher skalieren zu können, soll der SMC1000 8X25G DRAM-Controller mit kommenden OMI-DDIMMs (Differential Dual-Inline Memory Module) mit DDR4-3200-SDRAM und ECC-Fehlerkorrektur zusammenarbeiten. Die DDIMMs ermöglichen einen weitaus höheren RAM-Ausbau und stellen im Grunde einen Speicher-Controller mit ECC-Engine mit Anbindung an OpenCAPI 3.1 x8 dar.

DDIMMs sollen eine nur wenig größere Latenz beim Lesezugriff als LRDIMMs aufweisen. Microchip nennt in einem Whitepaper (PDF) 45,4 ns statt 41,5 ns. Zudem können DDIMMs auch als NVDIMM-N mit nichtflüchtigen Speicherchips ausgelegt werden.

DDIMM-Module von Samsung, SMART und Micron

Laut Microchip werden die ersten OMI-DDIMMs von Samsung, SMART Modular und Micron mit einer Kapazität von 16 Gigabyte bis 128 Gigabyte in einfacher Bauhöhe (1U DDIMM) und mit 256 Gigabyte in doppelter Bauhöhe (2U DDIMM) gefertigt. Die JEDEC sieht den DDIMM-Formfaktor für kommenden DDR5-SDRAM vor.

IBM will OMI bei Power-CPUs nutzen

Damit dies alles funktioniert, müssen Prozessoren das Open Memory Interface unterstützen. IBM hat angekündigt, OMI bei den Prozessoren der Power-Familie einzusetzen.

OMI Interface

- 1x8, 1x4 support

- OIF-28G-MR

- Up to 25.6 Gbps Link Rate

- Dynamic low power modes

DDR4 Memory Interface

- x72 bit DDR4-3200, 2933, or 2666 MT/s memory support

- Supports up to 4 ranks

- Supports up to 16 GBit memory devices

- 3D stacked memory support

Persistent Memory Support

- Support for NVDIMM-N module

Support for NVDIMM-N modules

- Intelligent Firmware

- Open Source Firmware

- On-board processor provides DDR/OMI initialization, and in-band temperature and error monitoring

- ChipLink GUI

Security and Data Protection

- Hardware root-of-trust, secure boot, and secure update

- Single symbol correction/double symbol detection ECC

- Memory scrub with auto correction on errors

Peripherals Support

- Support for SPI, I²C, GPIO, UART and JTAG/EJTAG

Small Package and Low-Power

- Power optimized

- 17 mm x 17 mm package

Microchip SMC 1000 8x25G – Spezifikationen

Im Podcast erinnern sich Frank, Steffen und Jan daran, wie im Jahr 1999 alles begann.