Für kleinere Zen-6-Epyc-CPUs: AMDs neuer Sockel SP8 besitzt 5.572 Kontaktflächen

AMDs nächste großen Zen-6-Epyc-Prozessoren der Familie Venice sitzen im neuen Sockel SP7. Darunter wird es wie üblich aber auch eine Nummer kleiner zugehen, der passende Sockel ist SP8. Die beiden neuen Sockel folgen dabei dem Muster der aktuell genutzten Sockel SP5 und SP6.

SP7 und SP8 ersetzen SP5 und SP6

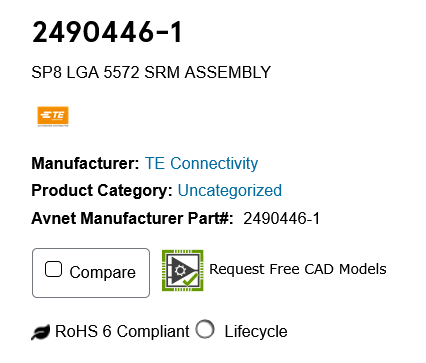

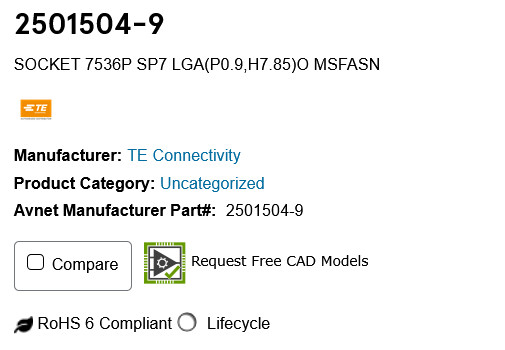

Mehrere Einträge bei verschiedenen Ausrüstern offenbaren AMDs neuen Sockel SP8, wie InstLatX64 entdeckt hat.

Dieser wird demnach 5.572 Kontaktflächen nutzen, klar weniger als der Sockel SP7 mit 7.536 Kontaktflächen. Beide zusammen ersetzen Sockel SP5 mit 6.096 Kontakten und Sockel SP6 mit 4.844 Auflageflächen im LGA-Format.

Mehr Bandbreite dank MRDIMM

Laut bisherigen Gerüchten wird nur der neue Sockel SP7 16 Speicherkanäle unterstützen, der für Workstation-Aufgaben (Stichwort Threadripper) gedachte kleinere Sockel SP8 wird bei 8 Kanälen bleiben – schon deshalb braucht es viel weniger Pins.

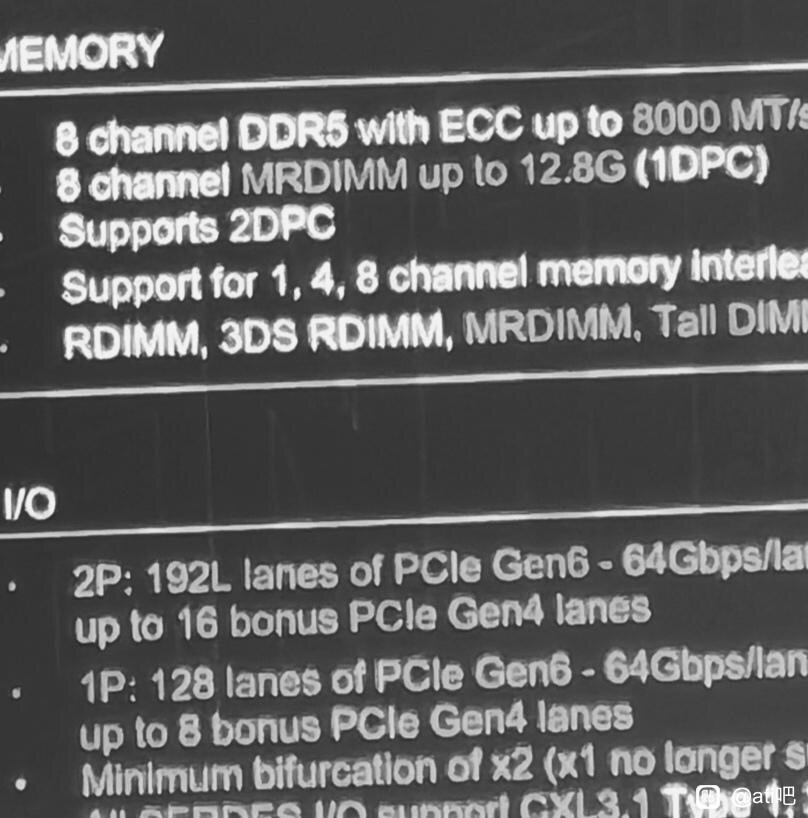

In beiden Fällen wird aber aller Voraussicht nach eine viel höhere Speichergeschwindigkeit von bis zu 12.800 MT/s bei Nutzung von MRDIMM umgesetzt. Gegenüber dem aktuell genutzten Standard von maximal DDR5-6400 entspricht dies im Sockel SP8 einer Verdoppelung der Bandbreite, im Sockel SP7 gegenüber dem Sockel SP5 kommt noch mehr Bandbreite hinzu, da 16 statt 12 Speicherkanäle verfügbar sind.

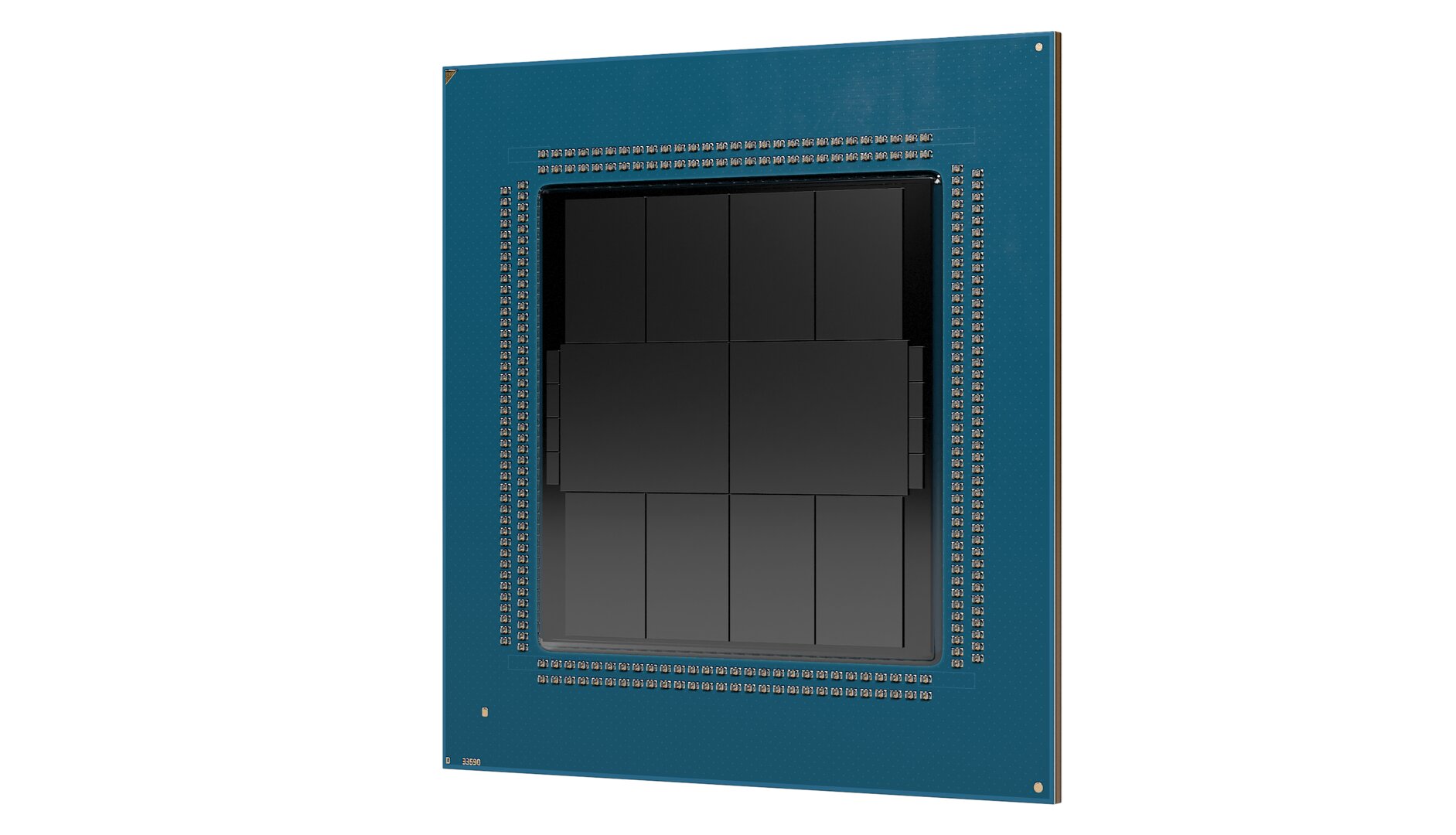

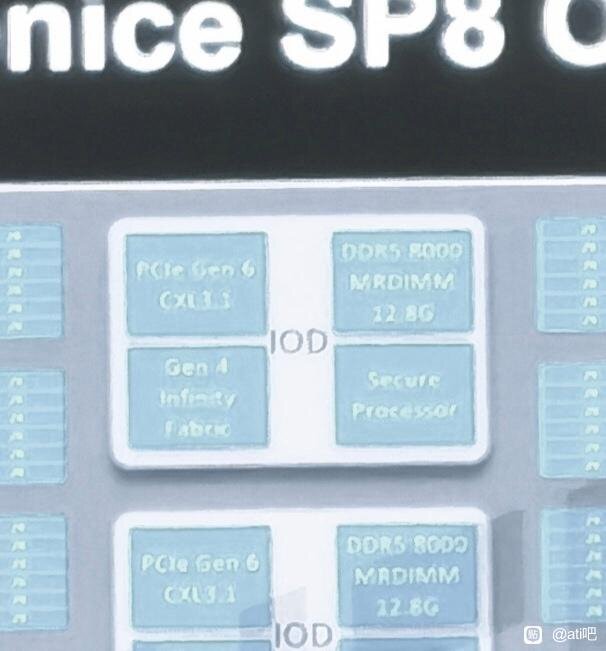

Auch im Sockel SP8 mit Dual-Die

Auch die Epyc/Threadripper-Prozessoren im Sockel SP8 sollen dabei auf das Dual-IO-Die-Design setzen, das AMD zu Beginn des Jahres erstmals auf der Bühne gezeigt hat.

Im Sockel SP8 bedeutet das gemäß Gerüchten ebenfalls sehr viele zur Verfügung stehende PCIe-Lanes und mehr. AMD hatte zuletzt auch PCIe 6.0 als Standard für die neuen Server-Prozessoren bestätigt, zuvor hatten Gerüchte das schon benannt.

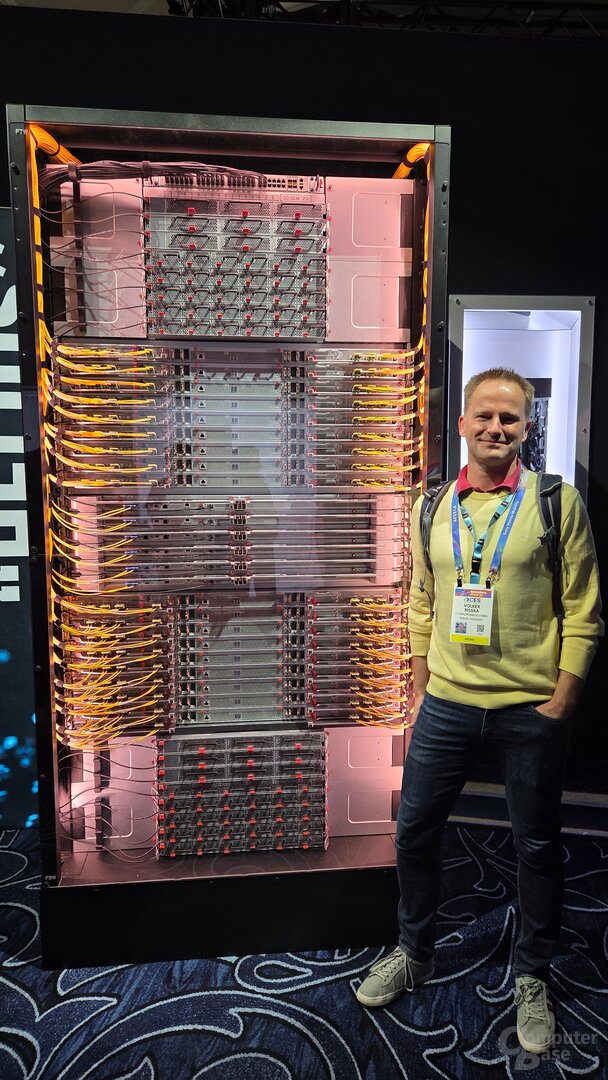

Traditionell sind die Gerüchte wenige Monate vor dem Start schon sehr genau, da viele dieser Chips bereits bei OEMs zur Qualifizierung im Einsatz sind. Erwartet wird die offizielle Vorstellung im Sommer dieses Jahres. Der Fokus liegt dann aber erst einmal auf den größten Venice-CPUs im Sockel SP7, um das AMD Helios Rack bestücken zu können, welches ab Q3/2026 ausgeliefert werden und AMD einen größeren Anteil am KI-Markt sichern soll.