Intel Sandy Bridge im Test: Fünf Modelle auf 54 Seiten untersucht

11/54Ein „Ring“ sie alle zu verbinden

Zum Abschluss der Architekturbetrachtungen kommt noch ein ganz wesentlicher Baustein zum Vorschein. Intel lässt sich gar dazu hinreißen zu behaupten, dass diese Neuerung uns viele kommende Jahr begleiten wird. Die Rede ist vom „Ring“.

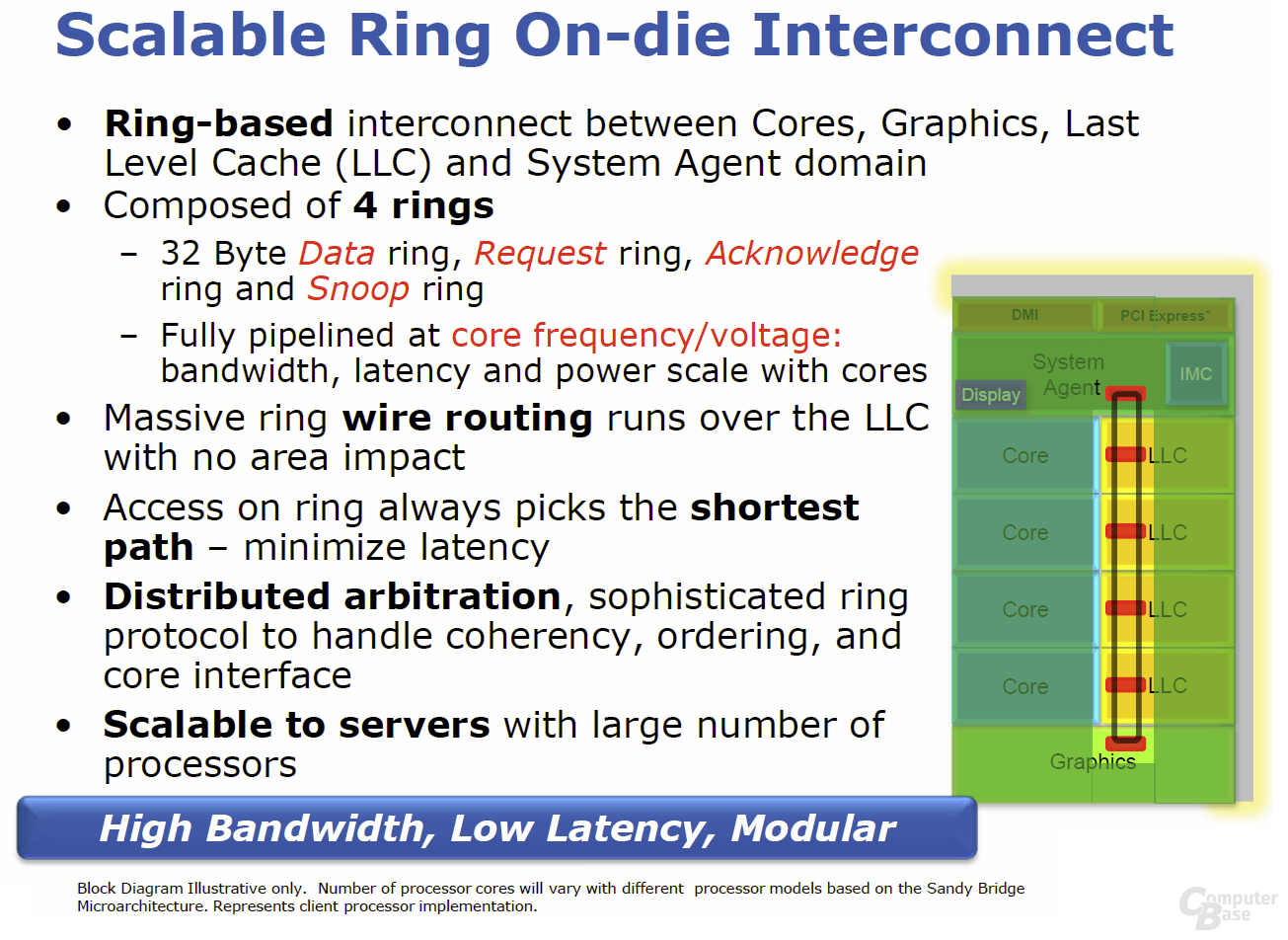

Ein „Ring“ sorgt im einfachsten Sinne schlichtweg für die Kommunikation aller wichtigen Elemente auf dem Die untereinander. Dies sind konkret die vier Kernkomponenten: Prozessorkerne, Grafikkern, Last Level Cache (LLC) sowie der System Agent, früher auch als „UnCore“ bezeichnet. Intel hat das Design dabei strikt modular ausgelegt, was es mit sehr geringem Aufwand möglich macht, beispielsweise den Grafikkern einfach noch ein Stück weiter „nach unten“ zu verschieben und zwei zusätzliche Kerne und weiteren LLC unterzubringen. Als weitere Möglichkeit kann man auch den Grafikkern ganz weglassen und dort weitere CPU-Kerne und Cache unterbringen – dies wird bei „Sandy Bridge E“ im Laufe des Jahres geschehen.

Technisch gesehen ist es nicht nur ein „Ring“, sondern derer gleich vier: Einer ist für Anfragen zuständig, ein weiterer übermittelt die Status-Meldungen, der dritte Ring lauscht (snoop) nach Veränderungen bei den Daten und der vierte Ring ist letztendlich für die Kommunikation der Daten selbst zuständig. Diese Ringe liegen in kürzester Distanz zu allen zu verbindenden Elementen, durchdringen sie aber nicht, was durch die schematische 2D-Darstellung nicht ersichtlich wird. Denn ein Prozessor ist 3-dimensional und so haben die Architekten die Verbindungsleitungen des Rings schlichtweg oberhalb (auf den Metall-Interconnect-Layern) der Kerne, Cache & Co. platziert.

Auch wenn die Bezeichnung „Ring“ einen Datentransfer immer im Kreis impliziert, ist dem nicht so. Kommt beispielsweise eine Anfrage des zweiten Prozessorkerns, geht dieser den kürzesten Weg zum Cache – direkt gerade durch (die rote Linie). Ist der zweite Cache-Bereich anderweitig belegt, sucht er sich den nächst liegenden – immer jedoch auf dem kürzesten Weg. Die langsamsten Verbindungen kommen logischerweise zustande, wenn CPU-Kern Nummer 4 etwas aus Cache-Box Nummer 1 haben möchte. Um dem entgegenzuwirken, hat Intel sowohl die Leistungen als auch die Bandbreite des Caches massiv gesteigert und gleichzeitig noch die Latenz von 36 Zyklen bei „Nehalem“ auf 26 bis 31 Zyklen – je nach „Wegstrecke“ – bei „Sandy Bridge“ verringert.

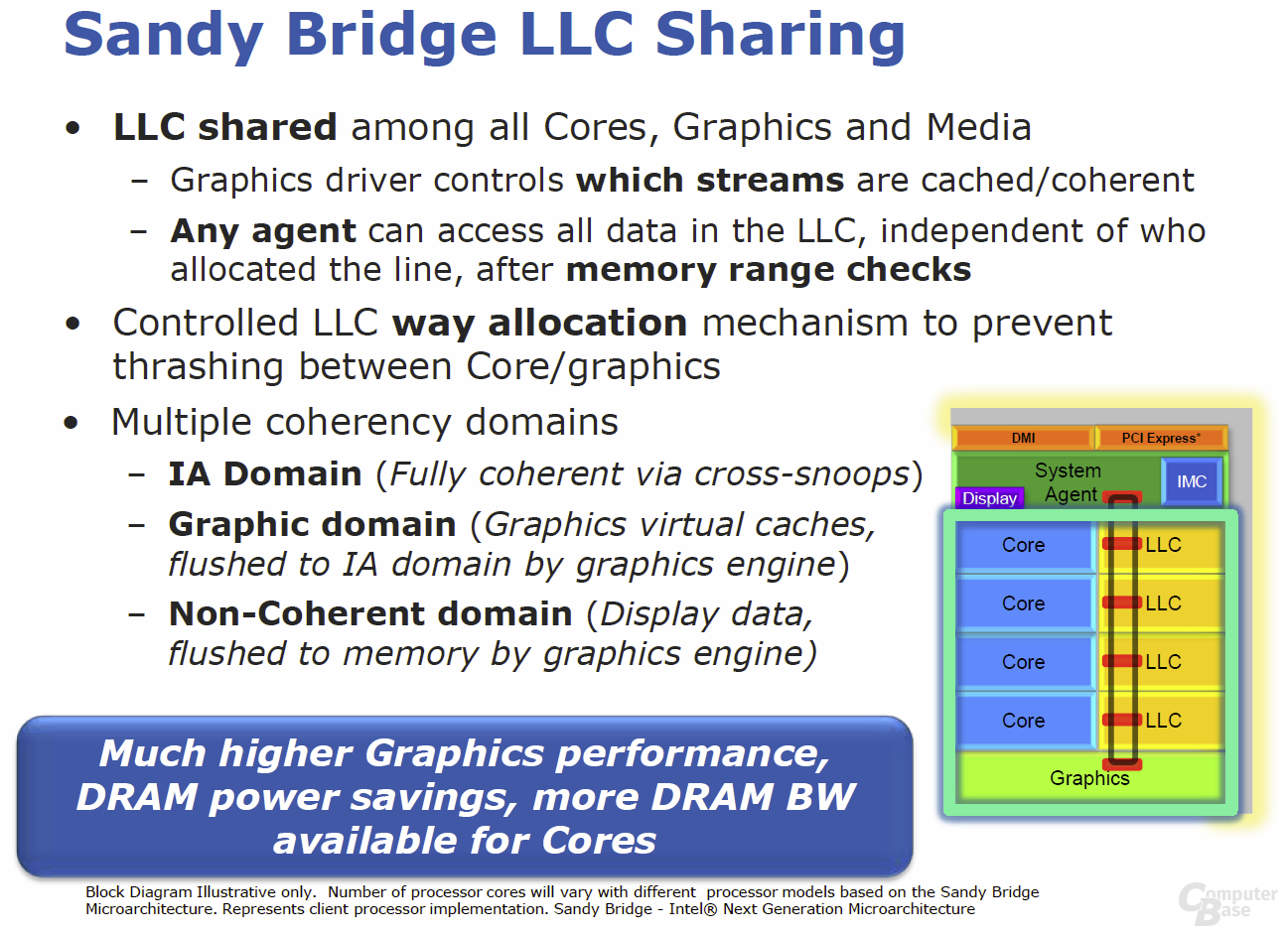

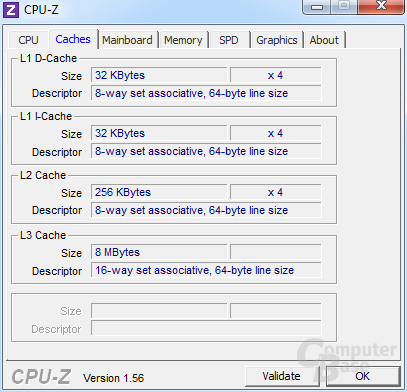

Der Last Level Cache (LLC), von Intel selbst noch oft genug als L3-Cache bezeichnet, wird damit zu einem elementar wichtigen Bauteil. Laut Intel liegt die „Hitrate“ bei Anfragen an den L3-Cache bei etwa 50 Prozent, was den weiten Weg zum Arbeitsspeicher erspart und eine hohe Performance bietet. Dies liegt auch an der vollständigen Skalierung. So arbeitet der L3-Cache fortan mit der gleichen Spannung und gleichen Taktfrequenz wie die Prozessorkerne, was den Cache bei schnelleren Prozessoren auch entsprechend schneller arbeiten lässt. Die Bandbreite eines 3 GHz schnellen Prozessors liegt dank 32 Bytes an Daten pro Taktzyklus und Kern bereits bei beachtlichen 96 GByte/s. Summiert man dies auf vier Kerne auf, sind es bereits 384 GByte/s, für das Flaggschiff Core i7-2600 mit 3,4 GHz bedeutet dies folglich eine gesamte Bandbreite von 435,2 GByte/s.

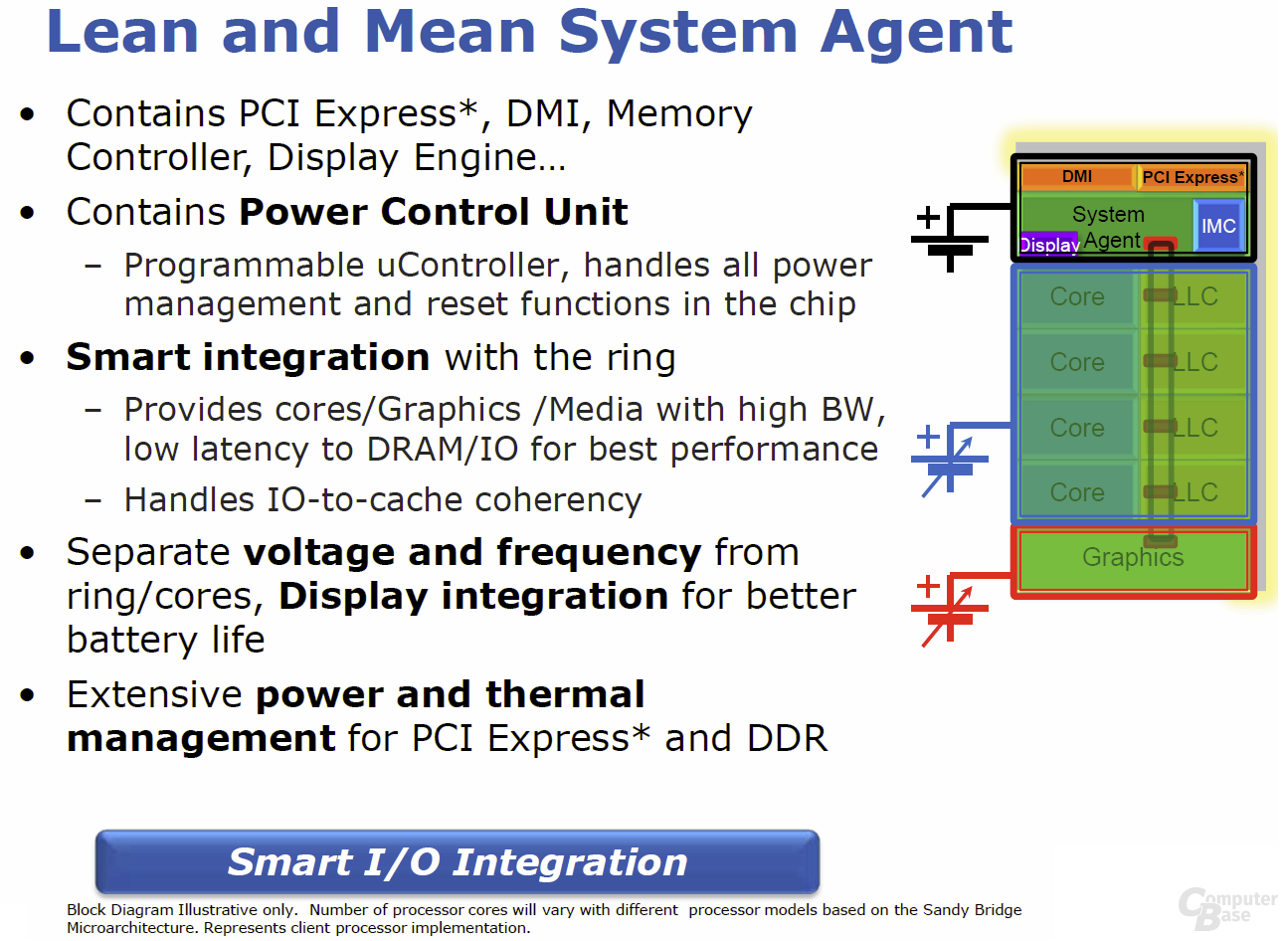

Das letzte Element, das am „Ring“ hängt, ist der „System Agent“. Erst dieser sorgt für die Kommunikation zur Außenwelt. Dafür bietet er nicht nur den integrierten Speichercontroller, sondern auch die PCI-Express-Lanes für die Grafikkarte, die FDI-Verbindung für die Ausgabe der integrierten Grafik und sorgt zu guter Letzt für die Kommunikation via Direct Media Interface (DMI) mit dem Platform Controller Hub (PCH), umgangssprachlich weiterhin Chipsatz genannt.

Der „System Agent“ – früher als Northbridge und UnCore-Bereich der CPU bekannt – wird das einzige Element im Prozessor sein, das immer eine feste Spannung zugeordnet bekommt. Deshalb hat Intel die Stromversorgung der gesamten CPU auch dreigeteilt. Während sie beim Prozessor/Cache und der Grafik jeweils variabel ist (damit auch der Turbo beziehungsweise die Schlafzustände funktionieren können), sind im System Agent jene Bauteile untergebracht, die sehr sensibel auf Takt- und Spannungsänderungen reagieren.

Auch in dem Bereich wurden teilweise massive Verbesserungen vorgenommen. Dies trifft unter anderem den integrierten Speichercontroller, der gegenüber den „Westmere“ nicht mehr teilweise mit der Grafikeinheit verbunden ist, sondern vollständig unabhängig agiert. Dadurch steigt die Bandbreite massiv an und hebt das Dual-Channel-Speicherinterface fast auf das Niveau des Triple-Channel-Interfaces der „Bloomfield“.