Fujitsu Sparc64 XIfx: 32+2-Kern-Prozessor für Supercomputer

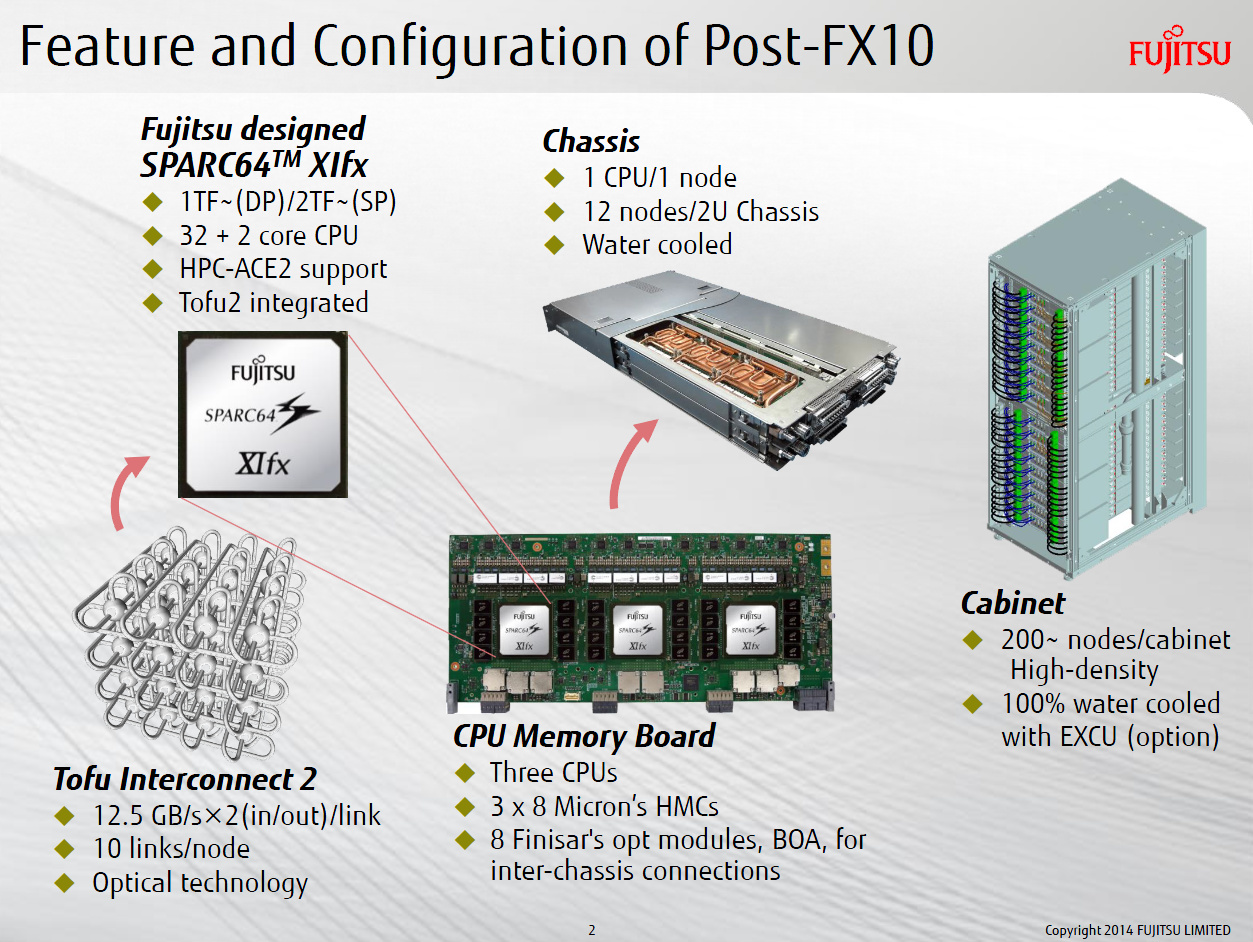

Im Rahmen des Symposiums „Hot Chips 26“ hat Fujitsu weitere Details zur Prozessorneuentwicklung Sparc64 XIfx für das HPC-Segment erläutert. Dieser setzt auf 32 zuzüglich zweier Assistenzkerne, hinzu kommt die Unterstützung eines neuen Interconnect-Systems und Microns Hybrid Memory Cube (HMC) als moderner Speicherstandard.

Der Sparc64 XIfx folgt auf den Sparc64 IXfx mit seinen bis dato 16 Kernen. Die 32 Kerne sind intern in zwei mal 16 Kerne aufgeteilt, die jeweils 12 MByte L2-Cache besitzen und diesen gemeinsam nutzen. Die Kerne in moderner Out-of-Order-Architektur wurden massiv überarbeitet, angefangen bei der Sprungvorhersage über nun 256 Bit breite SIMD-Einheiten bis hin zu schnellerem L1-Cache. Dank der angestrebten 20-nm-Fertigung konnte gleichzeitig der Takt von bisher maximal 1,848 auf rund 2,2 GHz gesteigert werden. Damit soll eine Leistung von maximal 1,1 TFLOPS erzielt werden, in passenden Server-Behausungen von maximal 96 Nodes und bis zu 1.024 Racks ergibt sich als großer HPC eine theoretisch mögliche Rechenleistung von 100 PetaFLOPs. Ein wichtiger Grund- und Meilenstein auf dem Weg zum Ziel aller großen HPC-Hersteller, bis zum Ende der Dekade die ExaFLOP-Marke zu durchbrechen.

Interessant ist jedoch nicht nur der Prozessor selbst, sondern auch die Speicheranbindung sowie Speicherart. Mit Hybrid Memory Cube kommt der neueste Standard zum Einsatz, die zwei Speichercontroller sollen 240 GByte/s an Daten bewegen können. Das Tofu 2 (PDF) getaufte neue Interconnect-System soll mehr als doppelt so schnell arbeiten wie der Vorgänger und 12,5 GByte/s an Daten transferieren können.

Der Sparc64 XIfx soll ab 2015 zur Verfügung stehen. Wer genau die CPU fertigt, ist derzeit nicht klar. Im Juli wurde bekannt, dass sich Fujitsu aus der Chip-Fertigung zurückziehen will. In der Übergangsphase soll ein Joint Venture mit UMC helfen, die Kosten von Fujitsu zu drücken. Da aber auch UMC in der Fertigung gerade bei 28 nm angekommen ist, bleibt abzuwarten, wer die 3,75 Milliarden Transistoren schwere CPU in 20 nm am Ende wirklich baut.