Patent: AMD plant mit GPUs im Chiplet-Design

Laut einem neuen Patent plant AMD zukünftig potenziell auch mit Grafikchips im modularen und bereits von den Prozessoren auf Basis der Zen-Mikroarchitektur bekannten Chiplet-Design. Ein solches Konzept auf GPUs angewandt sei allerdings komplex und teuer, so AMD.

AMD skizziert Chiplet-Design für GPUs

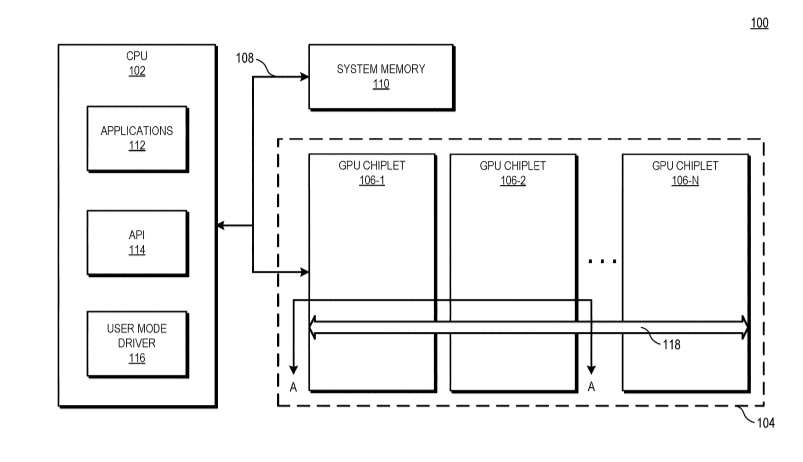

Wie die Website FreePatentsOnline berichtet, hat der Hersteller ein US-Patent unter dem Titel „GPU Chiplets using High Bandwidth Crosslink (PDF)“ und der Patentnummer „US 2020/0409859 A1“ beim „United States Patent and Trademark Office“, dem zuständigen Patentamt der Vereinigten Staaten eingereicht.

Im Patent selbst skizziert der Hersteller wie Grafikchips im Chiplet-Design zukünftig aussehen könnten und erklärt, weshalb dieser Ansatz bislang nicht stärker verfolgt und GPUs in einem monolitischen Zustand gehalten wurden.

Laut AMD sei das Design sehr komplex und kostspielig und zumindest zurzeit noch zu ineffizient, da es schwierig sei, die Parallelität auf mehrere Chips zu verteilen und Speicherinhalte entsprechend zu synchronisieren. Dieses Problem sollen Crosslinks mit hoher Bandbreite lösen.

GPU-Chiplet soll mit CPU kommunizieren

Laut AMD soll ein GPU-Chiplet direkt mit der CPU kommunizieren, während die anderen Chiplets über passive Crosslinks mit hoher Bandbreite untereinander kommunizieren und als System-on-a-Chip (SoC) auf einem entsprechenden Interposer angeordnet werden.

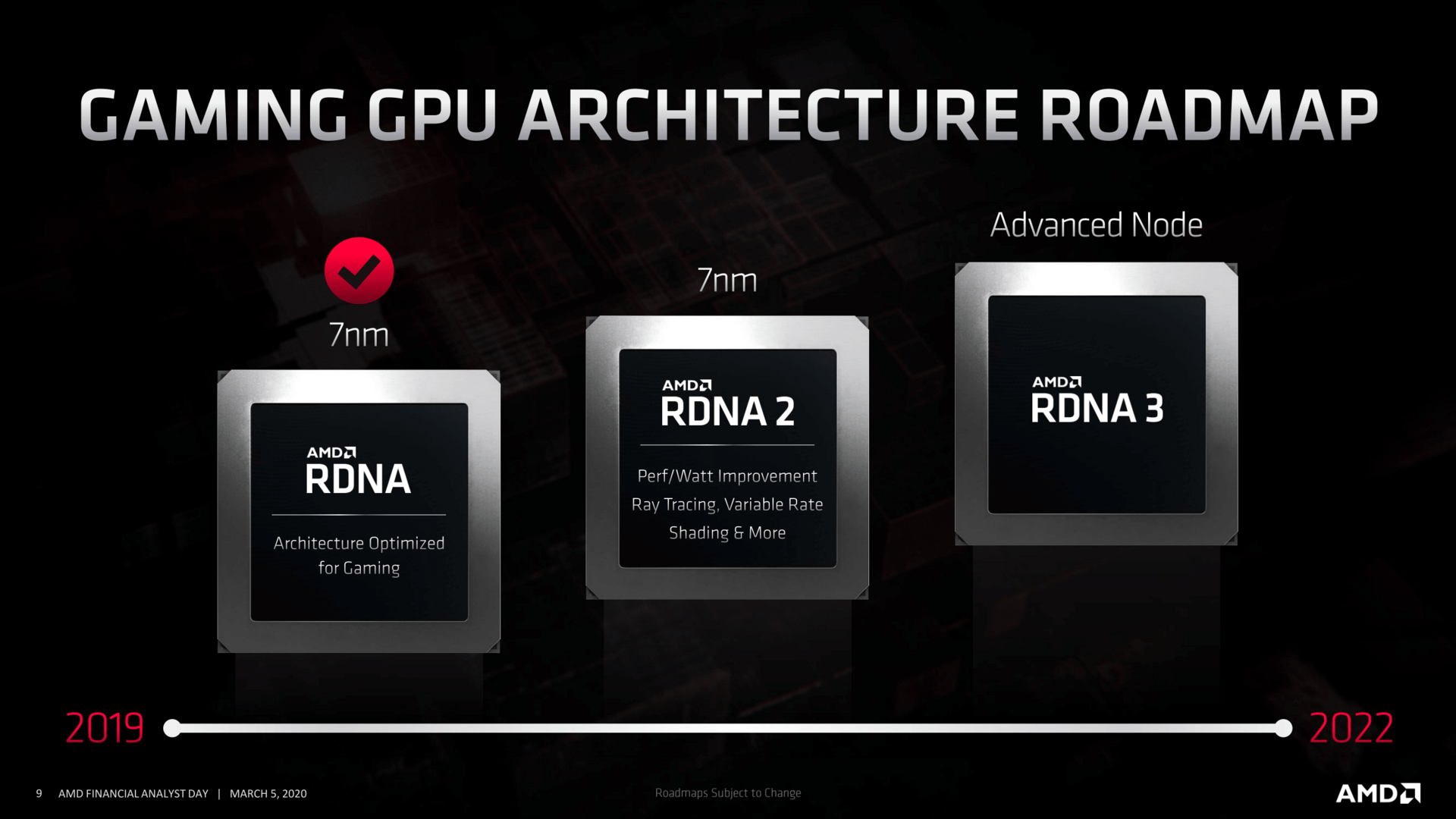

In der Vergangenheit wurden mehrfach Gerüchte laut, RDNA 3 oder RDNA 3+ könnten auf ein solches Chiplet-Design setzen, vermutlich aber eventuell eher ein Nachfolger der professionellen Lösung CDNA. Zen 4 und RDNA 3 sind aber noch Zukunftsmusik und sollen voraussichtlich Ende 2022 erscheinen.

AMD selbst hat sich bislang nicht offiziell zu einem Multi-Chip-Design kommender Gaming-GPUs der Radeon-Serie geäußert.

Die Redaktion dankt Community-Mitglied „Shakj“ für den Hinweis zu dieser Meldung.

Die Patentschrift in der näheren Analyse

Eine nähere Analyse der Patentschrift liefert weitere Details zur möglichen Umsetzung von GPU-Chiplets durch AMD.

So beschreibt der Hersteller, dass alle Chiplets Recheneinheiten à la CUs beinhalten werden, allerdings ein Chiplet als „Primary Chiplet“ die Kommunikation mit der CPU übernimmt. Dadurch wird der CPU weiterhin vorgegaukelt, mit einer monolithischen GPU zu arbeiten, wodurch die Notwendigkeit von Anpassungen an Anwendungen durch die Entwickler vermieden wird.

Notwendige Anpassungen an die Aufteilung der Rechenlast sollen hingegen vom Treiber und dem „Primary Chiplet“ übernommen werden.

Um Daten mit minimalen Einbußen zwischen den Chiplets zu verteilen, möchte AMD laut Patentschrift eine passive Schnittstelle namens HBX („High Bandwidth Crosslink“), die die L3-Caches aller Chiplets miteinander verbindet, nutzen. Dadurch können alle Chiplets sowohl auf die Daten im Cache als auch auf die VRAM-Anbindungen der anderen Chiplets zugreifen.

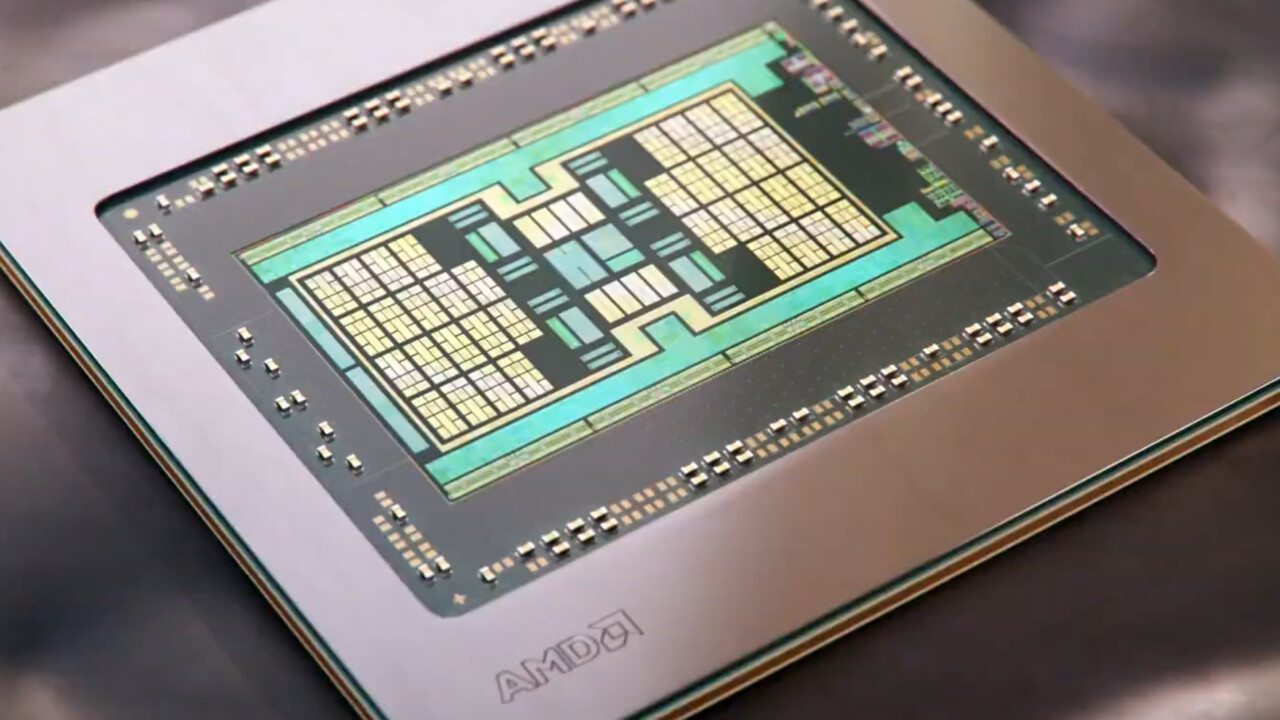

Den Darstellungen zufolge enthält ein Chiplet ähnlich wie bei RDNA 2 sowohl L2- als auch L3-Caches. Dies kann dahingehend interpretiert werden, dass die Chiplet-Technologie auch für Gaming-GPUs genutzt werden könnte, allerdings sind die Abbildungen zu ungenau, um dies mit Sicherheit zu sagen.

AMD erwähnt des Weiteren auch Aspekte, die schon von vorherigen GPUs und den CPUs auf Basis der Zen-Architektur bekannt sind, wie die Nutzung eines Interposers um die Chiplets zu verbinden.

Der Hersteller beschreibt dabei sowohl Lösungen, bei denen stets zwei Chiplets entlang einer Linie verbunden sind, als auch sternförmig angeordnete Netzwerke.