Syrato schrieb:

Wenn jemand nur LoL spielt, dann reichen 8 Kerne auch die nächsten Jahre.

Wenn jemand nur LoL spielt, hat man mit 8 Kernen ZU VIEL für die CPU bezahlt.

Bloß weil es vereinzelt Spiele gibt, die mit mehr als 8 Kernen etwas anfangen können, heißt das noch lange nicht, dass das allgemeingültig wird. Selbst für Spiele wie Anno 1800 muss man nicht gleich mit mehr als 8 Kernen, oder überhaupt 8 Kernen kommen. Ja, ich weiß, dass riesige fortgeschrittene Maps die CPU stark belasten, aber nicht jeder ist in dieser Blase gefangen, nur mit max. Details spielen zu müssen.

Mediendesigner schrieb:

so ein quatsch, selbst cs2 profitiert von mehr kernen aber ob es reicht ist ja eh ansichtssache.

Stimmt, CS2 kann von mehr als 2 Kernen durchaus profitieren. Du darfst gerne Benchmarks posten, mir fällt es schwer in der Hinsicht vernünftige Daten zu finden.

Was durchaus passieren kann, ist der Irrtum z.B. eine Mehrleistung zwischen einem 7700X und einem 7950X als Vorteil durch die zusätzlichen Kerne zu werten, während es dann eher an der höheren Taktfrequenz durch das bessere Binning resultiert. (Zumindest für Spiele, die stark vom Takt profitieren)

Dedenne1987 schrieb:

Das könnte Ende 27 anders aussehen. Ich denke mindestens MS haut da eine neue Konsole raus. Und ich denke „nur“ 8 Kerne wird das Teil nicht haben.

Nach den ganzen Verschiebungen unterschiedlichster Hardware wegen der RAMpocalypse würde es mich überraschen, eine neue Xbox Konsole schon Ende 27 kommen würde, selbst wenn sich die Lage in 2027H2 einigermaßen stabilisiert.

Aber egal, wann es herauskommt, wenn diese Konsole mehr als 8 Kerne beinhaltet, wird das eine geringe Rolle spielen, sollte diese Konsole laut den Gerüchten vielmehr ein PC als eine reine Konsole darstellen und dann folgen die Regeln für PC-Spieleentwicklung. In dieser Hinsicht geht Valve den intelligenteren Weg. Ihre Steam Machine ist kein Leistungsknaller, aber diese bietet ausreichend Leistung für jene, die sich keine Gedanken um das ganze PC-Drumherum machen, aber einfach Spiele genießen möchten und nicht zu viel dafür zahlen wollen (gut, der letzte Punkt ist gerade problematisch, aber Microslop wird davon auch nächstes Jahr (falls nächstes Jahr) betroffen sein, aufgrund der stärkeren Hardware wahrscheinlich noch stärker).

Im Vergleich dazu gehe ich jede Wette ein, dass die PS6 niemals mehr als 8 Kerne haben wird. Wozu auch? Die jetzige kann nur 6 der 8 Kerne für Spiele einsetzen, der Rest ist für das OS. Viel intelligenter wäre es, wenn 2-4 LPE-Kerne (je nachdem, ob SMT ja oder nein) auf den Chip kommen, welche sich um das OS kümmern. Ein getrennter RAM für das OS gibt es ja schon seit der PS4 Pro für die Pro Modelle, eigene LPE-Kerne sind nur der logische nächste Schritt.

Ripcord schrieb:

Läuft das OS dann allgemein stets nur auf einem einzigen Kern?

Sollten sogar zwei sein, was immens klingt.

scryed schrieb:

Am PC will ein größeres os mit betrieben werden hinzu kommen diverse Programme im Hintergrund ... Auch gibt es Leute die streamen oder ihre Sachen aufzeichnen

Und wo ist das Problem mit 8C-CPUs? Scheduling gibt es nicht umsonst und CPUs werden gerade bei Spielen nicht komplett in Anspruch genommen. Man muss die Spiele selbst heute suchen, die 8 Kerne so stark beanspruchen, dass andere Dinge davon negativ beeinflusst werden.

Diese Sache mit dem größeren OS ist übrigens irrelevant. Es ging nie darum, wie groß das OS ist, sondern wie es mit den Ressourcen umgeht und für Programme alles einteilt. Es spielt auch eine Rolle, wie sicher man sein System haben will/muss

Und zuletzt zum Streamen/Aufzeichnen, ich weiß ja nicht, ob du eine gewisse Ahnung davon hast, aber sofern man keine Benchmarks aufzeichnen will, wird man IMMER auf 60 fps limitieren, oder hast du auf irgendwelchen Streaming-Seiten mehr als 60 Hz Videos gesehen? Für das eigene Spielgefühl wird man vielleicht auf 60er Vielfachen limitieren (also 120, 180, 240 Hz) und schauen, dass es keine großen Ausreißer gibt, aber über diesen Punkt weiß ich nichts direkt.

scryed schrieb:

Mehr Kerne kann dazu führen daß die CPU Kühler bleibt

Das ist eine viel zu stark vereinfachte Darstellung. Ein einzelner Faktor bestimmt das Gesamtergebnis nicht so stark, wie du es hier darstellen willst.

Es stimmt ja so weit, dass mehr Kerne weniger hoch takten müssen, daher deren Vcore niedriger ausfällt und somit weniger Abwärme produzieren. Gilt ja auch für Anwendungen wie Spielen, wo die Auslastung niedriger ist, aber durch das Scheduling die Last zwischen Kernen springt, damit keine hohen Hotspots entstehen.

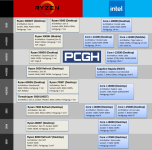

Was du jedoch ignorierst, dass es letzten Endes immer davon abhängt, wie diese CPU designt ist, auf welchen Verbrauch/TDP ist es eingestellt? Es bringt für die Kühlung rein gar nichts, wenn man die CPU mit durchgehend 250 W grillt. Ob mit 16 oder 32 Kernen, es bleiben 250 W. Bei leicht niedrigeren Lasten kann man wieder mit Hotspots argumentieren, aber hier spielt auch die Architektur eine große Rolle. Man sehe sich nur Intels Core-Aufteilung seit Arrow Lake an. Zwischen den P-Cores liegen die E-Cores, damit sich die stärkere Abwärme der ersteren nicht zu sehr sammelt.

Wenn du lieber doppelt so viele Kerne haben möchtest, damit die Last ständig umverteilt wird und somit weniger Hotspots entstehen, ist das ja schön und gut, ist aber wiederum nur ein Thema für jene Enthusiasten, die keine Kompromisse eingehen wollen und das empfinde ich persönlich so langweilig.

Cr4y schrieb:

Ich glaube, dass LPE-Cores im Desktop überflüssig sind.

Das kann man ja so sehen, aber es sollte dennoch nicht egal sein, ob ein Gesamtsystem 20, 60 oder gar 100 W verbraucht. Das Vorhandensein von LPE-Cores wird diesen Unterschied zwar nicht begünstigen, aber auch LPE-Cores sind ein Teil des Ganzen.

Viel schwerwiegender ist ein anderer Punkt. Wieso sollten sie die LPE-Cores entfernen, wenn sie so einen CPU-Tile auch für mobile Geräte anbieten wollen und das kann ja auch für den größten Tile zählen und dort sind LPE-Cores durchaus relevant. Dann müsste Intel einen separaten Desktop-Tile entwickeln. Ob das so Sinn ergibt, muss so oder so Intel zeigen.

Nighteye schrieb:

Meine Partnerin zockt auch noch im gleichen Raum wie ich. Sind dann 200W Menschen.

Auch hier kommen mehr Faktoren zusammen, als nur die Abwärme von Geräten und Lebewesen. Ich weiß ja nicht, wie eure Wohnung ist, aber je nach Lage (Süd - Nord, Dachgeschosswohnung) und Architektur/Bau (Altbau oder abgedichtet) habt ihr vielleicht einfach Glück und die richtigen Bedingungen. Schon das Lüften (eh kloar!) kann diese von dir genannten Faktoren mehr als ausgleichen, wenn die Bedingungen draußen passen.

Nighteye schrieb:

Schon mein Staubsauger verbraucht 700W.

Und? Gibt der 700 W Abwärme von sich? Ich glaube nicht Tim.

Nighteye schrieb:

Noch klarer kann man die Abkehr von Royal Core (Also P + E + Low Power) Kernen nicht machen.

Gar nichts ist klar. Ich weiß ja nicht, was sich Tan mit diesen Worten eigentlich gedacht hat, aber egal wie man zu der jetzigen Architektur steht, man redet NICHT die jetzigen und erst recht kommende Produkte im Vorfeld schlecht. Die müssen auch Nova Lake gut verkaufen wollen. Ich weiß auch nicht, wo sein Problem ist. Das Fehlen von HT ist primär im Server-Segment ein Problem, aber Panther Lake wurde positiv aufgenommen. Hat sich jemand über fehlendes HT beschwert?

Arrow Lake auf dem Desktop ist nicht populär, aber das liegt vorwiegend an der schlechten Spieleleistung. Anwendungen laufen darauf ganz ordentlich, trotz fehlendem HT und das ist für Spiele auch nicht gerade förderlich. Apple (oder auch Qualcomm) braucht auch kein SMT/HT, um Leistung zu liefern. AMD Ansatz passt, weil ihr SMT gut funktioniert und sie diese Architektur auch für Server kombiniert verwenden können. Wenn Intel wegen Servern HT wiederbringt, ist das ja schön und gut, aber dann sollte man damit erst herausrücken, wenn Nova Lake langsam weniger relevant wird und nicht, wenn wir noch nicht mal wissen, wie diese Architektur aussehen wird!

Und noch weniger bedeutet das, dass man sich von der hierarchischen Aufteilung verabschiedet.